文章目录

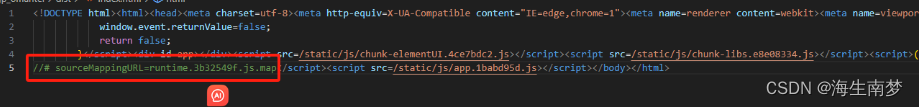

这个错误通常是由于尝试在非寄存器类型的对象上进行过程赋值所引起的。在 Verilog 中,当使用 always 块时,其中的赋值操作应该只用于寄存器类型的变量,比如 reg 类型。非寄存器类型的信号(比如 wire)不能在 always 块内进行赋值。

出现这个错误的原因可能是在非寄存器类型的信号上尝试进行赋值操作。在您的代码中,如果 output_data 是一个 wire 类型的信号,而您尝试在 always 块内给它赋值,这将导致这个错误。

解决这个问题的方法是将 output_data 声明为 reg 类型,而不是 wire 类型。修改代码如下:

module Data_Selector(

input [3:0] data0, // 输入数据0

input [3:0] data1, // 输入数据1

input sel, // 选择信号

output reg [3:0] output_data // 输出数据(改为 reg 类型)

);

always @(*) begin

// 使用条件运算符根据选择信号sel选择数据

output_data = (sel == 1'b0) ? data0 : data1;

end

endmodule

通过将 output_data 的声明从 wire 改为 reg 类型,您可以在 always 块内对其进行赋值,从而避免这个错误。

![Verilog刷题[hdlbits] :Module cseladd](https://img-blog.csdnimg.cn/03ba5258302c457b9110b24128b120de.png)