目录

1. Flash Memory中存储的信息

2. Flash操作

2.1 Read操作

2.2 Program操作

2.3 Erase操作

3 电压阈值分布

4 Block Erase

4.1 Pre-Program Phase

4.2 Erase Phase

4.3 Recovery Phase

5 Erase 中断

6 注意要点

这是之前搞Flash IP时的一个学习笔记,有点记不清楚出处是在哪里了,分享给大家关于Nor Flash的理解

NOR Flash的一个基本原理是必须先将其擦除,然后才能对其进行编程。另一个重要特征是擦除操作必须同时(批量)发生在整个内存块上,而不是按字节逐字节的方式依次发生。

所以,Erase操作包含了三个步骤:Pre-Program,Erase,Recovery。了解这个三个步骤中硬件原理是提升系统鲁棒性的重要因素。

1. Flash Memory中存储的信息

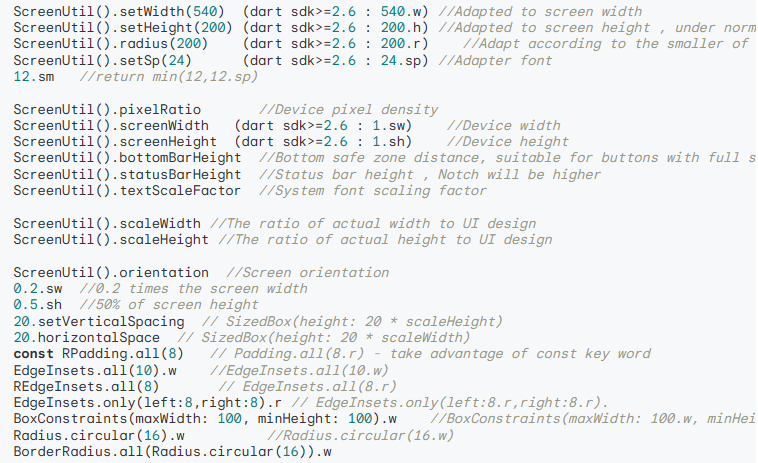

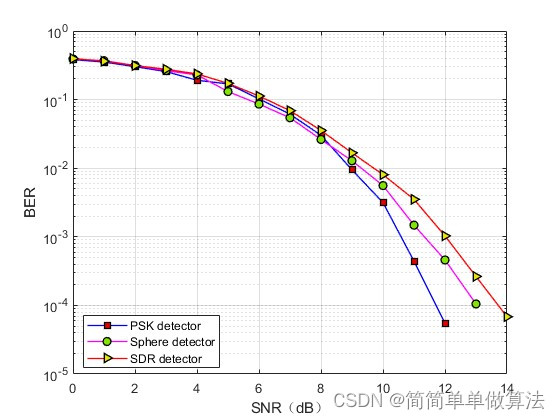

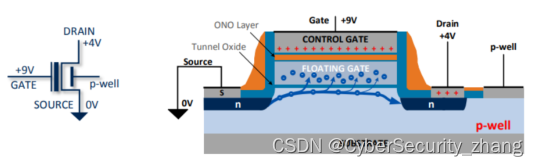

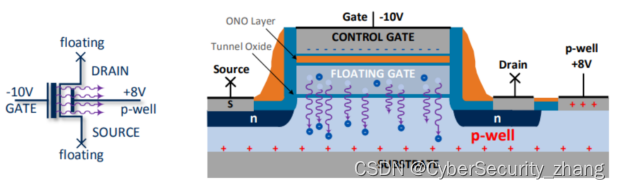

存储器的基本存储元件(单元)是由带“浮栅”的MOSFET组成的。困在存储单元浮栅内的电荷量决定了存储单元是否被编程或被擦除,浮栅中可以存储电荷,从而改变该单元的控制栅极(Control Gate)开关阈值电平Vth,当浮栅中没有电荷时(Erased)表示为“1”, 当浮栅中存有负电荷/电子时(Programmed)表示为“0”。如下图所示:

Source:源级

Tunnel Oxide:隧道氧化层

Control Gate:控制栅

Floating Gate:浮栅

Drain:漏极

P-well:P型衬底;每个p-well都有自己的电极,允许它在存储控制器的控制下,以特定的电压进行偏置。

Substrate:硅制造要求所有的存储单元都建立在一个共同的基础

擦除、读取、编程等操作后续具体讲。

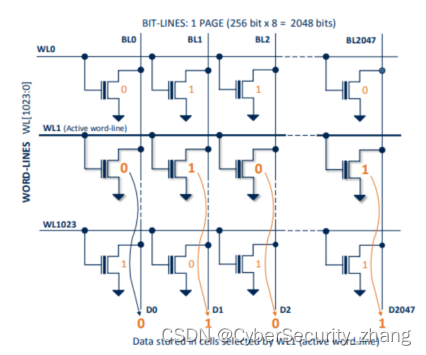

为了存储大量的信息,Flash Memory由memory cell按照N行M列来组成,每个行列交叉点都是一个cell,存储一个bit数据。因此一个flash的容量就为N*M bit。为便于记忆,我们把行叫做Word-line(WL),列叫做Bit-Line(BL)如下所示:

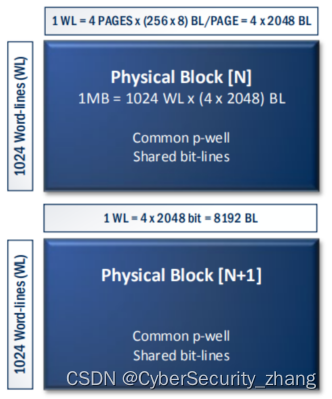

从上图看到,漏极通过bitline连接在一起,WL连接到控制栅;PAGE是一个WL中所有BL的集合,通常一个WL可以包含一个或者多个page。

重要的一点是,在每个physical block中,p-well和BL是共享的。

更进一步的,每个物理block可以分为更小的逻辑sector,方便管理。

2. Flash操作

对于Nor Flash来说,在写block之前必须擦除,并且擦除操作还要包括对已擦出的cell进行预编程。

2.1 Read操作

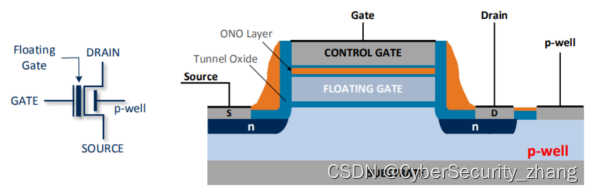

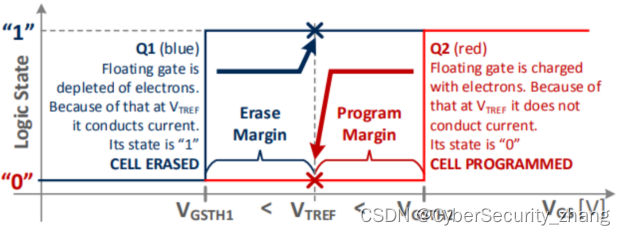

要确定单元格的状态(是已编程还是已擦除),必须读取单元格的内容,这是通过在MOSFET的栅极上施加大约5.5 V的参考电压来完成的。

如上图:Q1状态是已擦除,浮栅里被捕获电子耗尽了,由于其GATE-SOURCE阈值电压比VTREF小(VGSTH1<VTREF)。当确定该单元的状态时,对GATE施加一个5.5V的电压,这种情况下,MOSFET传导电流,因此处于逻辑“1”。

如上图:Q1状态是已编程,浮栅里充满了被捕获电子,由于其GATE-SOURCE阈值电压比VTREF大(VGSTH2>VTREF)。当确定该单元的状态时,对GATE施加一个5.5V的电压,这种情况下,MOSFET不传导电流,因此处于逻辑“0”。

通常情况下,浮栅不带电荷,则场效应管处于不导通状态,场效应管的漏极电平为高,则表示数据1。

编程时,场效应管的漏极和选择栅都加上较高的编程电压,源极则接地。这样大量电子从源极流向漏极,形成相当大的电流,产生大量热电子,并从衬底的二氧化硅层俘获电子,由于电子的密度大,有的电子就到达了衬底与浮栅之间的二氧化硅层,这时由于选择栅加有高电压,在电场作用下,这些电子又通过二氧化硅层到达浮栅,并在浮栅上形成电子团。浮栅上的电子团即使在掉电的情况下,仍然会存留在浮栅上,所以信息能够长期保存(通常来说,这个时间可达10年)。由于浮栅为负,所以选择栅为正,在存储器电路中,源极接地,所以相当于场效应管导通,漏极电平为低,即数据0被写入。由于热电子的速度快,所以编程时间短,并且数据保存的效果好,但是耗电量比较大。

擦除时,源极加上较高的编程电压,选择栅接地,漏极开路。根据隧道效应和量子力学的原理,浮栅上的电子将穿过势垒到达源极,浮栅上没有电子后,就意味着信息被擦除了。

2.2 Program操作

编程操作是基于称为“热电子注入”的物理过程。GATE与大电压相连(通常为+9V),同时漏极正偏压到约+ 4v,导致电子流从源极流向漏极。由于应用于GATE的强正电场,一些电子被“拉进”浮栅。一旦进入,这些电子就不再拥有逃离浮门限制所需的能量,它们仍然被困住:Cell被编程了。

为了将一个单元置于编程状态,所需要的阈值电压至少要大于5.5V,最好6.5V.。

2.3 Erase操作

擦除操作是基于Fowler-Nordheim Tunneling隧穿。

首先往p-well添加正电压(约+8V),用于吸引浮栅中被困电压;同时,在选择栅施加负电压(-10V),用于排斥电子,因此源极和漏极断开。

这两种电压叠加并产生一个大的电场,使电子能够隧穿氧化层。通过这个过程,浮栅耗尽了电子,降低了它们的阈值电压。如果观察单个细胞水平(通常在nA范围内),电流是微小的。由于电流非常小,电场必须维持很长时间才能提取足够数量的电子,这使得Erase操作相对缓慢

3 电压阈值分布

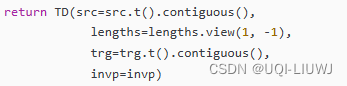

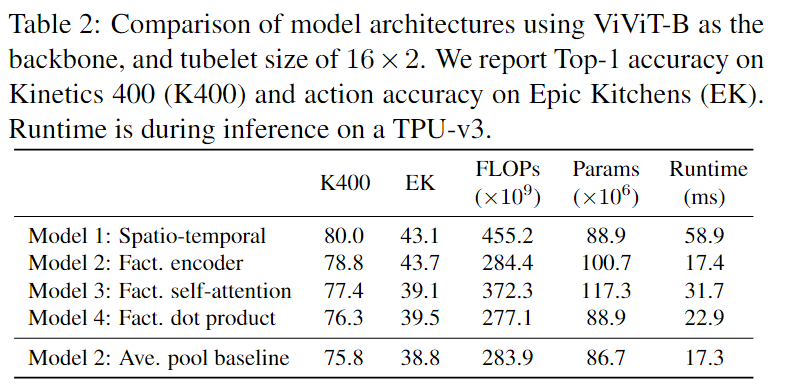

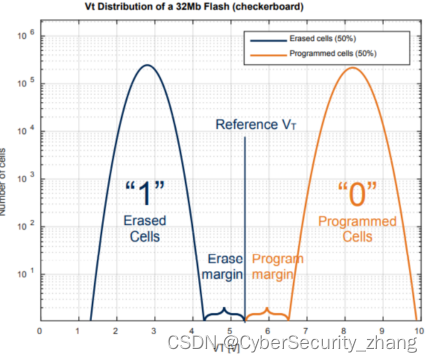

VT是电池中MOSFET在特定水平(通常为10 uA)上传导电流所需的阈值电压。它与浮栅中被困的电荷量有关。含有大量被捕获电子的Cell(程序Cell)具有较高的VT,通常为6.5 V或更高。耗尽电子的cell(擦除cell)具有较低的VT,通常为4v或更低。

在擦除和编程之间的VT范围的中间通常被用作参考阈值电压(VTREF),以确定特定的一组单元是否被编程或擦除。该电压用于被选择的WL(Word-Line),根据每个cell的浮栅状态以及被解码/选择的位行,模拟信号输出到shared WL。当WL电压从低电压依次增加到高电压时,y轴记录了从擦除状态切换到编程状态的单元数。

4 Block Erase

在NOR Flash的生命周期内,设备会被多次擦除和编程。在这个过程中,由于单个单元的状态从被编程变为被擦除,VT分布发生了变化,反之亦然。为了保持良好的VT分布和良好的边距,Erase操作分三个不同的阶段完成:

- Pre-Program Phase

- Erase Phase

- Recovery Phase

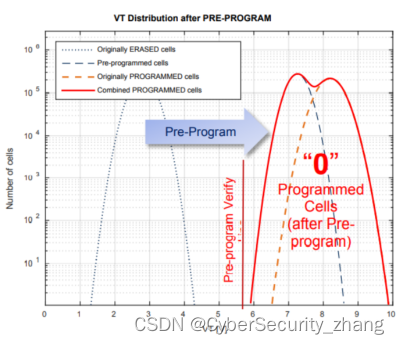

4.1 Pre-Program Phase

预编程的目的是为了让擦除操作工作在一个理想环境下。理论上讲,Erase操作同时影响所有cell,两个驼峰(橙色和蓝色曲线)都会向左移动。已经被擦除的cell位于负的VT区域,这在物理上是不可能的,因此,这些单元在VT接近0v时变得过度擦除,即使它们的栅极电压设置为0v时也会漏电流。

因此,通过预编程,所有cell都处于编程状态,这样可避免过擦出现,如下:

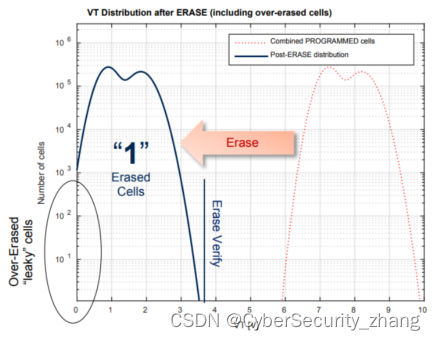

4.2 Erase Phase

Block Erase与Erase操作相同,不过是同时发生在完整的Logica块中;

一个巨大的电场——施加在物理块的公共p-well上的正电压(+8 V),以及施加在被擦除的逻辑块内的所有WL上的负电压(-10 V)——使电子“隧穿”通过potential barrier。浮栅损耗越来越大,VT电压降低。

在此过程中,一些cell可以移动到过度擦除的区域附近。如上所述,这种cell可以导电,即使当WL不活跃,其VT设置为接近0v。因为它是批量执行的,而且Erase操作必须持续到最慢的cell验证为止,因此Erase操作可能会导致较大的分布。

4.3 Recovery Phase

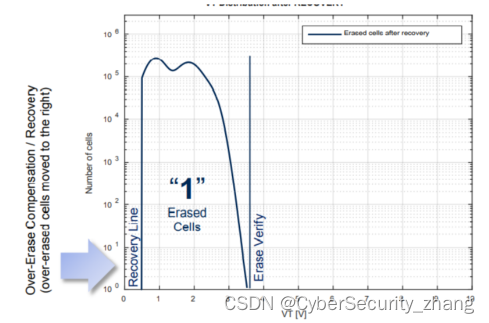

过度擦除的Cell被系统地软编程(以字节为基础),直到它们的VT足向右移动,以便它从左边越过恢复线。

当内部算法正在进行时,Flash集成控制器保持一个用户可读的状态位断言(状态寄存器中的BUSY/READY位)。

5 Erase 中断

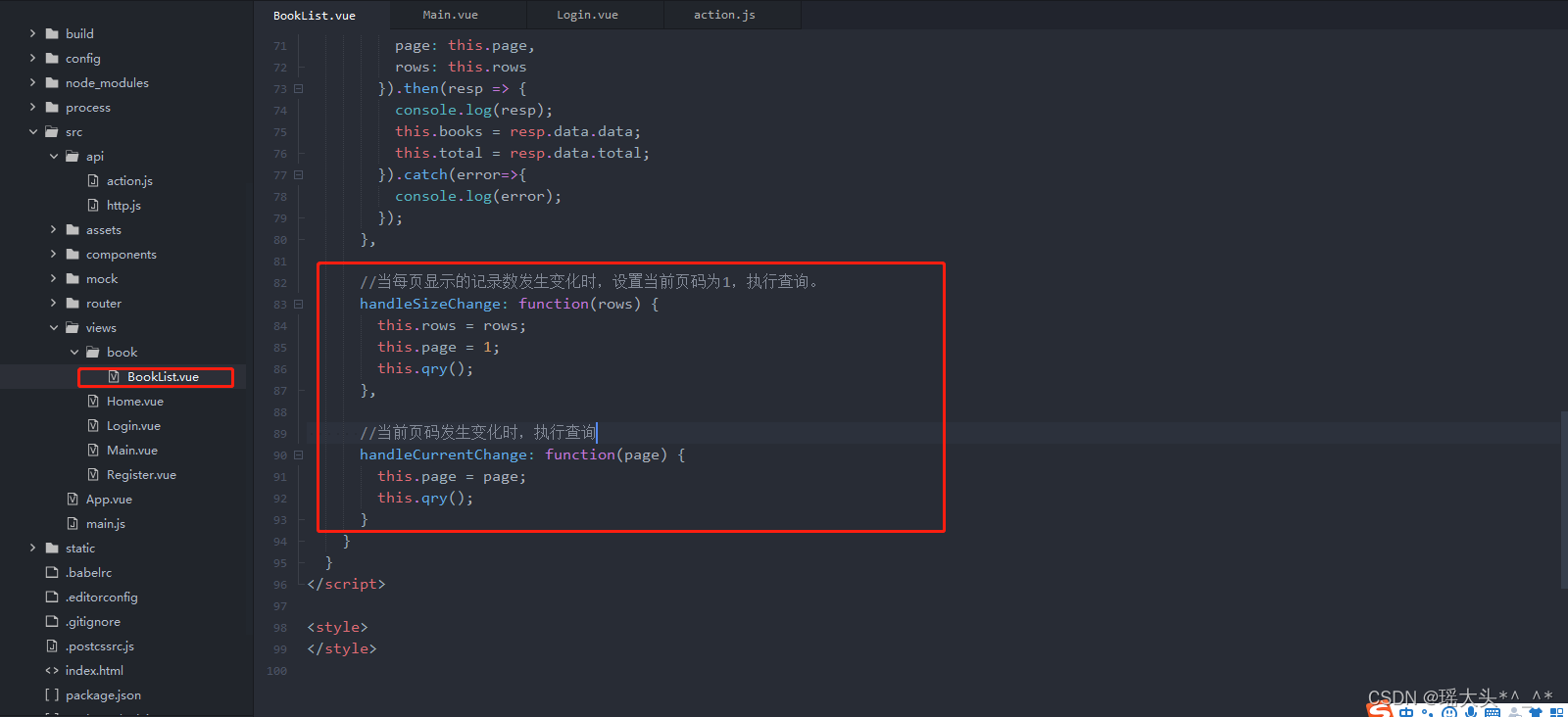

如果擦除操作被设备重启或者电源关闭打断,此时擦除操作的三个阶段还没完成,会导致memory进入到一个undefined状态:可以是擦除三个阶段的任意状态,因此读取的数据不可信。

如果Erase进程中断,内存设备可以通过几种不同的机制返回错误数据:

- 如果擦除中断是由软硬件复位、电源供电不足造成的,memory控制器会重启,并且会重置擦除操作。具体如下表所示

| 阶段 | 状态 | 影响 | |

| Pre-program | 部分cell被编程,部分擦除 | Block数据无意义 | |

| Erase | 部分被编程、部分擦除、部分过擦 | 显示全部擦除,但某些bit处于过擦状态,擦除不完全状态 | |

| Recovery | 部分被擦出、部分过擦 | ||

过擦的bit,导致共享BL上的泄漏,从而导致共享同一物理BL上的所有其他位的编程裕度降低。

上图展示了如果共享Bit Line上有一个泄露的cell,那么未选定WL上的“leaky cell”如何影响选定WL上“0单元格”的读取。当前选中WL[241],读取BL[1082]数据,但此时WL[65]BL[1082]处于过渡擦除状态;当泄漏量(漏电流)足够高时,所选单元中存储的“0”可能被错误读取为“1”。

如果是由于Erase Suspend指令中断Erase操作,上述副作用同样会发生,区别在于,当前设备中的SUSPEND bit会置1,用户可用于追踪,通过考虑状态位的状态,如果采取适当的预防措施,可以确保操作的成功完成。虽然过度擦除不太可能损坏同一物理块中的数据,但最好不要在挂起期间将要编程或读取的数据映射到同一物理块中。

6 注意要点

- 在发出软复位或硬复位和/或回收电源之前,始终检查BUSY/READY状态位是否有任何正在进行的操作。如果不这样做,可能会使内存处于未定义的状态,从而导致数据损坏;

- 当确实需要中断擦除操作,使用Suspend 指令,并将重要的系统级代码(在进行EraseSuspend操作时需要读取的代码)保存在单独的物理块中,远离用于数据记录的内存或经常被擦除更改的memory;

- 处理可能发生异步擦除中断的系统的另一种方法是,在逻辑块的开头编写一个唯一的字节值(“签名”),作为每次成功擦除操作的最后一步。如果由于计划外的电源中断或擦除操作过程中的小故障导致系统崩溃,作为崩溃恢复的一部分,将读取逻辑块的签名,并与已知的正确值进行比较。一个特定块的差异表明擦除操作没有正确完成,需要重复擦除,以恢复其正确的分布。