HDL

硬件描述语言(Hardware Description Lagnuage,HDL)通过描述硬件的实现方法,来 产生与之对应的真实的硬件电路,最终实现所设计的预期功能。

Verilog HDL 和 C 语言的比较

C 语言所描述的代码功能在执行时都是一行 一行顺序执行的,而 Verilog 语言在设计完成后执行时则是并行执行的,C 语言所描述的代 码功能并不会真实的映射成最后的硬件,只是对内存的操作和进行数据的搬移,而用 Verilog 语言所描述的代码功能则会真真正正的生成所对应的硬件电路

Verilog HDL 语言基础语法

所有的 Verilog 代码都以 module(模块)的方式存在,一个简单的逻辑可以由一个 module 组成,复杂的逻辑可以包含多个 modules,每个 module 有独立的功能,并可通过输 入、输出端口被其它 module 调用(实例化)。通过 module 的方式可以将一些比较独立、 可以复用的功能进行模块化,代码阅读起来也比较直观。

Verilog 语法是有很多的,而且分为可综合(综合后可以生成对应的硬件电路)的语法 和不可综合(综合后不可以生成对应的硬件电路)的语法。

标识符

标识符用于定义常数、变量、信号、端口、子模块或参数名称。

逻辑值

在二进制计数中,单比特逻辑值只有“0”和“1”两种状态,而在 Verilog 语言中,为 了对电路了进行精确的建模,又增加了两种逻辑状态,即“X”和“Z”。

当“X”用作信号状态时表示未知,当用作条件判断时(在 casex 或 casez)表示不关 心;“Z”表示高阻状态,也就是没有任何驱动,通常用来对三态总线进行建模。在综合 工具眼中,或者说在实际实现的电路中,并没有什么 X 值,只存在 0、1 和 Z 三种状态。 在实际电路中还可能出现亚稳态,它既不是 0,也不是 1,而是一种不稳定的状态。

常量

常量是 Verilog 中不变的数值,Verilog 中的常量有三种类型 (1) 整数型; (2) 实数型; (3) 字符串型。

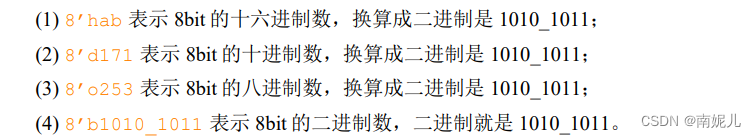

整数型常量也可以采用基数表示法表示。

变量

Verilog 语言中主要的两种变量类型

1. 线网型:表示电路间的物理连接;凡是在 always 或 initial 语句中被赋值的变量(赋值号左边的变量),不论表达的是组合逻辑还是时序逻辑, 都一定是 reg 型变量

2. 寄存器型:Verilog 中一个抽象的数据存储单元。凡是在 assign 语句中被赋值的变量,一定是 wire 型变量。

参数

参数是一种常量,通常出现在 module 内部,常被用于定义状态机的状态、数据位宽和 计数器计数个数大小等

parameter IDLE = 3'b001;

parameter CNT_1S_WIDTH = 4'd15parameter 是出现在模块内部的局部定义,只作用于声明的那个文件,可以被灵活改 变,这是 parameter 的一个重要特征。

赋值语句

赋值语句的赋值方式有两种,分别为“<=”(非阻塞赋值)和“=”(阻塞赋值)。

以赋值操作符“<=”来标识的赋值操作称为“非阻塞型过程赋值”,非阻塞赋值的特点:

- 在 begin-end 串行语句块中,一条非阻塞过程语句的执行不会阻塞下一语句的执行,也 就是说在本条非阻塞型过程赋值语句对应的赋值操作执行完之前,下一条语句也可以 开始执行;

- 仿真过程在遇到非阻塞型过程赋值语句后首先计算其右端赋值表达式的值,然后等到 仿真时间结束时再将该计算结果赋值变量。也就是说,这种情况下的赋值操作是在同 一仿真时刻上的其他普通操作结束后才得以执行。

以 赋 值 操 作 符 “ = ” 来 标 识 的 赋 值 操 作 称 为 “ 阻 塞 型 过 程 赋 值,阻塞赋值的特点:

- 在 begin-end 串行语句块中的各条阻塞型过程赋值语句将以它们在顺序块后排列次序依 次得到执行;

- 阻塞型过程赋值语句的执行过程是:首先计算右端赋值表达式的值,然后立即将计算 结果赋值给“=”左端的被赋值变量。

阻塞型过程赋值语句的这两个特点表明:仿真进程在遇到阻塞型过程赋值语句时将计 算表达式的值并立即将其结果赋给等式左边的被赋值变量;在串行语句块中,下一条语句 的执行会被本条阻塞型过程赋值语句所阻塞,只有在当前这条阻塞型过程赋值语句所对应 的赋值操作执行完后下一条语句才能开始执行。

关系运算符

(1) a < b,a 小于 b

(2) a > b,a 大于 b

(3) a <= b,a 小于或者等于 b

(4) a >= b,a 大于或者等于 b归约运算符、按位运算符和逻辑运算符

归约运算符和按位运算符

“&”操作符有两种用途,既可以作为一元运算符(仅有一个参与运算的量),也可 以作为二元运算符(有两个参与运算的量)。

当“&”作为一元运算符时表示归约与。&m 是将 m 中所有比特相与,最后的结果为 1bit

&4’b1111 = 1&1&1&1 = 1’b1

&4’b1101 = 1&1&0&1 = 1’b0当“&”作为二元运算符时表示按位与。m&n 是将 m 的每个比特与 n 的相应比特相 与

4’b1010&4’b0101 = 4’b0000

4’b1101&4’b1111 = 4’b1101

逻辑运算符

m&&n 是判断 m 和 n 是否都为真,最后的结果只有 1bit,如果都为真则输出 1’b1,如果不都为真则输出 1’b0。

移位运算符

移位运算符是二元运算符,左移符号为“<<”,右移符号是’>>‘,将运算符左边的 操作数左移或右移指定的位数,用 0 来补充空闲位。如果右边操作数的值为 x 或 z,则移 位结果为未知数 x。

4'b1000 >> 3 后的结果为 4'b0001,4'b1000 >> 4 的结果为 4'b0000。

移位运算符在使用时,左移一位可以看成是乘以 2,右移一位可以看成是除以 2。所以 移位运算符用在计算中,代替乘法和除法。尤其是除法,使用移位的方式,可以节省资 源。但使用的前提是数据位宽要进行拓展,否则就会出现移位后全为 0 的情况。

条件运算符

由条件运算符组成的条件表达式的一般形式为:表达式 1 ? 表达式 2 : 表达式 3

执行过程是:当表达式 1 为真,则表达式 2 作为条件表达式的值,否则以表达式 3 作 为条件表达式的值。

if-else 只能在 always 块中使用, 不能在 assign 中使用,如果我们想在 assign 中使用就需要用到条件运算符

优先级

总的优先级关系为:归约运算符 > 算数运算符 > 移位运算符 > 关系运算符 > “= =” 和“!=”> 按位运算符 > “&&”和“||”> 条件运算符,总的来说是一元运算符 > 二元运 算符 > 三元运算符。

位拼接运算符

位拼接运算符由一对花括号加逗号组成“{ , }”,拼接的不同数据之间用“,”隔 开。

实现增长位宽的作用

如果需要将 8bit 的 a、3bit 的 b、5bit 的按顺序拼接成一个 16 位的 d,表示方法为

wire [15:0] d;

d = {a, b, c}实现移位的作用

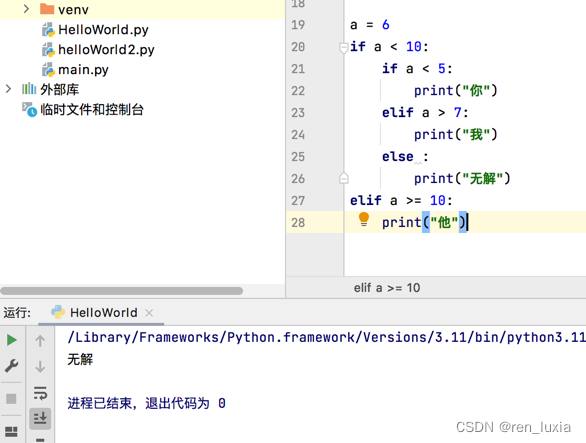

if-else 与 case

if(<条件表达式 1>)

语句或语句块 1;

else if(<条件表达式 2>)

语句或语句块 2;

………

else

case(<控制表达式>)

<分支语句 1> : 语句块 1;

<分支语句 2> : 语句块 2;

<分支语句 3> : 语句块 3;

………

<分支语句 n> : 语句块 n;

default : 语句块 n+1;

endcase

inout 双向端口

在定义端口列表的时候我们知道输入用 input,输出用 output,其实还有一种双向端 口,我们定义时使用 inout。

定义为 inout 的端口表示该端口是双向口,既可以作为数据的输入端口也可以作为 数据的输出端口

Verilog 语言中的系统任务和系统函数

Verilog 语言中预先定义了一些任务和函数,用于完成一些特殊的功能,它们被称为系 统任务和系统函数,这些函数大多数都是只能在 Testbench 仿真中使用的

`timescale 1ns/1ns //时间尺度预编译指令 时间单位/时间精度

仿真中使用“#数字”表示延时相应时间单位的时间,例#10 表示延时 10 个单位的时间, 即 10ns。

`timescale 1ns/10ps 精度 0.01,#10.11 表示延时 10110ps。

(1秒(s) =1000毫秒(ms)

1毫秒(ms)=1000微秒 (us)

1微秒(us)=1000纳秒 (ns)

1纳秒(ns)=1000皮秒 (ps))

$display 用于输出、打印信息

$display("%b+%b=%d",a, b, c);//格式“%b+%b=%d” 格式控制,未指定时默认十进

$write 用于输出、打印信息

$write("%b+%b=%d\n",a, b, c); //“%b+%b=%d\n” 格式控制,未指定时默认十进制

%h 或%H //以十六进制的形式输出

%d 或%D //以十进制的形式输出

%o 或%O //以八进制的形式输出

%b 或%B //以二进制的形式输出$strobe 用于输出、打印信息

$strobe("%b+%b=%d",a,b,c); //“%b+%b=%d” 格式控制,未指定时默认十进制

$monitor 用于持续监测变量

$monitor("%b+%b=%d",a,b,c); //“%b+%b=%d” 格式控制,未指定时默认十进制

$readmemb 用于读二进制文件函数 ,$readmemh 用于读十六进制文件函数

$readmemb("<数据文件名>",<存贮器名>);

$readmemh("<数据文件名>",<存贮器名>);