文章目录

-

- 一、问题描述

- 二、verilog源码

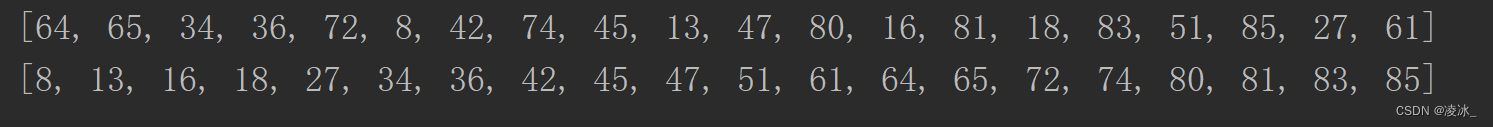

- 三、仿真结果

一、问题描述

if 语句通常创建一个 2 对 1 多路复用器,如果条件为 true,则选择一个输入,如果条件为 false,则选择另一个输入。

always @(*) begin

if (condition) begin

out = x;

end

else begin

out = y;

end

end

这等效于使用带有条件运算符的连续赋值:

assign out = condition ? (x : y);

使用if语句不当时会产生不想要的锁存器,想要if语句生成组合逻辑必须让其所有情形下都有对应的分支语句。

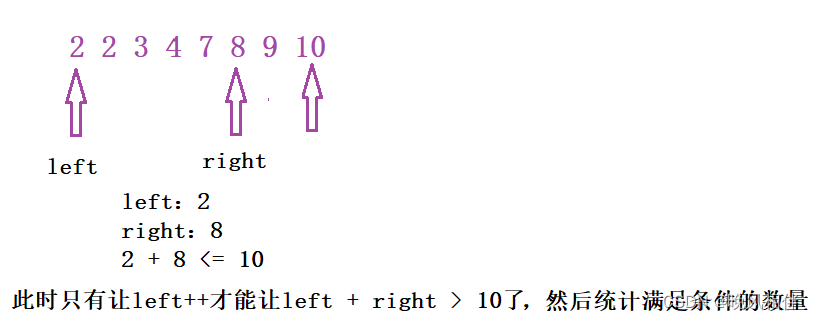

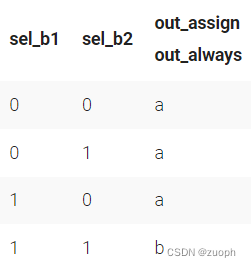

构建一个 2 对 1 多路复用器,在 a 和 b 之间进行选择。选择 b 是否两者都 sel_b1 sel_b2 为 true。否则,请选择 a 。执行两次相同的操作,一次使用 assign语句,一次使用 if 过程语句。

二、verilog源码

// s