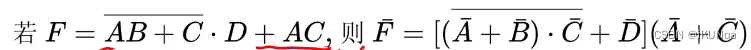

数制与码制

十进制转二进制

8 bits = 1 Byte

2|12 //12=1100自下而上 商为0为止

2|_ 6_…0

2|_ 3_…0

2|1…1

0…1

0.375 //0.375=0.011自上而下 小数点为0为止

x 2

————

0.75…0

x 2

————

1.5…1

x 2

————

1…1

BCD码:每4位二进制表示一位十进制

8421 BCD码 有权值码 8xa3+4xa2+2xa1+a0

5421 BCD码

2421 BCD码

余3码 8421+011

有两个码组表示一个数时,选择高位为1的(5以后有两个码组可以表示一个数)

明码:编码形式唯一

格雷码:相邻码组只有一位不同

循环码,不是有权值码

对称轴两边最高位对称取反,其余低位对称相等

由原二进制相邻位异或得到,第一位不变

奇偶校验码:只能检一位错,不能纠错

带符号的编码:原码反码补码

原码默认8位,1位符号位+7个数值位

反码:正数不变,负数反码为符号位为1不变+原码的数值按位取反

补码(类似于时钟):正数和0的补码与原码相同;负数的补码:负数的反码+1

快捷算法:原码从右到左第一个1不变,右边的不变,左边取反

补码可以实现正数与负数的二进制运算

原码:-(2n-1-1)~+(2n-1-1)包括+0、-0

反码:-(2n-1-1)~+(2n-1-1)包括+0、-0

补码:-(2n-1)~+(2n-1-1)不包括-0,包括-(2n-1)

逻辑代数

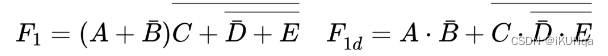

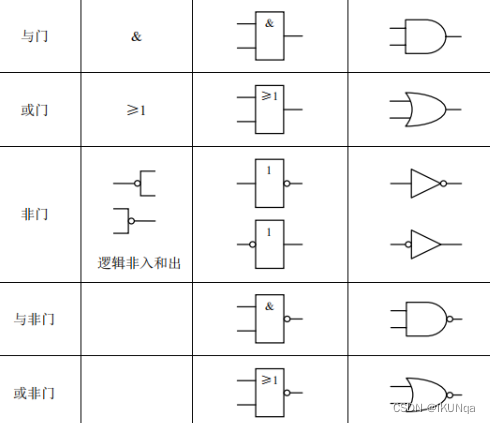

逻辑关系的表达方法:逻辑真值表,逻辑表达式,逻辑图(电路图),波形图,卡诺图,硬件描述语言

三态门:高阻态=隔断状态 EN=1电路正常,EN=0高阻态

分配律

A+BC=(A+B)(A+C)

A+A’B=A+B(一个项取反恰好是另一项的部分因子,则该部分因子可以消去)

AB+A’C+BCD=AB+A’C(两个项的部分因子互补,且该两项的其余因子都是第三项的部分因子,则第三项可消去)

反演律

(A·B)‘=A’+B’

(A+B)‘=A’·B’

三大规则

代入规则:(ABCD)‘=A’+B’+C’+D’和 (A+B+C+D)‘=A’·B’·C’·D’

反演规则:共同的非号保持不变,运算顺序不变 可证明反演律

对偶规则:共同的非号保持不变,运算顺序不变

异或和同或互为反函数和互为对偶函数

与或式:SOP积之和

或与式:POS和之积

最小项:与项,以原变量或反变量形式出现一次,只有一个变量取值使它为1

相邻项只有一位不同,n变量最小项有n个相邻项

最大项:或项,以原变量或反变量形式出现一次,只有一个变量取值使它为0

==最小项和最大项是取反的关系,eg.m3=A’BC,M3=A+B’+C’

卡诺图:

按照格雷码方式排列,圈必须为矩形且为2^n个

最大项在卡诺图中写入0

圈1为F,圈0为F’

组合逻辑电路

逻辑门符号

竞争与冒险:

竞争:当一个逻辑门的两个输入端信号同时向相反方向变化时,从变化开始到达稳定状态所需的时间不同

冒险:逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲(过渡干扰脉冲/毛刺)的想想现象

判断竞争冒险:

代数法:输出函数出现互补信号 eg.F=A+A’(产生负向尖峰脉冲) F=AA’(产生正向尖峰脉冲)

卡诺图:是否存在两个圈相切但不相交

消除竞争冒险:

更改逻辑设计

接入滤波电容

引入选通脉冲或封锁脉冲

常用组合逻辑器件

编码器

译码器

加法器:

一位加法器:

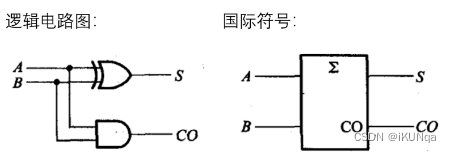

半加器 S=A⊕B为A、B相加的和,CO=AB为进位输出

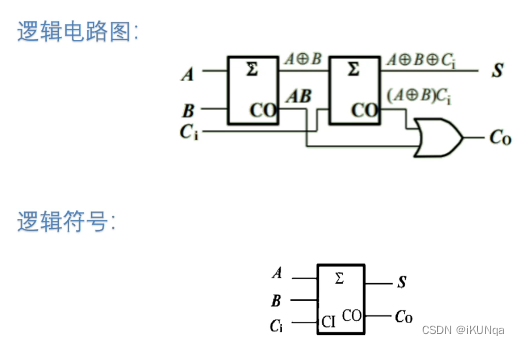

全加器(需要考虑来自低位的进位)S=A⊕B⊕Ci为A、B相加的和(需要加上Ci),CO=AB+(A⊕B)Ci为进位输出

多位加法器:串行进位加法器 逐级传递,运行速度慢(超前进位加法器)

数据选择器(MUX)2^n输入,1位输出

数值比较器

锁存器与触发器

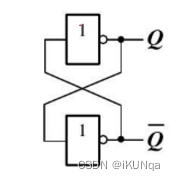

锁存器:直接由激励信号控制电路状态的存储单元

触发器:由时钟与激励信号一起控制电路状态;可认为是两个不同电平敏感的锁存器串连而成,前一个锁存器决定了触发器的建立时间,后一个决定了保持时间;具有记忆功能的双稳态电路

双稳态电路

现态Q和次态Q*

锁存器的分类

基本SR锁存器(set-reset,SR不能同时为1):与非门SR锁存器(低电平),或非门SR锁存器(SR=00时,保持现态;SR=01/10,看R是否复位;SR=11,禁止)

D锁存器:解决SR不能同时为1的问题,但对毛刺敏感,进一步提出了D触发器

触发器的分类

钟控(门控)RS触发器:基本SR触发器+两个与门 高电平触发

D触发器 电平触发Q*=D,两个电平触发的D触发器可组成一个边沿触发的D触发器

钟控JK触发器 状态方程:Q*=JQ’+K’Q

边沿JK触发器

钟控T触发器 状态方程:Q*=TQ’+T’Q

时序逻辑电路

时序逻辑电路:组合逻辑电路+存储电路(记忆功能)

按时钟分类:同步与异步时序电路

按外输出与外输入的关系:Mealy型(Z=F(X,Q)X为外部输入,Q为当前状态)和Moore型(Z=F(Q))

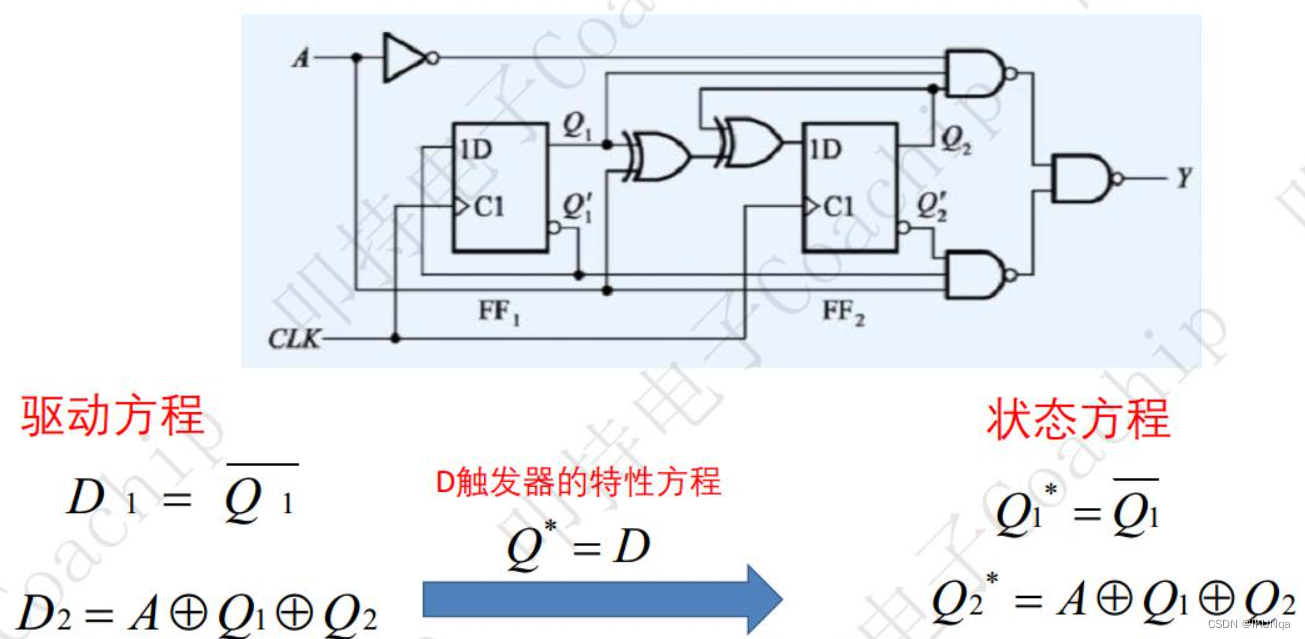

电路图分析

激励方程(驱动方程)代入特征方程得状态方程,再画出状态转换表、状态转换图