🔥点击查看精选 CXL 系列文章🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/134131924】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

- 💬 直达博主:loveic_lovelife 。(搜索或点击扫码)

文章目录

- Cachemem Message 定义、使用

- Arb/Mux仲裁问题

- Retry 问题

- CXL Latency

- Degrade Mode

- HDM/MLD 应用

- 识别不到 NUMA 节点

- 仿真问题

- 参与讨论

以下问答来源于博主 MangoPapa 牵头组织的 【CXL 技术交流群】,博主仅对讨论内容进行总结记录,不保证问题答案的正确性。如有谬误,欢迎指出;如持异见,欢迎讨论。如有意加入,欢迎联系我。

Cachemem Message 定义、使用

-

对博文《CXL.cache D2H Message 释义》内容存疑,若 Device 中 Cache Miss 后发出 RdOwnNoData,Host 不回复数据,那么 Device 内该 Cacheline 还是 Invalid 吗?

若 Host 回复了 GO-E,则 Device 内该 Cacheline 状态变化为 I->E,即不在为 Invalid。 -

追问:Device 内该 Cacheline 处于 E 态,此前又没有数据回来,数据和内存中不一致吧?

RdOwnNodata 多用于 Cacheline Write 之前获取 Exclusive 权限,其状态会 I->E->M,I->E 之后、E->M 之前不要去读,读的话需要用 RdOwn 来保证读到的数据与内存一致,不能用 RdOwnNoData。 -

下图为 CXL 2.0 Spec 中 Device Read to Device-attached Memory的 示意图,对于 Host-bias 访问,如果 Host 内也有一份 Copy,Host Copy 如何写回到 Device Memory 中?根据文档中的描述(描述随附),是否会在图中的箭头位置插入一些操作?

文档描述:In the first one, a device read to device attached memory happened to find the line in Host bias. Since it is in Host bias, the device needs to send the request to the Host toresolve coherency. The Host, after resolving coherency, sends a MemRdFwd on CXL.mem to complete the transaction, at which point the device can complete the read internally.

回复1:我感觉如果是 E/S 的 Copy,Host 就把状态变成 Invalid,把所有权给 Device,如果是 M,就发起 CXL.mem MemWr 把数据写回,然后再发 MemWrFwd。

回复2:我感觉应该是根据 Rd 的 op 决定的。

补充:CXL 3.0 中指出了具体的 Rd 类型。

Arb/Mux仲裁问题

-

已知 CXL Arb/Mux 仲裁策略支持自定义,请问大家是如何考虑的?采用的什么策略?

我们采用了 WRR(Weighted Round Robin,加权循环调度)策略,Cachemem 权重高,IO 权重低。 -

追问:是否要支持 Adapter 仲裁权重任意可配?比如 1:64 或更大?

比例无需配置太大,只需保证 Value 大小稍微大一点即可。

Retry 问题

-

为什么 Retry Framing Sequence 定义 Retry.Req/Ack 之前需要 5 个 Retry.Frame 而不是 4 个?

根据协议,最多支持连续发送 4 个ADF (All Data Flit) 是为了区分发 5 个 Retry.Frame。 -

追问:为什么 4 个 Retry.Frame 不足以区分?

因为 ADF 最多有四个,如果 Retry.Frame 也发四个的话,连续四个 ADF 里的字段如果被识别成 Retry.Frame 就可能会被误认成要 Retry 了,但是连续五个 Retry.Frame 是不会跟 ADF 混淆的。 -

追问:假设为 4 个 Retry.Frame,即便 4 个 ADF 全部被误识别为 Retry.Frame,其后仍有 4*Retry.Frame+Retry.Req/Ack 不是么?怎么会识别为需要 Retry?ADF 必须先于 Control Flit 且不能 Interleave。

CXL 1.1 时最大支持连续 5 ADF(Max All-Data-Flit=5),因此 5*Retry.Frame+Retry.Req/Ack 防止将 ADF 误判为 Retry,这样是解释地通的。到了 CXL 2.0,最大连续 ADF 数目将为 4,但是 Retry.Frame 数目未作变动(兼容性考虑?)。

补充:关于 retry.frame为啥保持在了 5,可能啊,可能还有BE的原因,BEP=1 时 1 个 data header 对应 5 slot。CXL 1.1 时候也有 BE 且 max adf=5,至于为啥 retry.frame 还是 5 我也没深究过

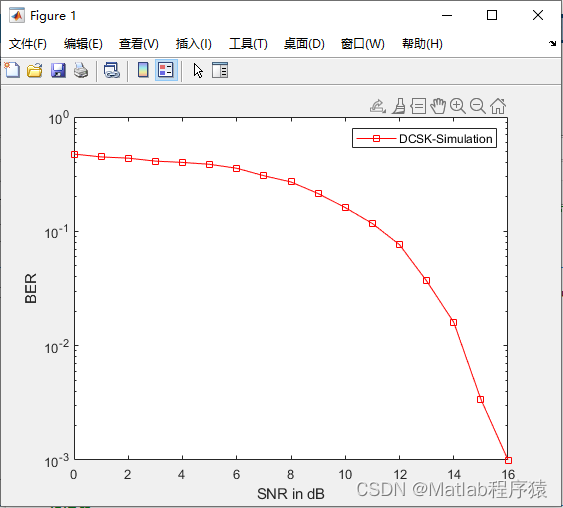

CXL Latency

-

CXL 相比 PCIe,Latency 更小的原因是?

-

如下图 Device 读 Host Memory 的 Data Path,为何 CXL.io 或 PCIe 在 DDR Ctrl 到颗粒之间会多出那么多延迟?Host 端 PCIe RC 的 AXI Master 去 DDR 取数据无需 CPU 介入吧?(图中红圈内含 CPU 操作)

讨论1:是否是因为 PCIe 访问主存比 CXL 访问主存多了 DMA 搬运。 -

追问:RC 收到 EP 的 MRd TLP 经 tlp2axi bridge 后由 RC 的 AXI Master 经 Bus Matrix 到DDR,无需 DMA 吧?

这是 IO Coherency 引入的高延时吧。图中有歧义,不应体现在 DDR Ctrl 到颗粒之间的延时中。

Degrade Mode

-

CXL 在降级模式下是怎么操作的?

个人理解就是支持 Gen5 x16 的 Device,Host 目标速率设成非 32GT/s 或者 Link Width 非 x16 就是Degraded 模式了 -

追问:那 Degrade 模式下 CXL 还是和 32G 时传输流程一样么?就只是速率变慢了?

Link Width 在Synopsys IP 都是可配置的。我们曾经用 FPGA 开发板在 Gen4 协商速率下工作,按照我的理解,仅仅速率变了,其他都没变。

HDM/MLD 应用

-

CXL DVSEC 中 CXL Range Size (Memory_Size) 为 RO,这个值是固定的吗?如果后期插的存储条大小变化怎么办?

在 PCIe 建链前,由 CPU 初始化配置。后续如果更改了,更改 CPU 配置值就可以。 -

CXL Device 的 Function 是如何规定的?需要几个 PF?是否需要 VF?

需要 1 个 PF,不需要 VF。 -

追问:MLD 呢?是 1PF+15VF 还是 16PF?

讨论1:PF 应该不会设置那么多,底层 PCIe Ctrl 难以 Hold 住 16PF。

讨论2:.mem 和内存一个等级,无需虚拟化。对于 PCIe 可以 1PF+nVF,对于 CXL.mem无需 VF。

讨论3:Function 和 MLD 是两个概念,CXL.mem 应该没有 VF 内容。一个 Mem Device 可以指出 16 MLD,每个 MLD 类似于一个 PF,但是没有 BDF 的说法。多个 Host Bridge 绑定多个 MLD,类似于分区。

讨论4:我感觉 PCIe 里的 SRIOV 做虚拟化是两层内涵,1.通过 VF 把设备的的资源/队列实体让客户机直接编程 2.Host 侧部署 SMMU 支持设备对主存的基于客户机虚拟地址的访问 CXL 或许在第二点上和 PCIe 有不同,但我感觉第一点还在。

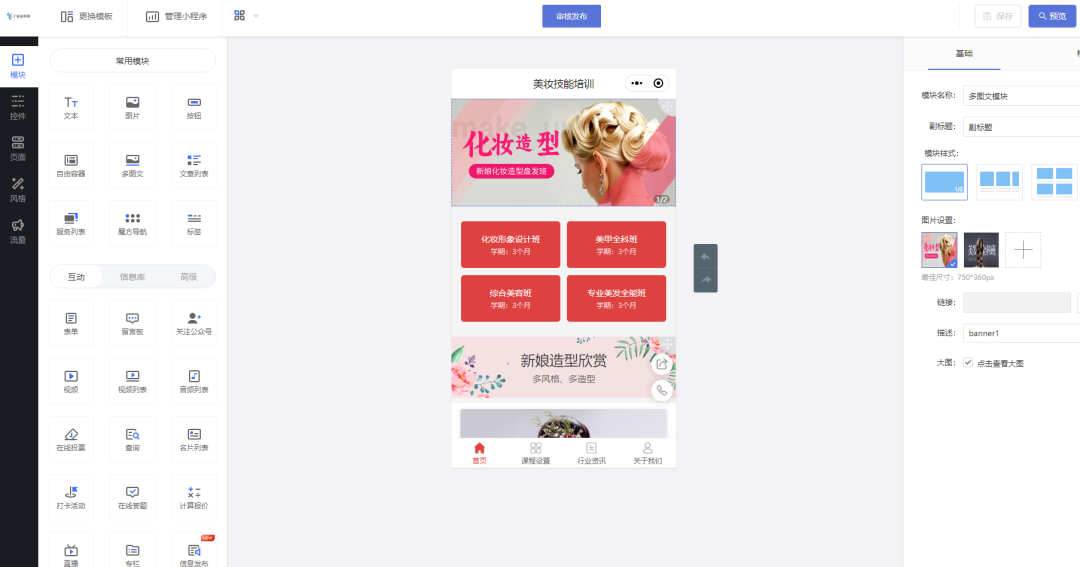

阶段性结论:确实不是 BDF 了,而是 LD-ID,参照下图。

-

追问:如果一个 MLD 支持 16 个 LD,每个 LD 一个 Function,配置 IP 需要几个 Function?

指出几个 LD 就配置几个 Function,和 CXL 关系不大。 -

目前有做MLD Feature的吗?

<无人回答>

识别不到 NUMA 节点

-

该如何配置 PCIe DVSEC for CXL Device 中的 Range?能够 Link Up,但 Host(联想)识别不到 NUMA 形式的节点。

由 Device 给定 Size,Host OS 获取 Device 分配的 Range。

我们 OS 系统上同样遇到了找不到 NUMA 节点的情况,采取了以下两个操作:- Install the OS with UEFI boot mode.

- Try for simplified smdk kernel.(三星的 SDK)

补充:采用 Intel Host 能够 Link,但是 AMD Host Link 失败。

-

AMD Host 没起来是 Link 没起来?还是 Traffic 不通?

可以 Link 起来,但 CXL 1.1 FPGA Device 被 AMD Host识别为CXL 2.x Device。

-

采用 AMD Host 存在 Link 不起来问题,去 Compliance 时候就失败了

大概是一个 IO PM VDM Message Routing 的一个问题,如果 Device Check 了 Routing 可能会有点问题,如果是类似问题可以通过刷 Firmware 解决。

补充:AMD 反馈 Geona 板子有和别的 Vendor Link 不起来的情况。

仿真问题

- Intel Agilex I-series FPGA 的 CXL design example 仿真官方文档中说需要 avery CXL VIP,这里可不可以用其他厂商的 CXL VIP?

讨论1:如果需要在 example tb 里直接跑 example testcase,那必须用他们的 VIP。

讨论2:确实需要,跟 FAE 反复确认后需要,但可以把 CXL IP Bypass 掉,自己制造 CXL IP 输出信号给后续模块。

讨论3:是可以的,CXL.mem 或者 CXL.cache 的 boundry 再转成 AXI 到 Memory Controller , 我以前就这么做的,但是不是 Intel 的 Design。

参与讨论

superhorse,青简半卷,Yierrs,Andy,李兵,沐叶,秦木木,民工松,欢乐糗球,Jianglfl,友谊的小船需要帆,天明,Yue H,小陈麻花,MangoPapa,陆小虎,谷东昌,忠俊,晴空一鹤排云上,Exceed 星途,Stan,Eric-Xianyu,五岁抬头,Cheney.Ren,Bazinga,无问西东

|

|

🔥 精选往期 CXL 协议系列文章,请查看【 CXL 专栏】🔥

⬆️ 返回顶部 ⬆️