目录

冯·诺依曼计算机的特点

计算机硬件框图

系统复杂性管理的方法(3’Y)

计算机的工作步骤

上机前的准备

计算机的工作过程

存储器的基本组成

运算器的基本组成及操作过程

控制器

计算机组成原理课程笔记。

冯·诺依曼计算机的特点

冯·诺依曼计算机主要由以下6个特点组成,其中存储程序较为重要,我们也会主要讲解一下。

- 计算机由五大部件组成

- 指令和数据用二进制表示

- 指令由操作码和地址码组成

- 以运算器为中心

- 指令和数据以同等地位存于存储器, 可按地址寻访

- 存储程序

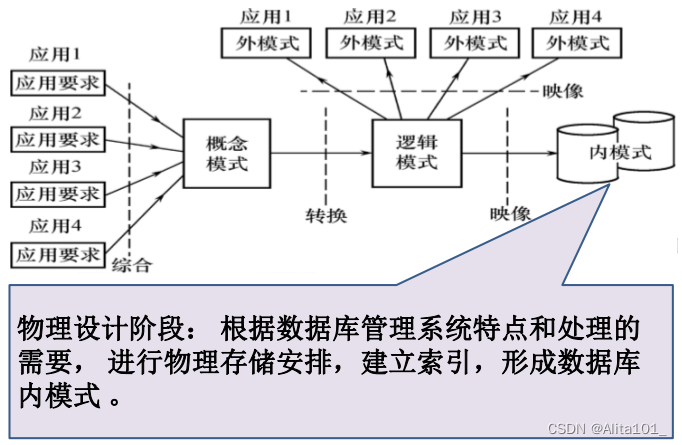

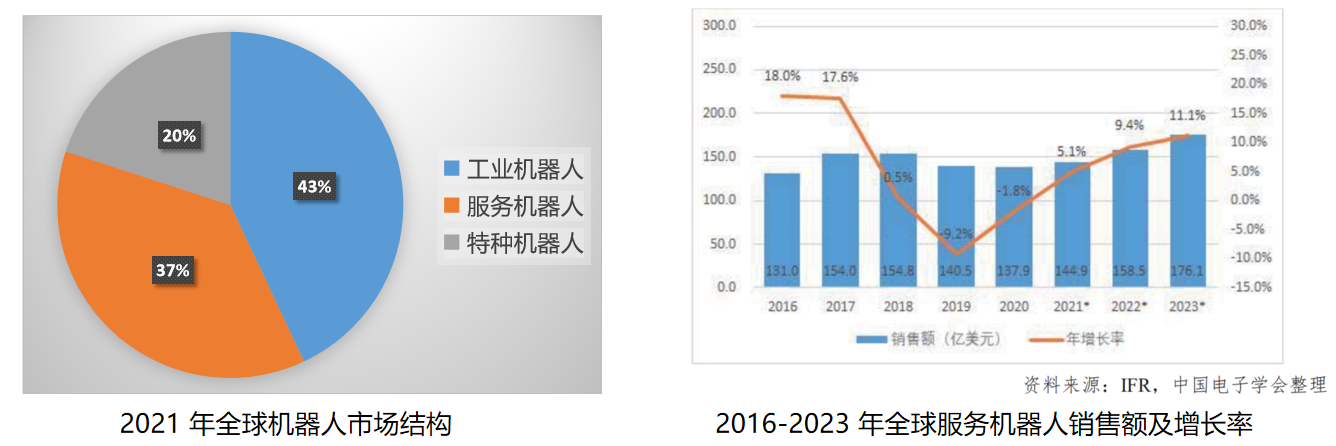

计算机硬件框图

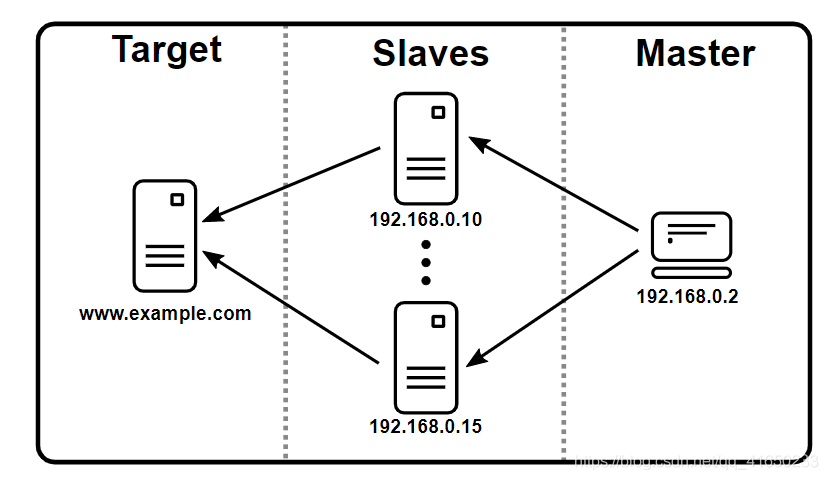

这个是冯诺依曼计算机结构框图,运算器用来完成算术运算和逻辑运算,并将运算的中间结果暂存在运算器内。存储器用来存放数据和程序。控制器用来控制、指挥程序和数据的输入、运行以及处理运算结果。 输入设备用来将人们熟悉的信息形式转换为机器能识别的信息形式,常见的有键盘、鼠标等。 输出设备可将机器运算结果转换为人们熟悉的信息形式,如打印机输出、显示器输出等。

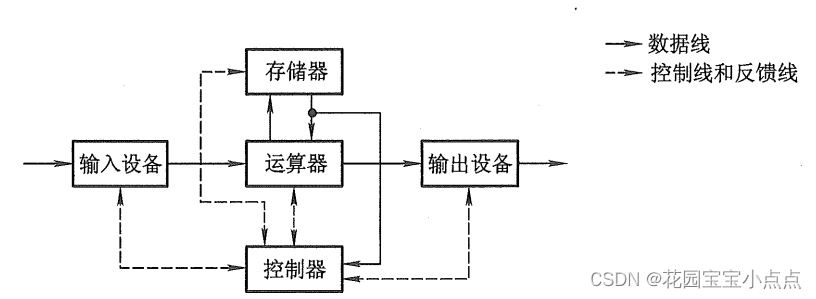

但是这个结构主要就是靠运算器工作,甚至直接输入输出也需要运算器参与,所以运算器的负载和压力较大,在此基础上,有人提出了以存储器为核心的结构框图。

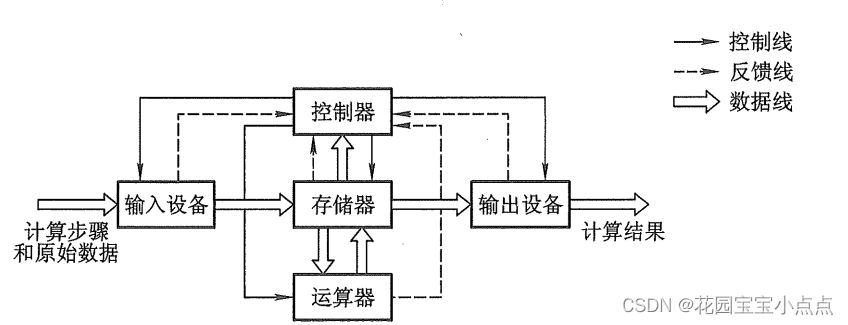

这样的话,运算器的压力就不会那么大,整体看上去也较为简洁明了。但是我们现在把控制器和运算器合成一个东西,叫CPU,加上存储器,就组成了主机。然后输入输出设备我们统称为IO设备,主机加上IO设备,就组成了硬件,这也是现代计算机的结构框图。

这样看起来,封装程度更高,更加清晰明了。

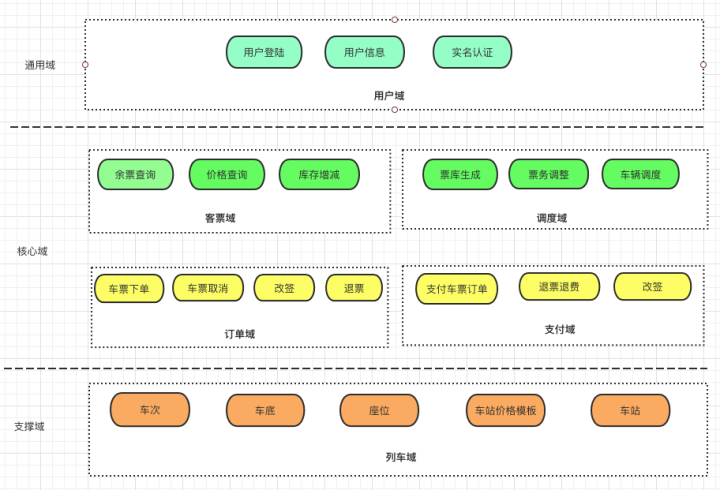

系统复杂性管理的方法(3’Y)

系统设计需要满足3Y原则:

- 层次化(Hierachy):将被设计的系统 划分为多个模块或子模块

- 模块化(Modularity):有明确定义 (well-defined)的功能和接口

- 规则性(regularity):模块更容易被重用

计算机的工作步骤

我们用计算机来解决问题的时候,首先并不是去编程,而是应该按照相应的步骤去操作。

上机前的准备

- 建立数学模型

- 确定计算方法

- 编制解题程序

计算机的工作过程

存储器的基本组成

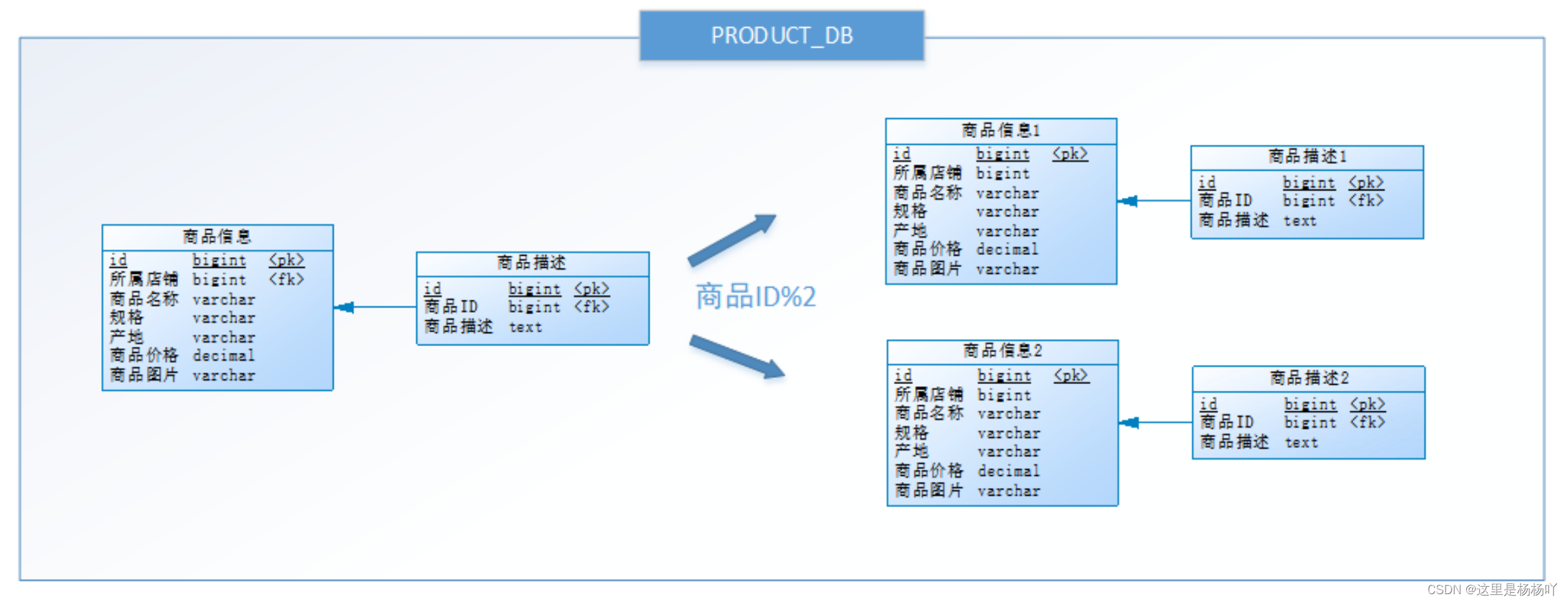

主存储器(简称主存或内存)包括存储体 、各种逻辑部件及控制电路等。存储体由许多存储单元组成,每个存储单元又包含若干个存储元件(或称存储基元、存储元),每个存储元件能寄存一位二进制代码 “0” “1” 。

书上有个这样的例子,我觉得很形象的表述了存储器的构成:如果把一个存储体看作一幢大楼,那么每个存储单元可看作大楼中的每个房间,每个存储元可看作每个房间中的一张床位,床位有人相当于 “1” ,无人相当于 “0” 。床位数相当于存储字长。 显然,每个房间都需要有一个房间编号,同样可以赋予每个存储单元一个编号,称为存储单元的地址号。

存储体 – 存储单元 – 存储元件 (0/1)

大楼 – 房间 – 床位 (无人/ 有人)

我们再提炼一下知识点:

- 存储单元 ——存放一串二进制代码

- 存储字 ——存储单元中二进制代码的组合

- 存储字长 ——存储单元中二进制代码的位数 每个存储单元赋予一个地址号

- 按地址寻访

主存储器之后,就是MAR和MDR,接下来介绍一下这两部分结构。

- MAR 存储器地址寄存器 反映存储单元的个数

- MDR 存储器数据寄存器 反映存储字长,就是数据展示寄存到这,不管是输入数据,还是输入数据。

举个例子:如果 MAR=4位 MDR=8位,存储单元个数为2^4=16, 存储字长8。

运算器的基本组成及操作过程

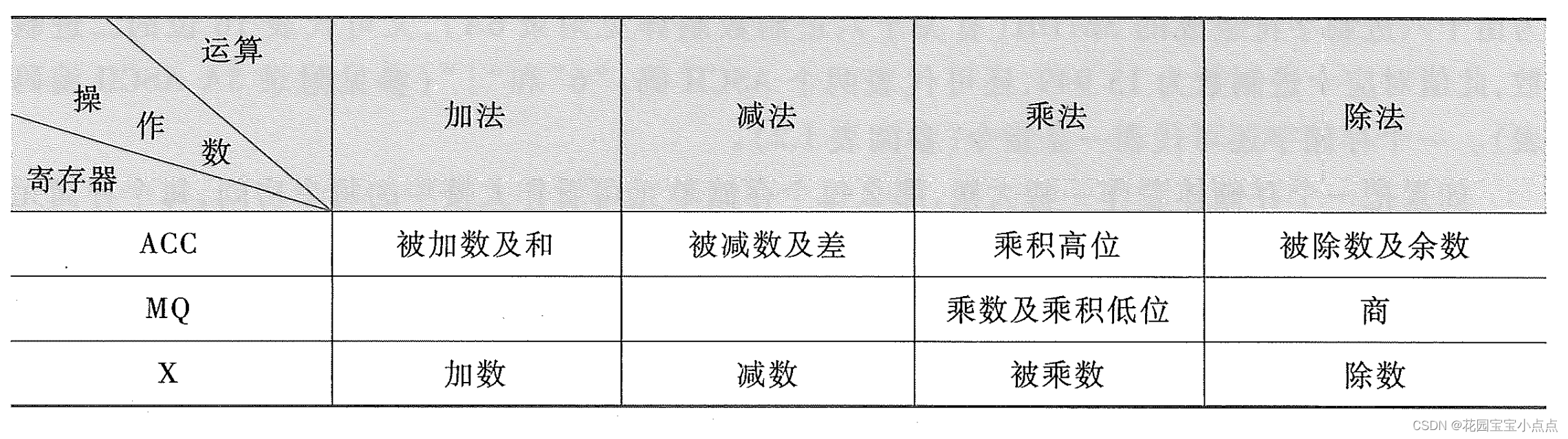

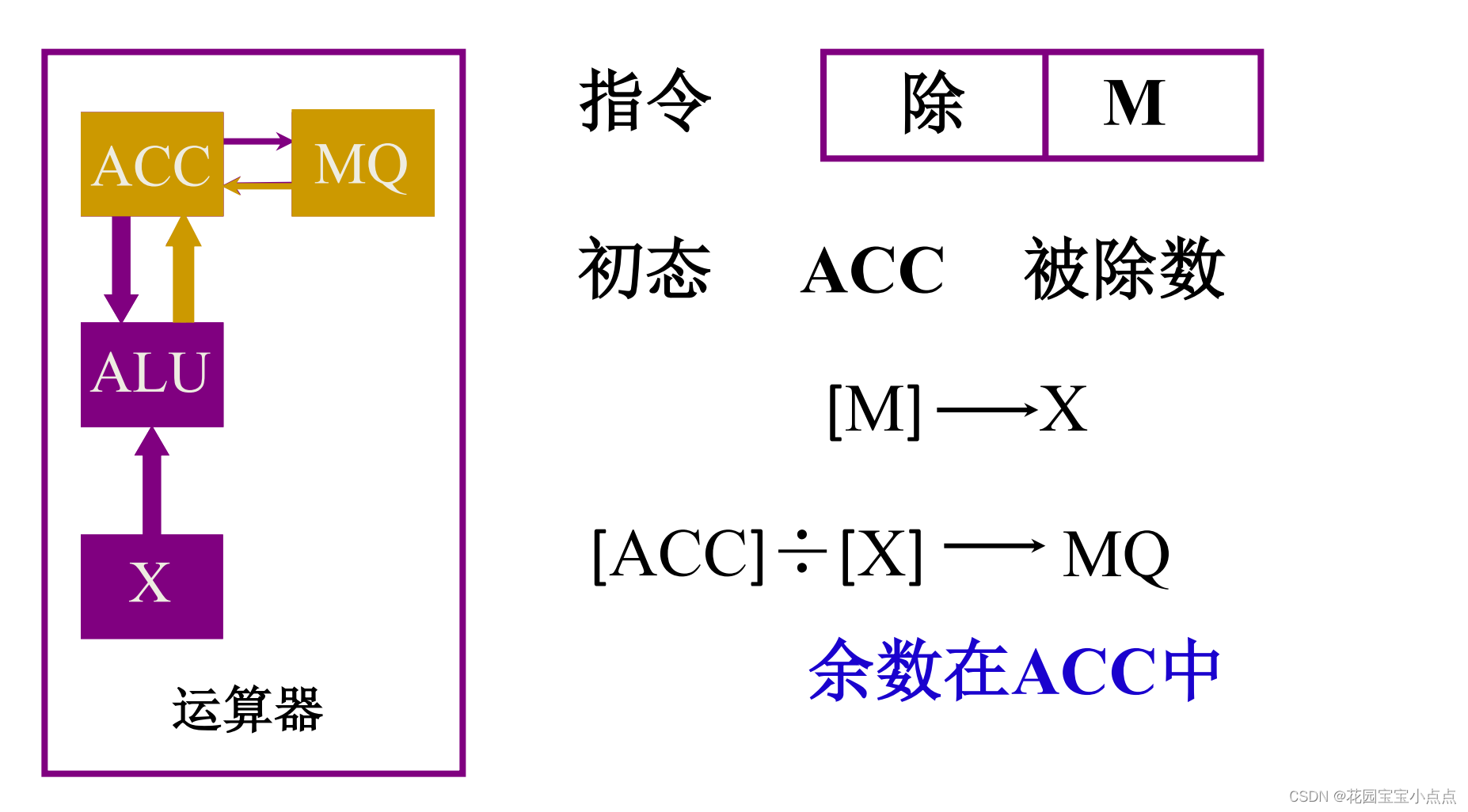

运算器,主要就是用来进行运算的,我们来简单介绍一下如何进行运算。首先,我们需要3个寄存器:ACC 为累加器, MQ 为乘商寄,X为操作数寄存器,再加上一个个算术逻辑单 (ALU)。就组成了一个简单的运算器。

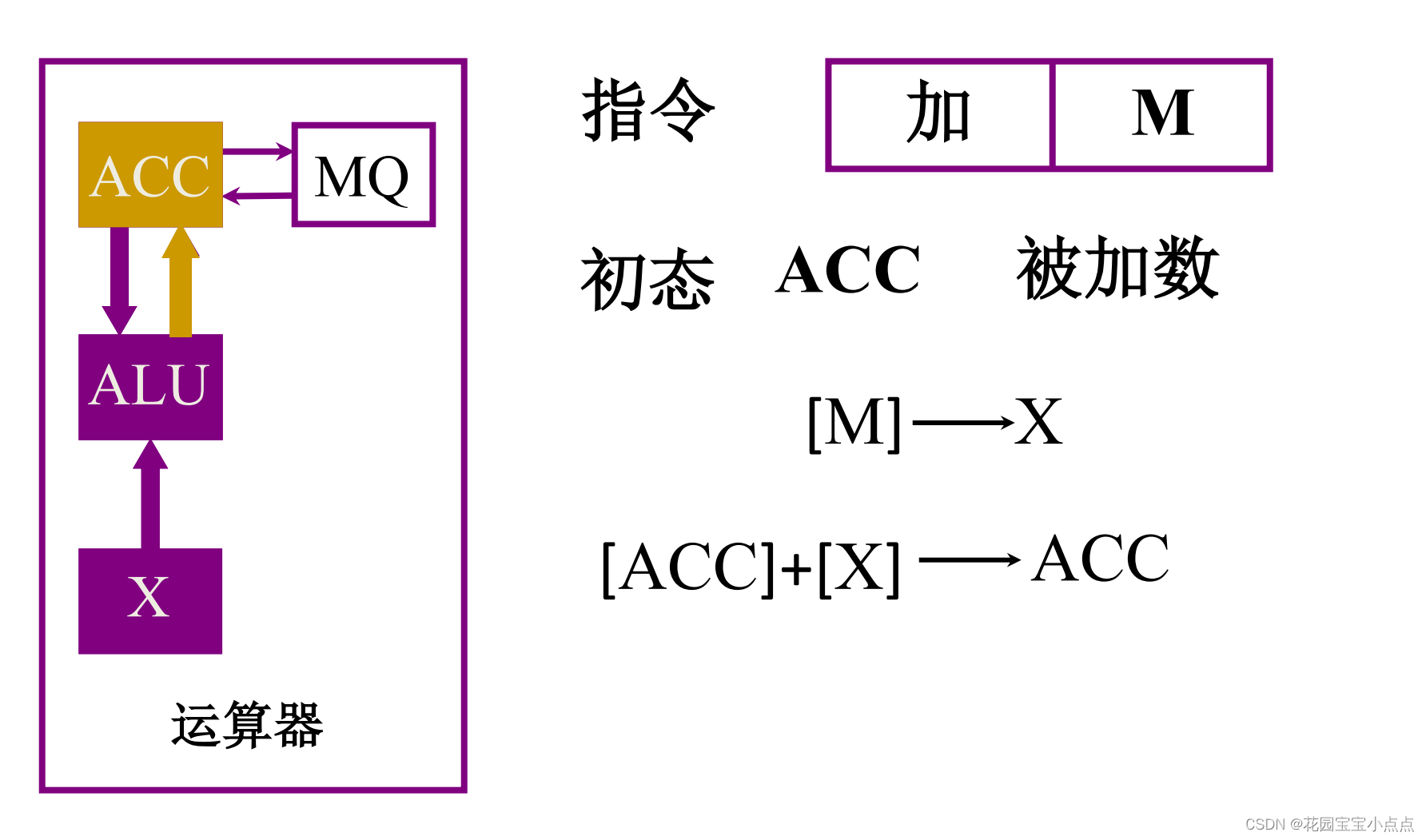

加法

即将 [ACC] 看作被加数,先从主存中取一个存放在地址号单元内的加数 [M] ,送至运算器的 寄存器中,然后将被加数 [ACC] 与加数 [X] 相加,结果(和)保留在 ACC 中。

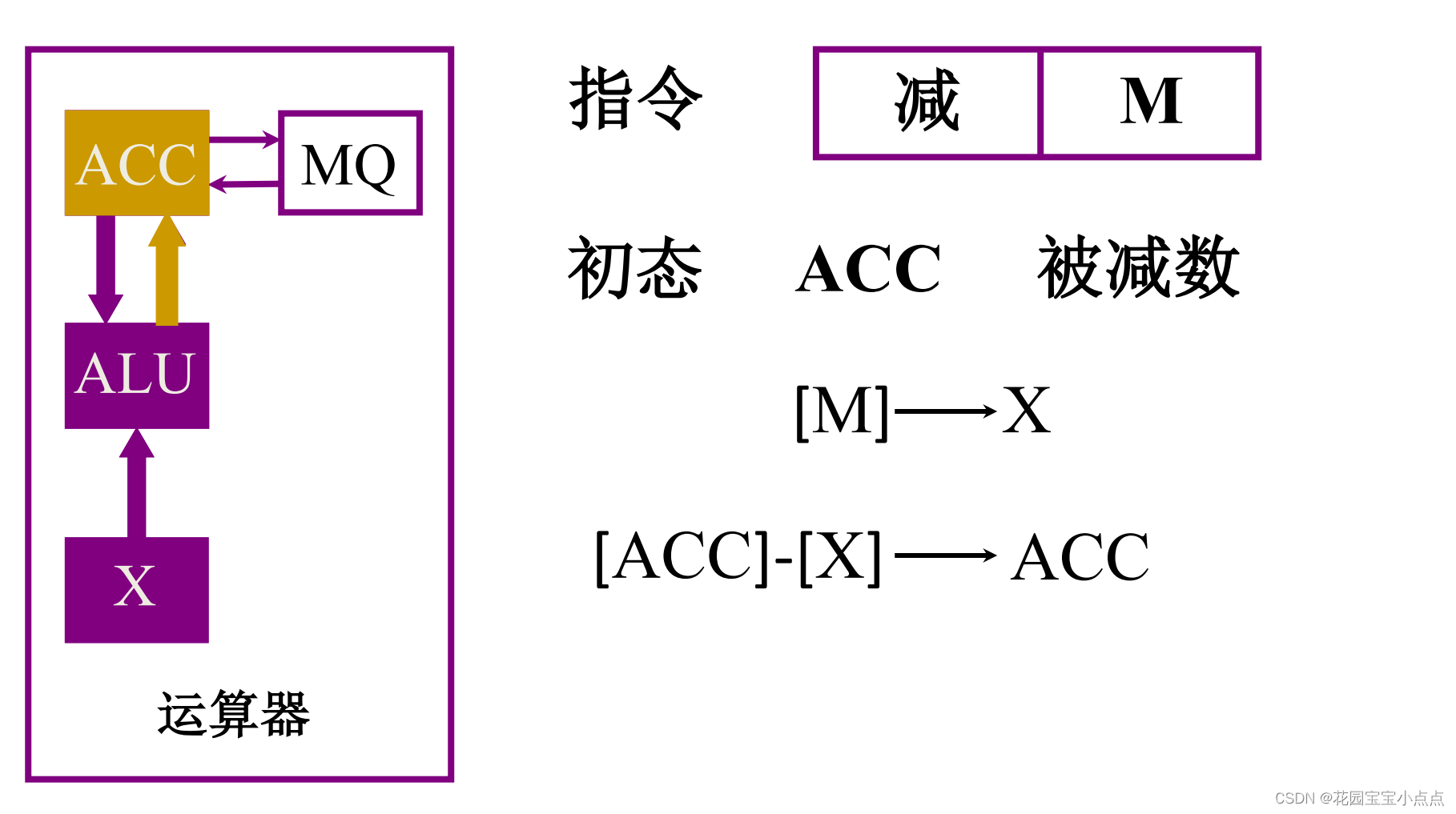

减法

将 [ACC] 看作被减数,先取出存放在主存地址号单元中的减数 [M] 并送入 ,然后 [ACC] -[X] ,结果(差)保留在 ACC 中。

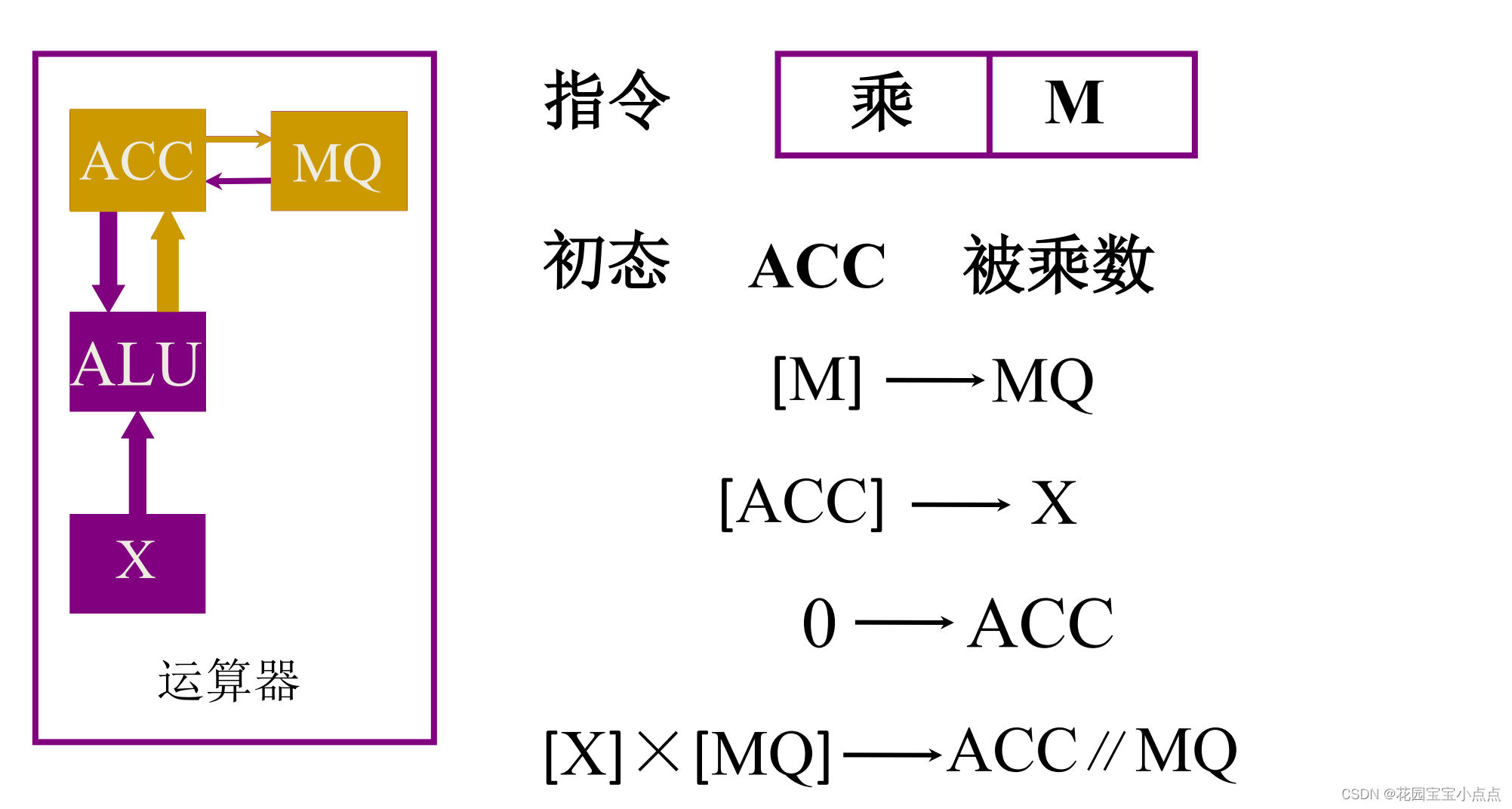

乘法

即将 [ACC] 看作被乘数,先取出存放在主存号地址单元中的乘数 [M] 并送入乘商寄存器 MQ ,再把被乘数送入寄存器,并将 ACC “0” ,然后 [X] [MQ] 相乘,结果(积)的高位保留在 ACC 中,低位保留在 MQ 中。注意,两根斜杠就是表示寄存器链接的意思。

除法

即将 [ACC] 看作被除数,先取出存放在主存号地址单元内的除数 [M] 并送至寄存器,然 [ACC] 除以 [X] ,结果(商)暂留千 MQ,[ACC] 为余数 。若需要将商保留在 ACC 中,只需 做一步 [MQ]->ACC 即可。

控制器

控制器由程序计数器 (Program Counter, PC) 、指令寄存器 (Instruction Register, IR) 以及控制单元 (CU) 组成。 PC 用来存放当前欲执行指令的地址,它与主存的 MAR 之间有一条直接通路, 且具有自动加的功能,即可自动形成下一条指令的地址。 IR 用来存放当前的指令, IR 的内容 来自主存的 MDR IR 中的操作码 (OP (IR) )送至 CU ,记作 OP (IR)->CU ,用来分析指令;其地址码 (Ad(IR) )作为操作数的地址送至存储器的 MAR ,记作 Ad (IR) -> MAR, CU 用来分析当前指令所需完成的操作,并发出各种微操作命令序列,用以控制所有被控对象。