前言

前面的博文已经讲了异步FIFO和同步FIFO,但并没有实现FIFO的读写位宽转换功能,此功能是FIFO的主要功能之一,应用十分广泛,因此,在前面两个模块的基础上,本文使用纯Verilog实现了读写位宽不同的FIFO,并仿真验证了设计的正确性。

相关博文,传送门:

Verilog功能模块——异步FIFO-CSDN博客

Verilog功能模块——同步FIFO-CSDN博客

一. 实现思路

思路:

-

根据读写数据位宽的关系,分两种情况,当读位宽>写位宽时组合数据;当读位宽<写位宽时分解数据

-

同步FIFO作为缓冲,深度固定为2,异步FIFO作为主体,深度为设定深度

-

当读位宽≥写位宽时,读端口逻辑无需关心,同步FIFO时钟与异步FIFO写时钟为同一时钟,只要同步FIFO中有数据就立刻读出,组合之后写入异步FIFP,所以写端口的full信号只会在异步FIFO满之后再写入两个数据才置高,此时不必担心同步FIFO因为深度为2会很快写满

-

当读位宽<写位宽时,写端口逻辑无需关心,同步FIFO时钟域异步FIFO读时钟为同一时钟,只要异步FIFO中有数据就分解之后写入到同步FIFO,所以读端口的empty信号只会在异步FIFO空之后置高,此时不必担心同步FIFO因为深度为2会很快读空

注意:

- 因为模块主体仍是异步FIFO,所以异步FIFO的“假满”和“假空”问题仍然存在,不影响功能

- FIFO实际容量总是比设定容量大,差值为两个小位宽(读/写)数据,这不影响功能

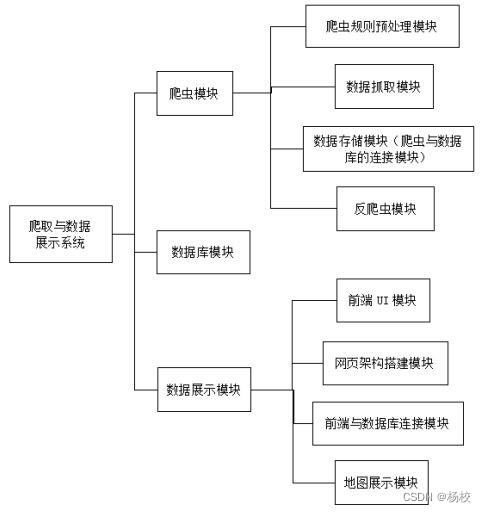

二. 模块功能框图与信号说明

信号说明:

| 分类 | 信号名称 | 输入/输出 | 说明 |

|---|---|---|---|

| 参数 | DIN_WIDTH | – | 输入数据位宽 |

| DOUT_WIDTH | – | 输出数据位宽 | |

| WADDR_WIDTH | – | 写地址位宽,FIFO深度=2**WADDR_WIDTH | |

| FWFT_EN | – | First word fall-through输出模式使能,高电平有效 | |

| MSB_FIFO | – | 1(默认值)表示高位先进先出,0表示低位先进先出 例如输入4bit,输出8bit,则首先输入的认为是8bit的高4位, 接着输入的认为是8bit的低4位。 同理,如果输入8bit,输出4bit,则首先输出的会是8bit的高4位, 接着输出的是8bit的低4位。 Vivado FIFO只有高位先进先出 | |

| FIFO写端口 | din | input | FIFO数据输入 |

| full | output | FIFO满信号 | |

| wr_en | input | FIFO写使能 | |

| wr_clk | input | FIFO写时钟 | |

| wr_rst | input | FIFO写复位 | |

| almost_full | output | FIFO快满信号,FIFO剩余容量<=1时置高 | |

| FIFO读端口 | dout | output | FIFO数据输出 |

| empty | output | FIFO空信号 | |

| rd_en | input | FIFO读使能 | |

| rd_clk | input | FIFO读时钟 | |

| rd_rst | input | FIFO读复位 | |

| almost_empty | output | FIFO快空信号,FIFO内数据量<=1时置高 |

注意:

-

信号的命名与Vivado中的FIFO IP核完全一致

-

复位均为高电平复位,与Vivado中的FIFO IP核保持一致

-

复位为异步复位,写复位和读复位可以公用一个信号,也可以分开

-

FIFO深度通过WADDR_WIDTH来设置,所以FIFO的深度必然是2的指数,如8、16、32等

-

DIN_WIDTH与DOUT_WIDTH的倍数关系必须是2的n次方,如2倍、4倍、8倍,不能是3倍、6倍

-

WADDR_WIDTH必须≥3,且RADDR_WIDTH = WADDR_WIDTH + log2(DIN_WIDTH / DOUT_WIDTH)也必须≥3

一种极限情况,DIN_WIDTH = 4,DOUT_WIDTH=16,WADDR_WIDTH=5,RADDR_WIDTH =5+log2(4/16)=3

-

MSB_FIFO用于设定高位/低位先进先出,它和一般讲的FIFO大端和小端模式不是一个概念

三. 部分代码展示

//~ 如果读位宽大于写位宽,则需要组合数据,组合成一个数据就写入到读取侧FIFO中

if (DOUT_WIDTH >= DIN_WIDTH) begin

wire clk = wr_clk;

wire rst = wr_rst;

wire wdata_almost_full;

syncFIFO # (

.DATA_WIDTH (DIN_WIDTH),

.ADDR_WIDTH (1 ),

.FWFT_EN (1 )

) syncFIFO_inst (

.din (din ),

.wr_en (wr_en ),

.full (full ),

.almost_full (wdata_almost_full),

.dout (wdata ),

.rd_en (wdata_rd_en),

.empty (wdata_empty),

.almost_empty ( ),

.clk (clk ),

.rst (rst )

);

assign almost_full = (wdata_almost_full && rdata_full) || full;

localparam RADDR_WIDTH = $clog2(2**WADDR_WIDTH * DIN_WIDTH / DOUT_WIDTH);

asyncFIFO # (

.DATA_WIDTH (DOUT_WIDTH ),

.ADDR_WIDTH (RADDR_WIDTH),

.FWFT_EN (FWFT_EN )

) asyncFIFO_inst (

.din (rdata ),

.wr_en (rdata_wr_en ),

.full (rdata_full ),

.almost_full ( ),

.wr_clk (clk ),

.wr_rst (rst ),

.dout (dout ),

.rd_en (rd_en ),

.empty (empty ),

.almost_empty (almost_empty),

.rd_clk (rd_clk ),

.rd_rst (rd_rst )

);

// 在读取侧FIFO未满,而写入侧FIFO非空时去读取写入侧FIFO

assign wdata_rd_en = ~rdata_full && ~wdata_empty;

reg [DOUT_WIDTH-1:0] rdata_r;

if (MSB_FIFO == 1) begin

always @(posedge clk or posedge rst) begin

if (rst)

rdata_r <= 'd0;

else if (wdata_rd_en)

rdata_r <= {rdata_r[DOUT_WIDTH-DIN_WIDTH-1:0], wdata}; // 先进的为高位

else

rdata_r <= rdata_r;

end

assign rdata = {rdata_r[DOUT_WIDTH-DIN_WIDTH-1:0], wdata}; // 先进的为高位

end

else begin

always @(posedge clk or posedge rst) begin

if (rst)

rdata_r <= 'd0;

else if (wdata_rd_en)

rdata_r <= {wdata, rdata_r[DOUT_WIDTH-1 : DIN_WIDTH]}; // 先进的为低位

else

rdata_r <= rdata_r;

end

assign rdata = {wdata, rdata_r[DOUT_WIDTH-1 : DIN_WIDTH]}; // 先进的为低位

end

localparam WDATA_RD_EN_CNT_MAX = DOUT_WIDTH / DIN_WIDTH - 1;

reg [$clog2(WDATA_RD_EN_CNT_MAX+1)-1 : 0] wdata_rd_en_cnt;

always @(posedge clk or posedge rst) begin

if (rst)

wdata_rd_en_cnt <= 'd0;

else if (wdata_rd_en)

wdata_rd_en_cnt <= wdata_rd_en_cnt + 1'b1;

else

wdata_rd_en_cnt <= wdata_rd_en_cnt;

end

assign rdata_wr_en = wdata_rd_en && wdata_rd_en_cnt == WDATA_RD_EN_CNT_MAX;

end

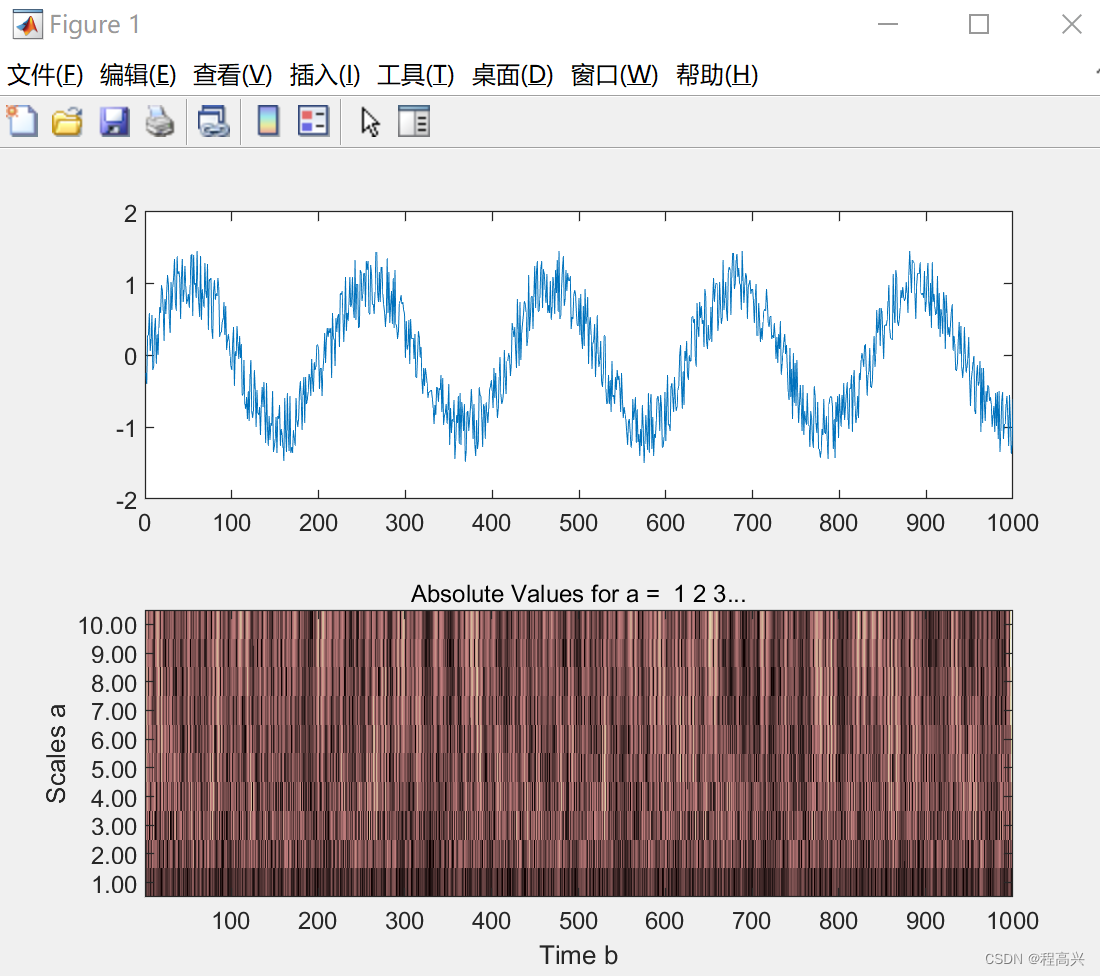

四. 功能仿真

仿真与之前异步FIFO的情形基本相同,只是要将读写数据位宽设为不一样。

testbench与之前异步FIFO基本相同,文末也有工程分享,各位同学可自行查看。

写入4bit,写入深度64,读出16bit,FWFT FIFO仿真,波形如下:

可以看到,写入4个4bit数据后,empty在延迟两个读时钟上升沿后拉低,同时数据变为16’h0123,在读出之后,数据变为16‘h4567,读端口逻辑正常。Vivado FIFO IP的empty信号拉低延迟较大,但也保证了在empty拉低时数据是有效的。

从上图可以看到,full信号和almost_full信号能正常置高,然后再读取一个数据后延迟两个写时钟上升沿一起拉低,因为读数据读一次就相当于4个写数据,所以almost_full和full是一起拉低的,这也是正确的。Vivado FIFO IP的实际深度比设定的64要大,这也是此IP的full比模块full更晚置高的原因。

可以看到模块的读数据与Vivado FIFO IP的读数据是一样的,在最后,模块FIFO读出16’h0123后,empty置高,Vivado IP因为深度更大,empty更晚置高,可见读端口的行为是正确的。

因篇幅问题,其它条件下的仿真不再展示,感兴趣的同学可通过更改testbench自行验证。

- 更改读写时钟的频率,上述仿真是写时钟频率大于读时钟频率

- FWFT_EN改为0,注意同步修改Vivado FIFO的配置

- 验证写数据位宽>读数据位宽的情况

五. 工程分享

Verilog功能模块——读写位宽不同的异步FIFO,Vivado 2021.2工程。

欢迎大家关注我的公众号:徐晓康的博客,回复以下四位数字获取。

8303

建议复制过去不会码错字!

或者在我的码云仓库获取,传送门:

徐晓康/Verilog功能模块 - 码云 - 开源中国 (gitee.com)

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。

![[yolo系列:YOLOV7改进-添加CoordConv,SAConv.]](https://img-blog.csdnimg.cn/2ba6b26858f84fef9683874df1336046.png)