ADC架构种类说明

- FLASH_架构ADC 可达GHz级别

- Pipeline_ADC架构

- SAR ADC架构

FLASH_架构ADC 可达GHz级别

通过电阻分压再经过比较器进行输出数字信号 再经过编码器

为什么会那么快的速度呢?是因为它是并行处理的 快慢主要看比较器转换速率

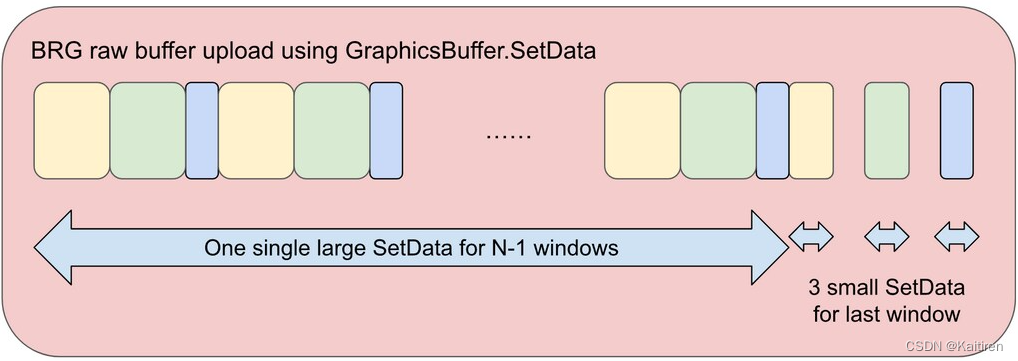

Pipeline_ADC架构

Pipeline_ADC主要思想是将ADC进行对半分进行比较,符合再次进行对半分比较…

量化误差 数据数字对应特定的一点范围的电压值 主要看起分辨率的大小

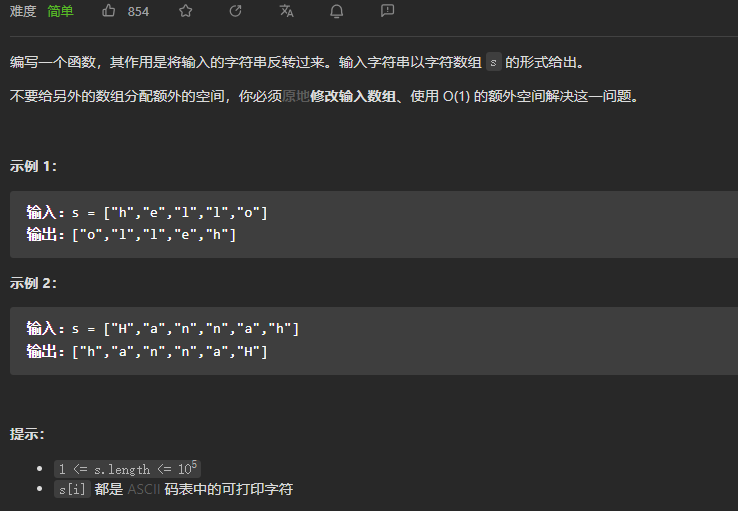

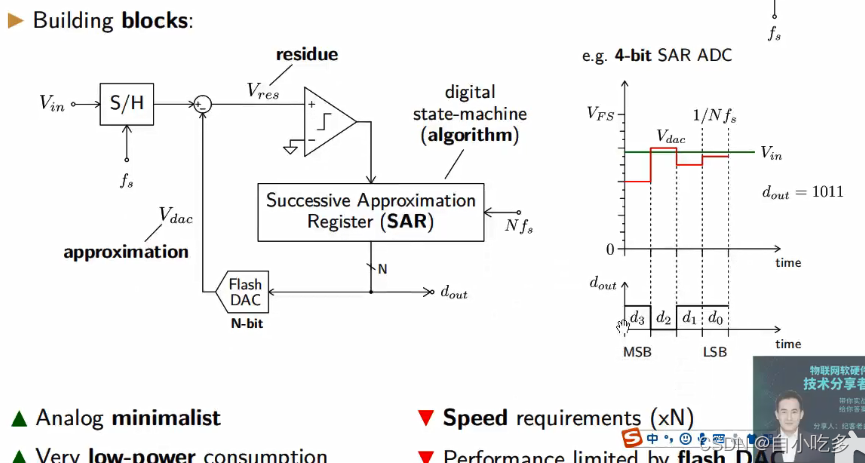

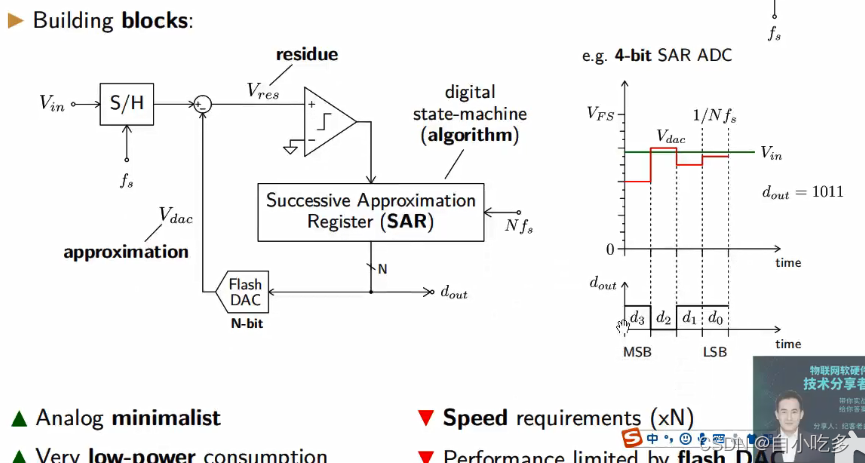

SAR ADC架构

模拟输入信号 -> 采样保持电路 -> 减法器 -> 比较器 -> SAR