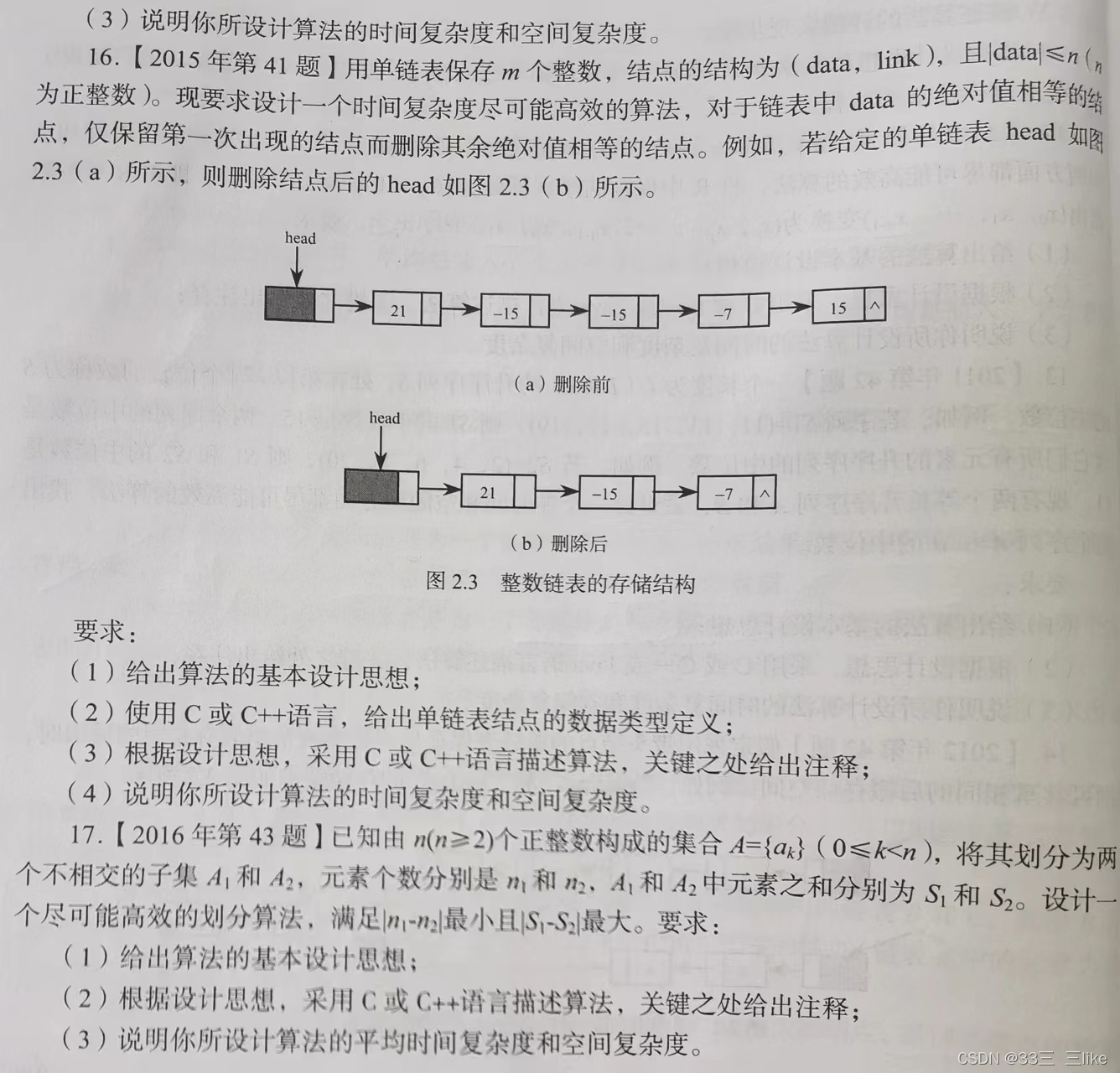

名称:数字秒表VHDL启动暂停清零(代码在文末付费下载)

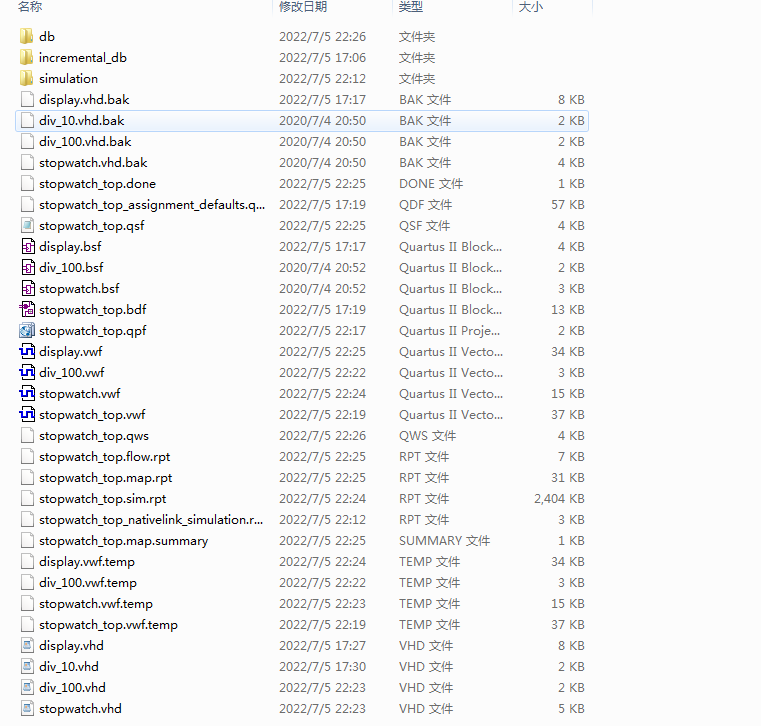

软件:Quartus

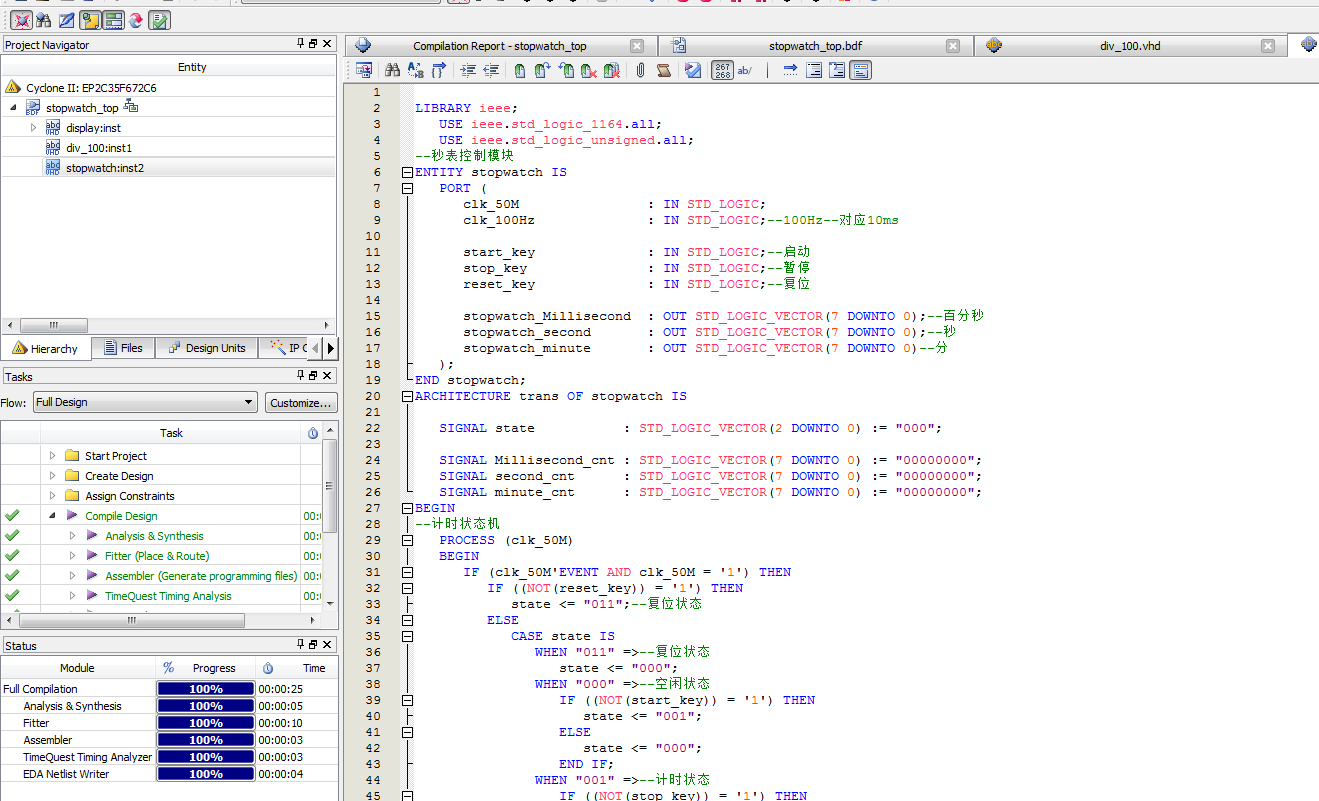

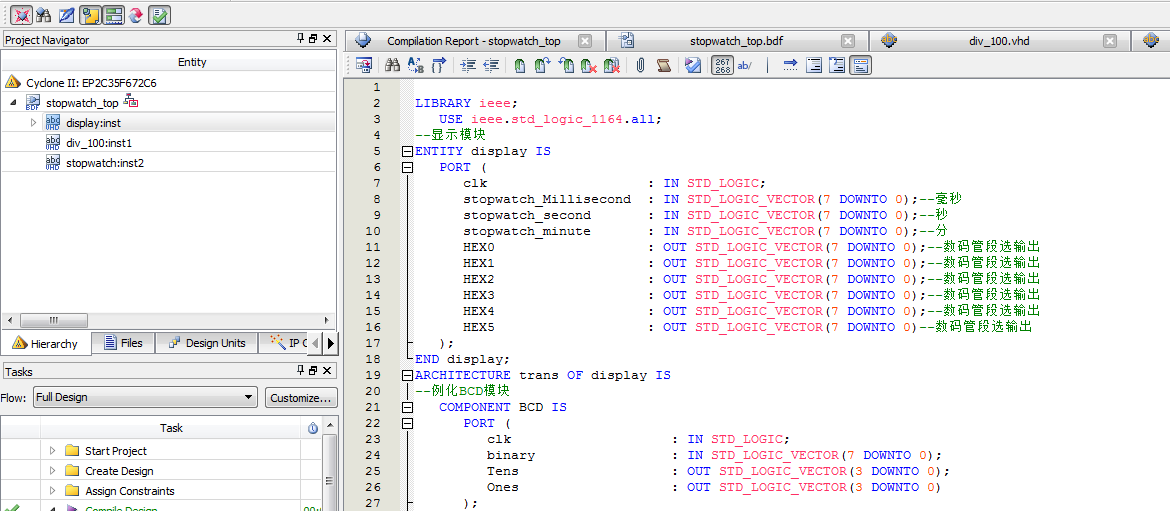

语言:VHDL

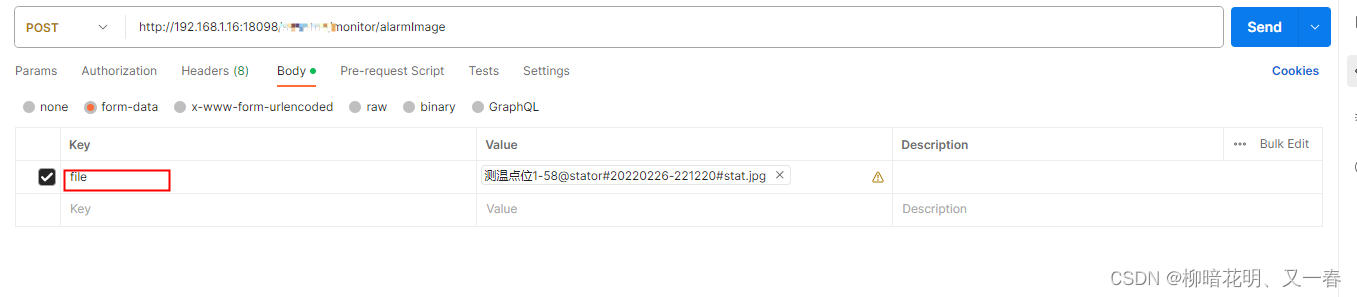

代码功能:

数字秒表

使用VHDL语言设置数字秒表。要求具有百分秒、秒和分钟显示,百分秒范围00-99,秒范围00-59,分钟范围00-59

系统具有启动/暂停功能系统具有清零功能

本资源包含2个不同的代码工程,每个工程都可独立实现上述功能。具体可以下载下文中的设计文档阅读。

演示视频:数字秒表VHDL启动暂停清零_Verilog/VHDL资源下载

FPGA代码资源下载网:hdlcode.com

代码下载:数字秒表VHDL启动暂停清零_Verilog/VHDL资源下载名称:数字秒表VHDL启动暂停清零(代码在文末付费下载)软件:Quartus语言:VHDL代码功能:数字秒表 使用VHDL语言设置数字秒表。要求具有百分秒、秒和分钟显示,百分秒范围00-99,秒范围00-59,分钟范围00-59 系统具有启动/暂停功能系统具有清零功能本资源包含2个不同的代码工程,每个工程都可独立实现上述功能。具体可以下载下文中的设计文档阅读。演示视频:FPGA代码资源下载网:hd![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=202

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=202

部分代码展示

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --秒表控制模块 ENTITY miaobaio_ctrl IS PORT ( clk_50M : IN STD_LOGIC; clk_100Hz : IN STD_LOGIC;--100Hz--对应10ms start : IN STD_LOGIC;--启动 stop : IN STD_LOGIC;--暂停 reset : IN STD_LOGIC;--复位 Millisecond : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--百分秒 second : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--秒 minute : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--分 ); END miaobaio_ctrl; ARCHITECTURE trans OF miaobaio_ctrl IS SIGNAL state : STD_LOGIC_VECTOR(2 DOWNTO 0) := "000"; SIGNAL Millisecond_cnt : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000"; SIGNAL second_cnt : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000"; SIGNAL minute_cnt : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000"; BEGIN --计时状态机 PROCESS (clk_50M) BEGIN IF (clk_50M'EVENT AND clk_50M = '1') THEN IF ((NOT(reset)) = '1') THEN state <= "011";--复位状态 ELSE CASE state IS WHEN "011" =>--复位状态 state <= "000"; WHEN "000" =>--空闲状态 IF ((NOT(start)) = '1') THEN state <= "001"; ELSE state <= "000"; END IF; WHEN "001" =>--计时状态 IF ((NOT(stop)) = '1') THEN state <= "010"; ELSE state <= "001"; END IF; WHEN "010" =>--暂停状态 IF ((NOT(start)) = '1') THEN state <= "001"; ELSE state <= "010"; END IF; WHEN OTHERS => END CASE; END IF; END IF; END PROCESS; PROCESS (clk_50M) BEGIN IF (clk_50M'EVENT AND clk_50M = '1') THEN IF (state = "011") THEN minute_cnt <= "00000000"; ELSIF (state = "001" AND clk_100Hz = '1') THEN--计时状态 IF (Millisecond_cnt = "01100011" AND second_cnt = "00111011") THEN--59秒99‘时向前记1分 IF (minute_cnt < "00111011") THEN minute_cnt <= minute_cnt + "00000001";--计时到990ms,下一次就到1秒了 ELSE minute_cnt <= "00000000"; END IF; ELSE minute_cnt <= minute_cnt; END IF; END IF; END IF; END PROCESS; PROCESS (clk_50M) BEGIN IF (clk_50M'EVENT AND clk_50M = '1') THEN IF (state = "011") THEN--复位状态 second_cnt <= "00000000"; ELSIF (state = "001" AND clk_100Hz = '1') THEN--计时状态 IF (Millisecond_cnt = "01100011") THEN--990ms时向前记1秒 IF (second_cnt < "00111011") THEN second_cnt <= second_cnt + "00000001";--计时到990ms,下一次就到1秒了 ELSE second_cnt <= "00000000"; END IF; ELSE second_cnt <= second_cnt; END IF; END IF; END IF; END PROCESS; PROCESS (clk_50M) BEGIN IF (clk_50M'EVENT AND clk_50M = '1') THEN IF (state = "011") THEN--复位状态 Millisecond_cnt <= "00000000"; ELSIF (state = "001" AND clk_100Hz = '1') THEN--计时状态 IF (Millisecond_cnt < "01100011") THEN--计时到990ms,下一次就到1秒了 Millisecond_cnt <= Millisecond_cnt + "00000001"; ELSE Millisecond_cnt <= "00000000";--计时到990ms,下一次就到1秒了 END IF; END IF; END IF; END PROCESS; Millisecond <= Millisecond_cnt; second <= second_cnt; minute <= minute_cnt; END trans;

设计文档:

设计文档.doc

设计文档2.doc

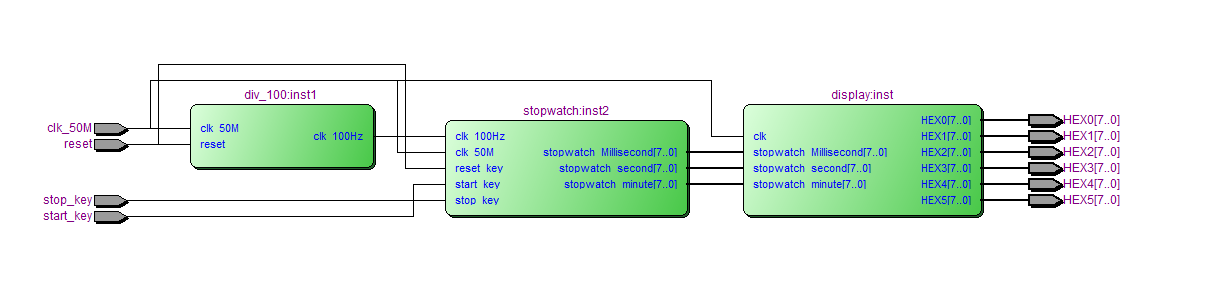

1. 工程文件

2. 程序文件

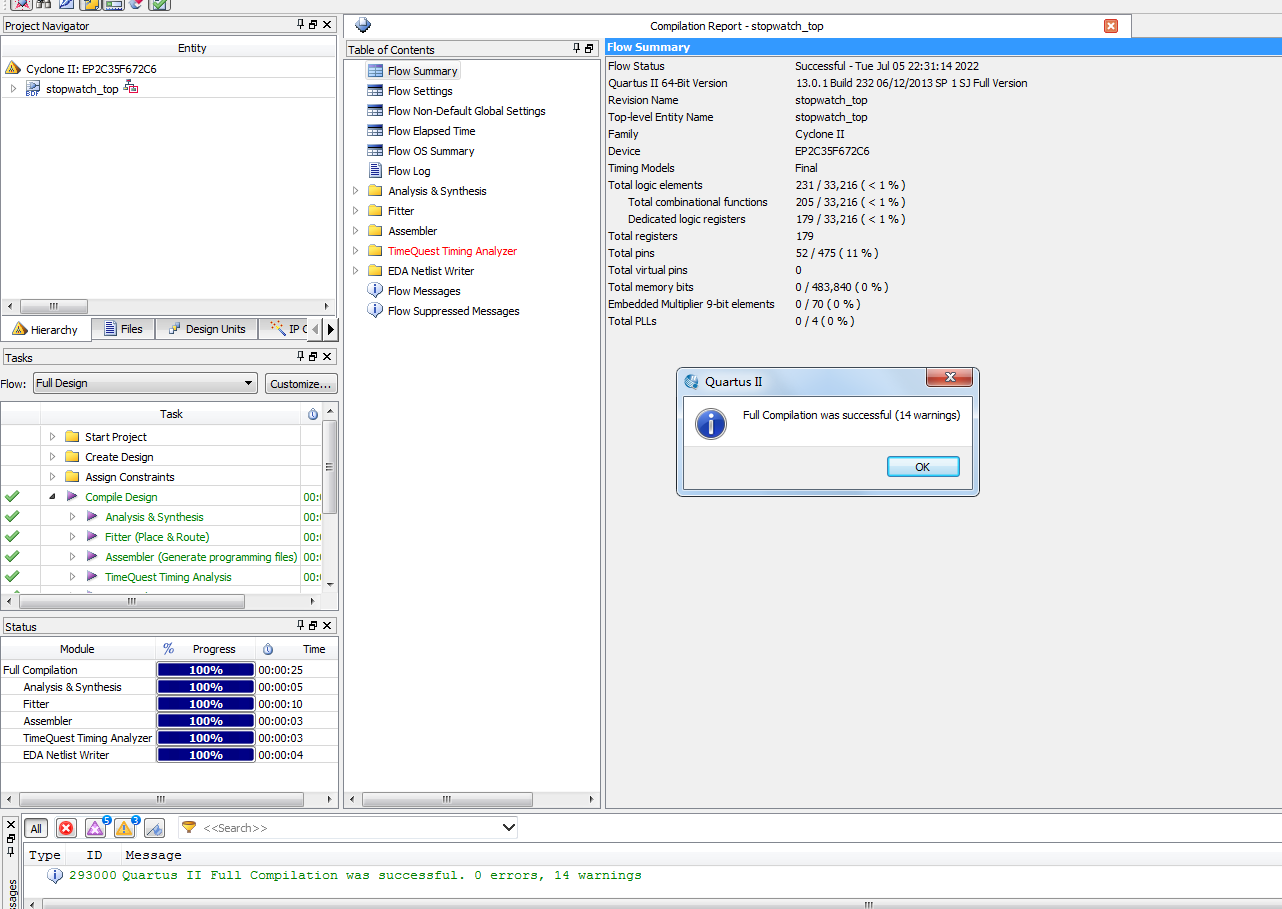

3. 程序编译

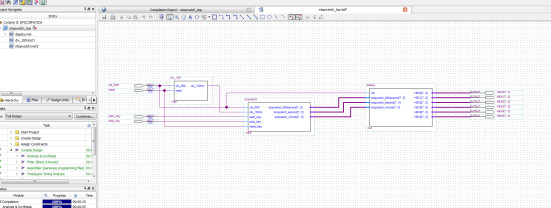

4. RTL图

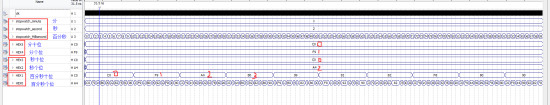

5. 仿真图

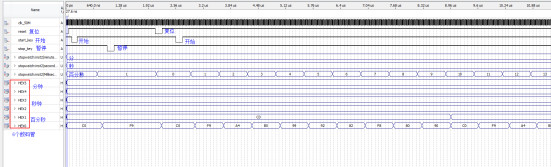

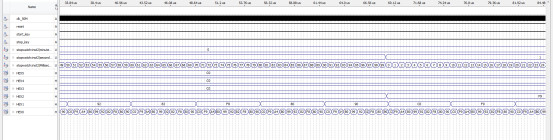

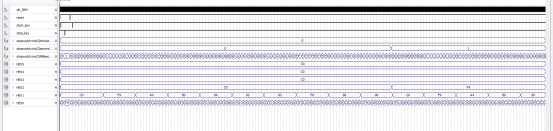

整体仿真图

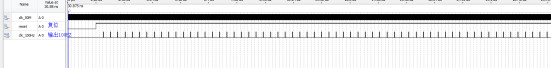

分频模块

控制模块

显示模块