文章目录

- 概述

- 1.1 A720 Features

- 1.1.1 core features

- 1.1.2 Cache features

- 1.1.3 Debug features

- 1.2 A720 组件介绍

- 1.2.1 L1 缓存系统

- 1.2.2 指令解码

- 1.2.3 寄存器重命名

- 1.2.4 指令分发单元

- 1.2.5 向量执行单元

- 1.2.6 加解密扩展单元

- 1.2.6.1 有限域算法

- 1.3 接口

- 1.4 GIC CPU Interface

- 1.5 System Control

- 1.6 Debug

- 1.7 Performance Monitors Extension

概述

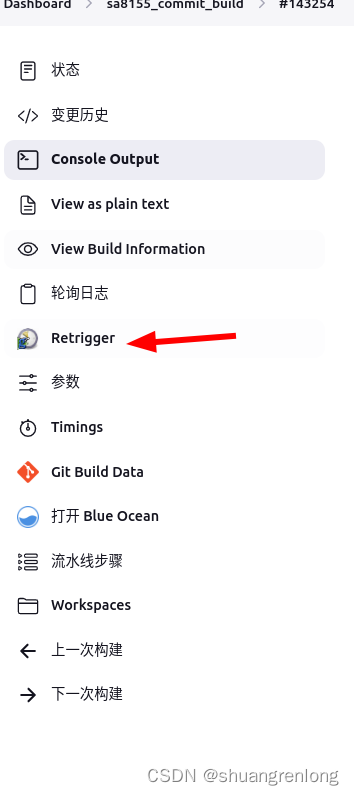

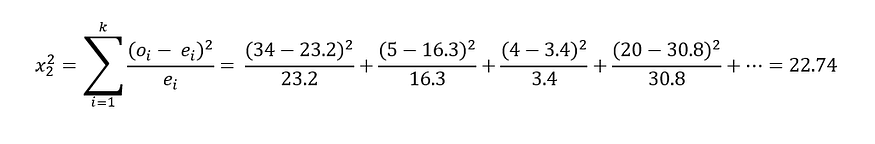

Cortex-A720 是基于 DSU-120 实现的,下图显示了A720的实现配置图:

1.1 A720 Features

1.1.1 core features

- 基于 ArmV9.2-A A64 指令集实现;

- 包含MMU;

- 40位的物理地址宽度,48位的虚拟地址宽度;

- GIC(Generic Interrupt Controller);

- 通用时钟接口,支持64位的counter计数器;

- 支持 RSA Extension(Reliability, Availability, and Serviceability);

- 支持 Scalable Vector Extension (SVE) ;

- 支持 SIM 和 浮点运算;

- 支持 AMU(Activity Monitoring Unit);

- 支持加解密引擎。

1.1.2 Cache features

- L1 的 指令cache和数据cache分开,L1 指令cache size 可选:32KB or 64KB,数据cache可选:32KB or 64KB;

- L2 Cache; L2 Cache 的配置大小可选:128KB, 256KB, or 512KB;

- 支持 MAPM(Memory System Resource Partitioning and Monitoring)。

1.1.3 Debug features

- 支持 Armv9,2 的 debug 逻辑;

- 支持 PMU,PMU支持的event conuter 个数可配置范围:6 或者20个;

- 支持 ETE(Embedded Trace Extension );

- 支持 TRBE(TRace Buffer Extension);

- 可选项 SPE (Statistical Profiling Extension )功能;

- 可选项 ELA-600功能。

1.2 A720 组件介绍

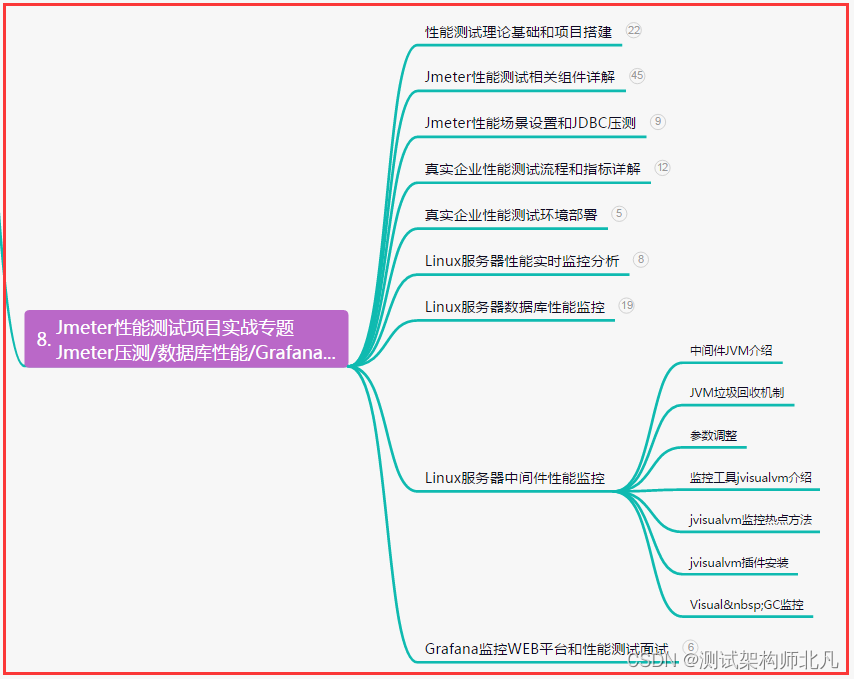

下图是 A720 内部组件图:

主要包含以下内容:

- L1 instruction and L1 data memory systems

- L2 memory system

- Register rename,寄存器重命名

- Instruction decode,指令解码

- Instruction issue,指令分发

- Execution pipeline,执行流水线,主要是做一些向量运算,

- Memory Management Unit (MMU)

- Trace unit and trace buffer

- Performance Monitoring Unit (PMU)

- Activity Monitoring Unit (AMU): 它的主要功能是提供一种机制来测量处理器的运行活动。

AMU 通过收集和存储关于处理器执行的指令和内存访问的详细信息,使得开发者可以更好地理解和优化软件在硬件上的性能。这些信息可能包括执行的指令数、缓存命中和未命中的数目、分支预测的准确性等等。

在某些场景下,AMU 的信息还可以用来进行能耗分析和优化。比如,通过比较不同的软件版本或者算法实现在处理器上运行的效率,开发者可以找到并解决可能的性能瓶颈,进一步减少能耗。 - Generic Interrupt Controller (GIC) CPU interface

- Branch prediction,分支预测

A720 通过 CPU Bridge 与 DSU-120 连接, DSU-120再与与外部存储及SOC上其它项连接

1.2.1 L1 缓存系统

主要是从指令cache中拿去指令然后发送到指令解码单元。

L1 缓存系统主要包括:

- 4路组相连,大小可配置为32K或者64K, cacheline 64bytes

- L1 指令 TLB,大小可以配置为 16K, 64K, 2M

- 动态分支预测

1.2.2 指令解码

解码单元将AArch64 架构的指令解码成CPU内部格式,然后发送到执行单元。

1.2.3 寄存器重命名

该功能主要是通过寄存器重命令来加速乱序执行和分发解码后的指令到对应的发射通道。

1.2.4 指令分发单元

控制何时将解码后的指令发送到执行管道,它包含分发队里用于暂存解码后的指令。

1.2.5 向量执行单元

主要用于执行 SVE 和 SEV2 指令,也可以执行加解密指令。

SVE,全名Scalable Vector Extension,是ARM在ARMv8-A架构中引入的一种向量扩展。SVE提供了一种新的处理向量数据的方法,使得在处理大规模并行任务时能够更加高效。SVE的一大特点是其向量寄存器的长度是可伸缩的,可以最大达到2048位。

SVE2是在SVE基础上的进一步扩展,加入了对复杂整数和浮点数运算的支持,以及对通信和密码学应用的支持。SVE2是ARMv9架构中的一个重要特性。

1.2.6 加解密扩展单元

- 支持 AES 加解密;

- 支持 SHA-1,SHA-2,SHA-3 哈希算法;

- 支持 SM3 hash 功能和 SM4 hash 功能;在讨论这个问题之前,需要先明确一点,SM3和SM4是密码算法,而不是哈希算法。SM3是一种消息摘要算法,SM4是一种分组密码算法,它们都是由中国的国家密码管理局发布的。在硬件级别上,ARMv9能够更快更安全地执行这两种算法。这对于一些需要执行大量这类加密运算的场景(如网络安全、数据保护等)非常有利。

SM3是一种消息摘要算法,常用于数字签名、消息认证码等密码学应用中,它的输出是一个固定长度(512位)的“摘要”,任何微小的输入变化都会导致输出摘要的巨大变化,使得攻击者无法通过摘要反推出原始输入信息。

SM4是一种分组密码算法,用于数据的加密和解密。SM4使用的密钥长度为128位,分组长度为128位,采用了分组密码中常见的Feistel结构,是对称密码算法,即加密和解密使用的是同一个密钥。 - 支持有限域算法,用于支持Galois/Counter Mode 和 Elliptic Curve加解密, Galois/Counter Mode (GCM) 是一种块密码模式,它可以提供数据的加密和认证,常常用于保护网络数据。GCM 结合了 Galois 模式的消息认证码(GMAC)和计数器模式(CTR)的加密方式,可以同时进行加密和认证操作。

1.2.6.1 有限域算法

有限域算法,又称有限字段算法,是指在有限域(Finite Field)或者称伽罗华域(Galois Field)上进行的运算规则和算法。

有限域是由有限个元素组成的代数结构,满足加法、乘法、减法和除法四则运算的封闭性、结合律、交换律、分配律,并且乘法和加法操作都有单位元素和逆元素。

在有限域上的算法主要包括有限域上的加法、乘法、求逆等基本运算,以及更高级的多项式运算、矩阵运算、求解线性方程组等。

有限域算法在密码学、编码理论、线性代数、数字信号处理等领域都有广泛应用。例如,在密码学中,AES(高级加密标准)就是在有限域上进行运算的。在编码理论中,Reed-Solomon编码也是建立在有限域上的。

1.3 接口

1.4 GIC CPU Interface

TODO

1.5 System Control

TODO

1.6 Debug

TODO

1.7 Performance Monitors Extension

TODO

![红队专题-从零开始VC++C/S远程控制软件RAT-MFC-[5]客户端与服务端连接](https://img-blog.csdnimg.cn/69bda4c6158d412abc7a503189f78fe8.png)

![2023年中国熔盐储能装机量、新增装机量及行业投资规模分析[图]](https://img-blog.csdnimg.cn/img_convert/ca455f9baba4380fb2304ab6ec63852e.png)