先补充一下算术移位寄存器和按位移位寄存器:

SystemVerilog具有按位和算术移位运算符。

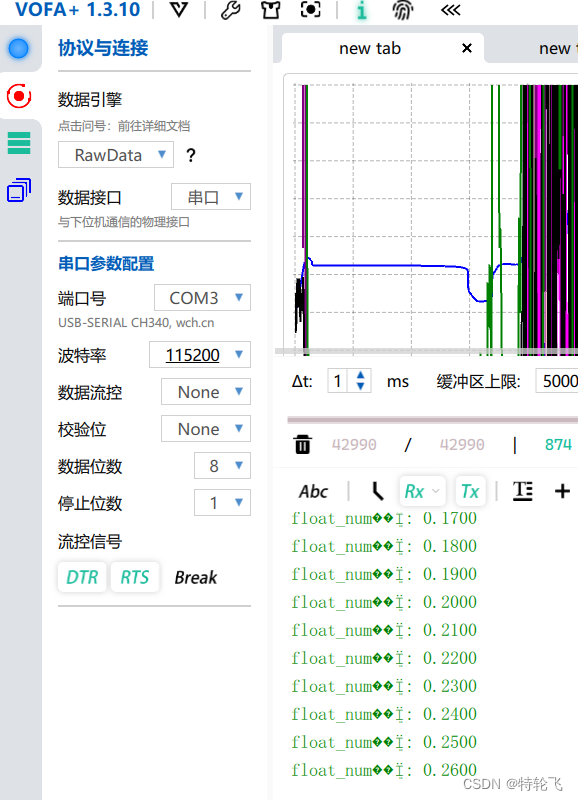

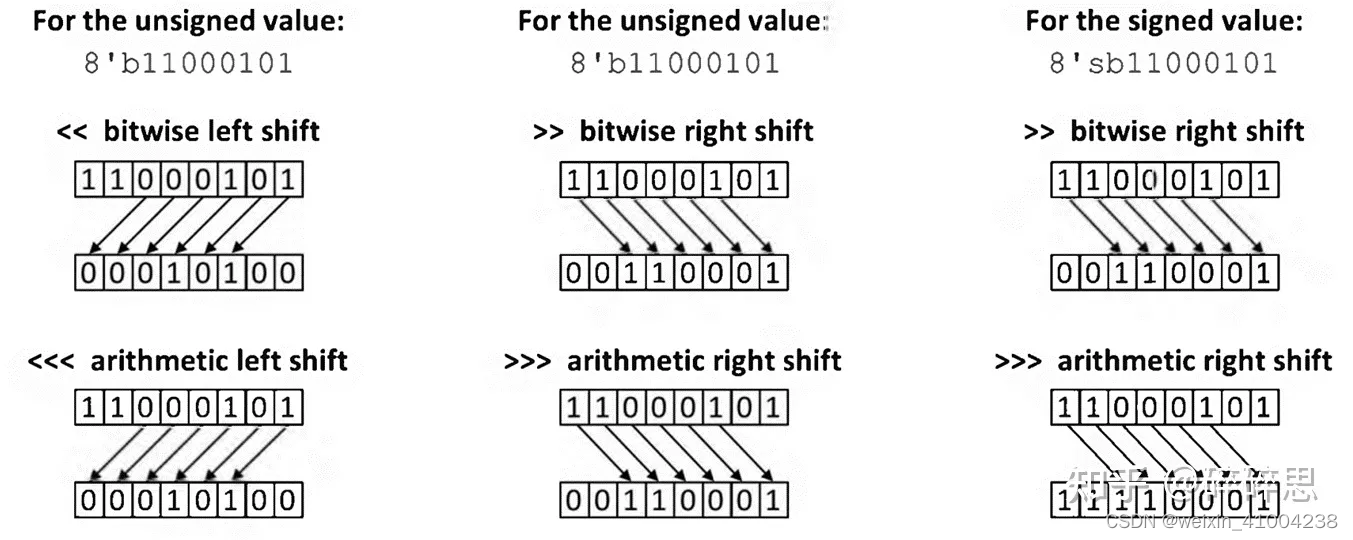

按位移位只是将向量的位向右或向左移动指定的次数,移出向量的位丢失。移入的新位是零填充的。例如,操作8’b11000101 << 2将产生值8’b00010100。按位移位将执行相同的操作,无论被移位的值是有符号的还是无符号的。

算术左移位对有符号和无符号表达式执行与按位右移位相同的操作。算术右移位对“无符号”和“有符号”表达式执行不同的运算。如果要移位的表达式是无符号的,算术右移位的行为与按位右移相同,即用零填充输入位。如果表达式是有符号的,则算术右移将通过用符号位的值填充每个输入位来保持值的有符号性。

注意:有符号数的算术右移比较特殊,最右边补的位是符号位的值!

注意:有符号数的算术右移比较特殊,最右边补的位是符号位的值!

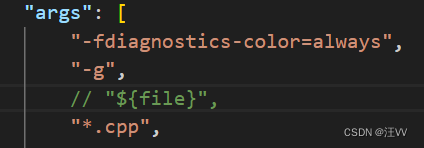

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always@(posedge clk)

if(load)

q <= data;

else if(ena)

case (amount)

2'b00: q <= q << 1 ;

2'b01: q <= q << 8 ;

2'b10: q <= {q[63],q[63:1]};

2'b11: q <= {{8{q[63]}},q[63:8]} ;

endcase

endmodule