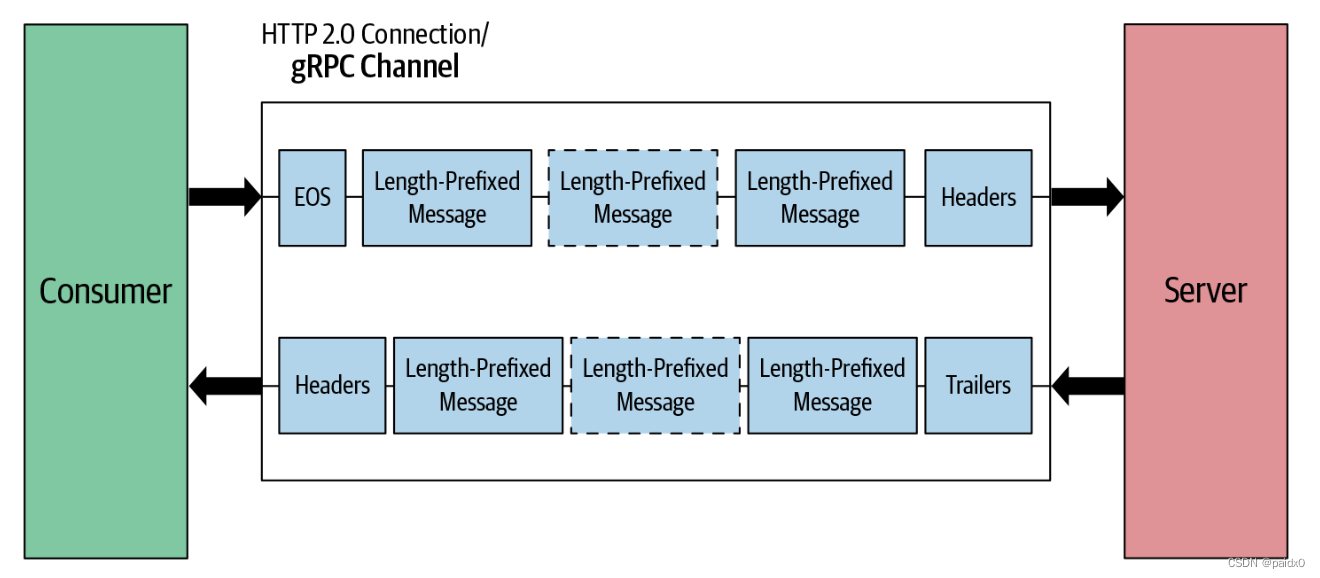

graybox功能简化了分层设计中的扫描插入和ATPG处理过程,允许对子模块执行扫描和ATPG操作,然后允许在以下情况下使用该子模块的简化灰箱表示在下一个更高层次执行扫描和ATPG操作。由于子模块的灰盒表示仅包含最小数量的互连电路,因此在大型分层设计中使用灰盒可以显著减少执行扫描插入、优化时序、分析故障和创建测试模式所需的内存和工具运行时间。

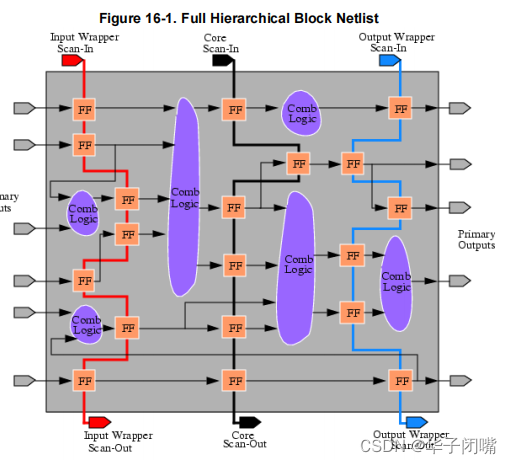

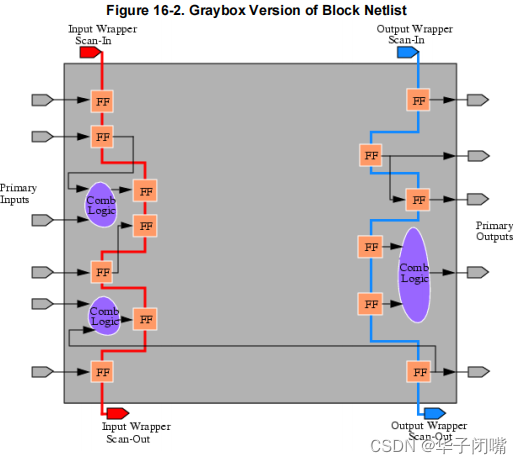

为了理解子模块的灰盒表示,首先考虑图16-1所示的完整网表表示。该图显示了输入和输出包装器链、核心扫描链以及包装器链内外的组合逻辑。在为该子模块执行扫描插入、故障统计和模式创建之后,您将创建子模块的灰色框表示,如图16-2所示。

图16-2是图16-1所示子模块的灰盒表示。注意,灰盒仅包含主输入/输出、包装链和包装链外部的组合逻辑(即,主输入或输出与最近连接的触发器之间的任何组合逻辑)。

1.定义外部模式中使用的时钟引脚(使用add_clocks命令)。

2.约束将电路置于外部模式的测试控制引脚(使用add_input_constrats命令)。

3.定义包装链(使用add_scan_chains命令)。

4.使用测试程序文件将电路置于外部模式。该测试程序文件应执行以下操作:

o定义外部模式的测试设置程序,以强制启用信号路径的主输入到包装单元。

o定义移位和加载卸载程序,以强制包装链扫描启用信号,并切换外部模式的移位时钟。可能还需要其他类型的扫描和时钟程序(如主观察或阴影观察)和非扫描程序(如捕获),以确保电路在外部模式下正确运行。

5.使用analyze_graybox命令标识灰盒逻辑。该命令还显示一个摘要,以指示分析所识别的组合逻辑门和顺序逻辑门。该工具通过设置其“in_graybox”属性来标记已识别的灰盒实例。通过使用set_attribute_value命令启用/禁用此属性,还可以在灰箱网表中包含其他实例(或从灰箱网列表中排除特定实例)。灰盒分析通过从所有主输出引脚和包装链向后追踪来执行识别。然而,芯链的扫描输出引脚被排除在反向跟踪之外。由于核心链不是用add_scan_chains命令定义的,因此可以通过使用set_attribute_value命令设置扫描引脚的ignore_for_graybox属性来实现这一点。

6.“write_design-graybox”命令将写出用in_graybox属性标记的所有实例。该工具取消了灰箱网表中包含的所有模块(顶部模块除外),保留未验证模块的接口(端口声明)。

当使用“set_wrapper_chains-wrapper_extest_ports”命令插入包装链时,Tessent Scan会将这些端口插入到块中。通过将全局信号wrapper_extest约束为逻辑1来激活包装器外部端口。通过在执行灰盒分析之前使用ignore_for_graybox属性标记EDT通道输出,EDT逻辑和随后的核心逻辑被排除在灰盒网表之外。

EDT逻辑的插入方式使得通道I/O引脚的排他子集仅用于包装链。这允许通过使用ignore_for_graybox属性标记核心链EDT通道输出,从灰箱网表中排除核心逻辑。如果分配给包装器链的信道输出上的sequential pipeline stages的深度小于2,则灰箱分析可以识别对外部敏感的EDT逻辑。然而,在本示例中,EDT块被指定为保留实例,以将其完全包含在灰箱网表中。

通道I/O引脚上的任何顺序流水线级都将包含在灰箱网表中。以下示例dofile显示了在灰箱分析中使用EDT取景器的典型设置。为核心链分配的EDT通道引脚被限制/屏蔽,以便EDT查找器忽略。然而,当为包装和核心链插入单独的EDT块时,这通常是有效的。

由Tessand Shell提供,其设计满足ATPG, Logic BIST, EDT, and Low Pin Count Test.。

•ATPG对每个时钟域进行独立控制,以提高覆盖率,减少pattern计数,并在用户干预最少的情况下实现安全计时。

•在捕获期间,根据每个pattern提供正确数量的时钟脉冲。

•在移位和捕获时钟之间进行正确切换。

•在捕获期间启用慢速或快速时钟,以应用慢速和高速模式。

•在包芯内生成的扫描可编程时钟波形是在芯层生成pattern的理想选择。这些pattern可以重新定位到顶层并合并,以同时测试多个内核,而不会在每个内核内控制时钟的方式上发生冲突。

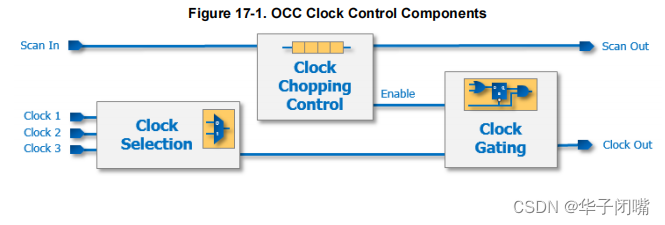

You can use the Tessent OCC with the following:

•时钟选择

o选择使用的始终捕获或始终脉冲时钟。

o根据频率、测试类型和其他标准选择时钟。

•Clock Chopping Control

o扫描可编程移位寄存器控制时钟脉冲抑制。

o为时钟门控创建启用信号。

•Clock Gating

oGates clock based upon clock chopping enable signal

默认情况下,Tessent OCC包含一个内部时钟门控器。此选项可以在生成步骤中禁用。当设计已经包含时钟门控器时,可以用时钟使能信号生成Tessent OCC。 当使用具有时钟启用功能的Tessent OCC时,该工具检测OCC控制的时钟门控单元。此过程是自动的,不需要用户输入。为了能够正确检测OCC控制的时钟门控单元,需要在单元库中使用适当的模拟功能对单元进行适当建模。

![[思维模式-9]:《如何系统思考》-5- 认识篇 - 改变开环、组合逻辑的线性思考,实施闭环、时序逻辑的动态思考。](https://img-blog.csdnimg.cn/df87183378194fef920384ccdade9c9c.png)