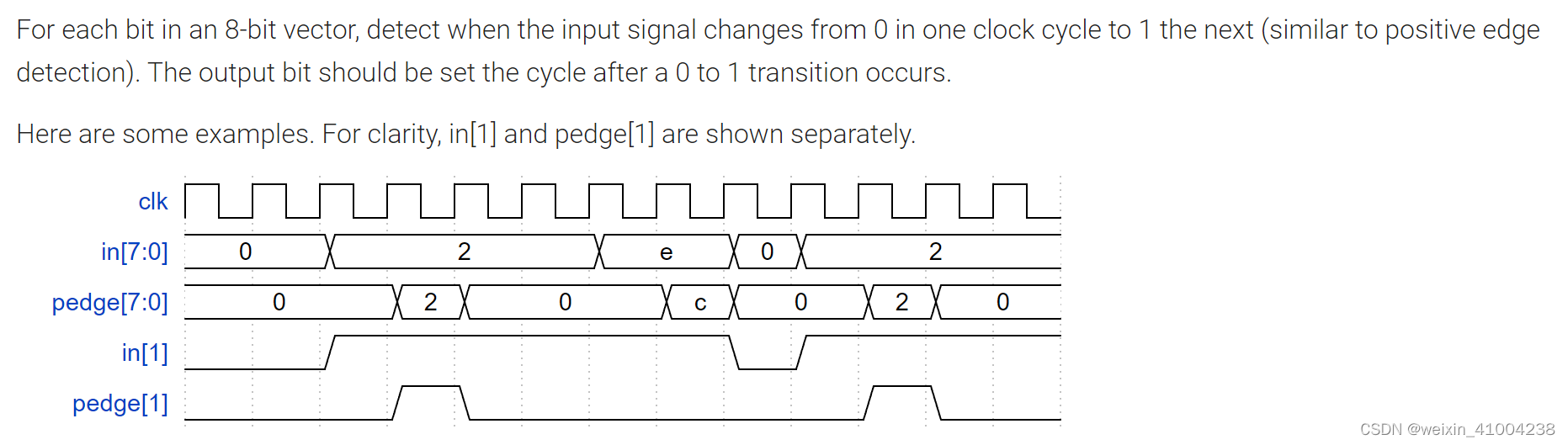

module top_module (

input clk,

input [7:0] in,

output [7:0] pedge

);

reg [7:0] in_old;

always@(posedge clk)

begin

in_old <= in;

end

assign pedge <= in & ~in_old;

endmodule对于边缘检测而言,若是0→1和1→0都检测则为in^in_old;若只检测0→1则为in&~in_old;若是只检测1→0则为!in&in_old。