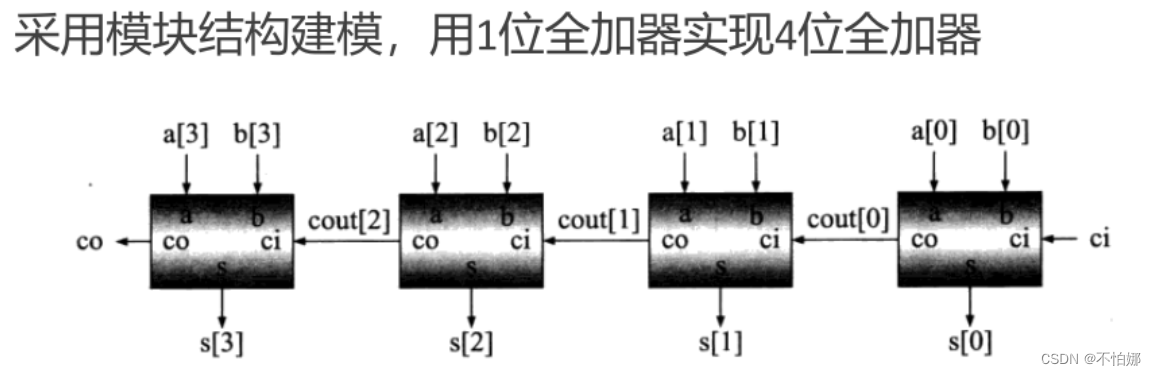

题目要求:

采用模块结构建模,实例化四个1位全加器并连线,完成图示的四位全加器建模并编写四位全加器测试模块,在modelsim里执行,查看波形图。

-

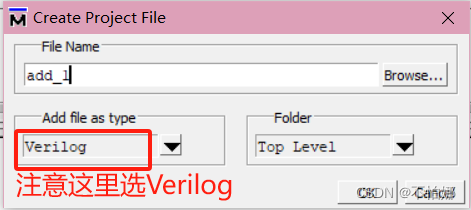

首先,在工程区右键选择创建一个新文件去实现1位全加器的功能。在这里我创建的文件叫add_1:

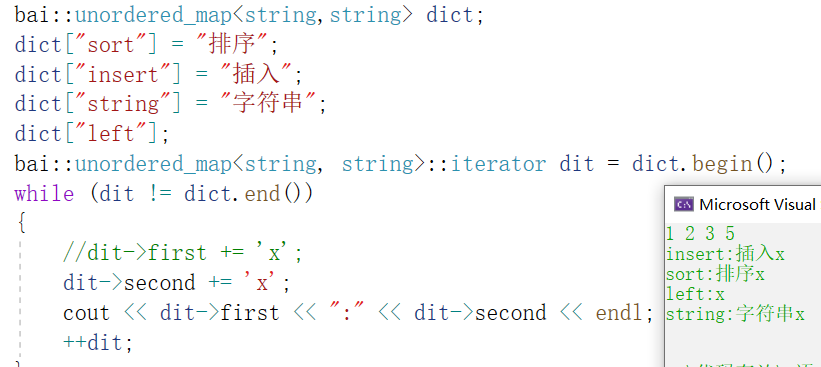

在文件中添加如下代码:

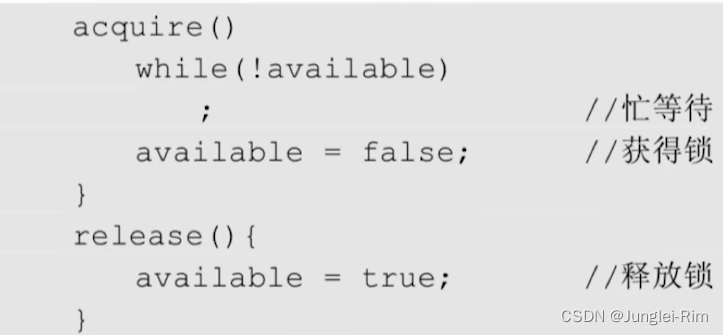

module add_1(a,b,ci,co,s); input a,b,ci; output co,s; assign{co,s}=a+b+ci; endmodule注意要保存文件,可以按 Ctrl + s 键来保存。

-

然后同样的步骤再添加一个文件用于实现4位全加器。这里我创建的文件叫fuadder4。

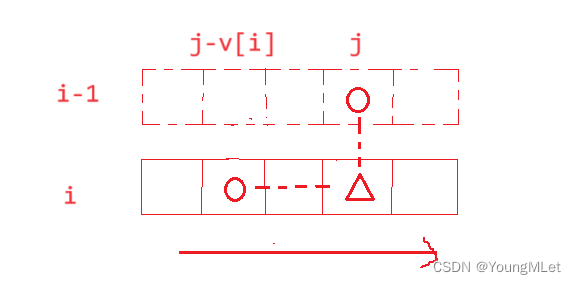

在文件中添加如下代码:module fuadder4(a,b,ci,co,s); input [3:0] a,b; input ci; output co; output [3:0] s; wire [2:0] count; add_1 U1(a[0],b[0],ci,count[0],s[0]); add_1 U2(a[1],b[1],count[0],count[1],s[1]); add_1 U3(a[2],b[2],count[1],count[2],s[2]); add_1 U4(a[3],b[3],count[2],co,s[3]); endmodule注意要保存文件

-

接下来同样的步骤创建一个文件用于测试4位全加器。这里我创建的文件叫fuadder4_tb。

在文件中添加如下代码:module fuadder4_tb; reg [3:0] a,b; reg ci; wire co; wire [3:0] s; always #20 ci = ~ci; initial begin a = 4'b0000; b = 4'b0000; ci = 0; repeat(16) #20 a = a + 1; end initial begin a = 4'b0000; b = 4'b0000; ci = 0; repeat(16) #20 b = b + 1; end fuadder4 uut(a,b,ci,co,s); endmodule注意要保存文件

-

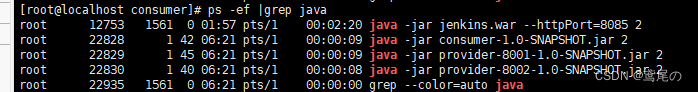

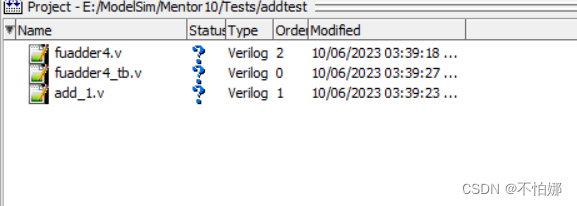

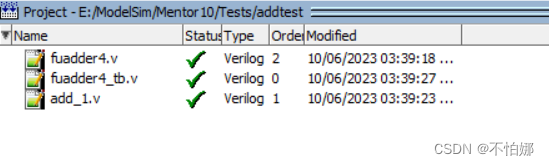

到此为止,我们一共创建了三个文件,分别实现了1位全加器、四位全加器和四位全加器测试代码。现在工程区显示应该如下所示:

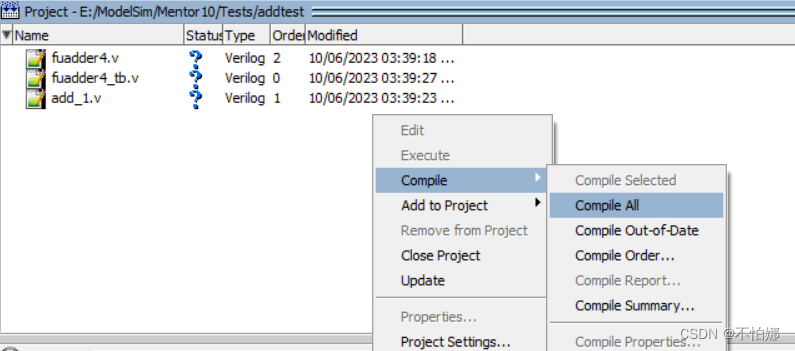

然后右键选择编译所有文件:

编译成功后显示如下,可以看见问号都变成了对号。

-

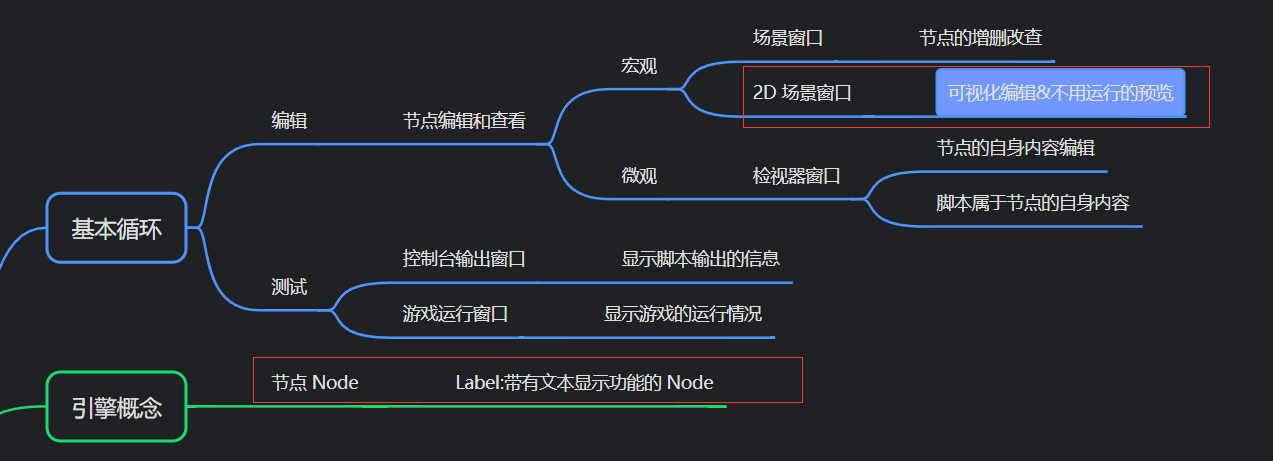

最后我们来进行仿真。

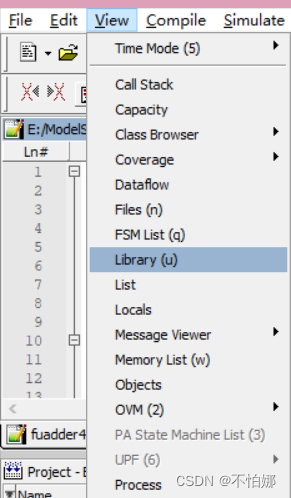

看旁边的Library区。如果没有,就点击View勾上Library。

如下所示:

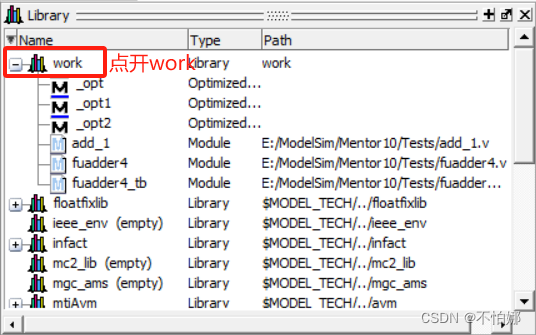

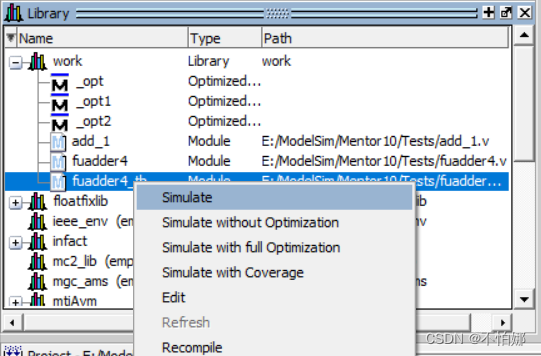

然后在work里面可以看见我们之前创建的三个文件。然后右键测试文件,也就是fuadder4_tb,选择Simulate:

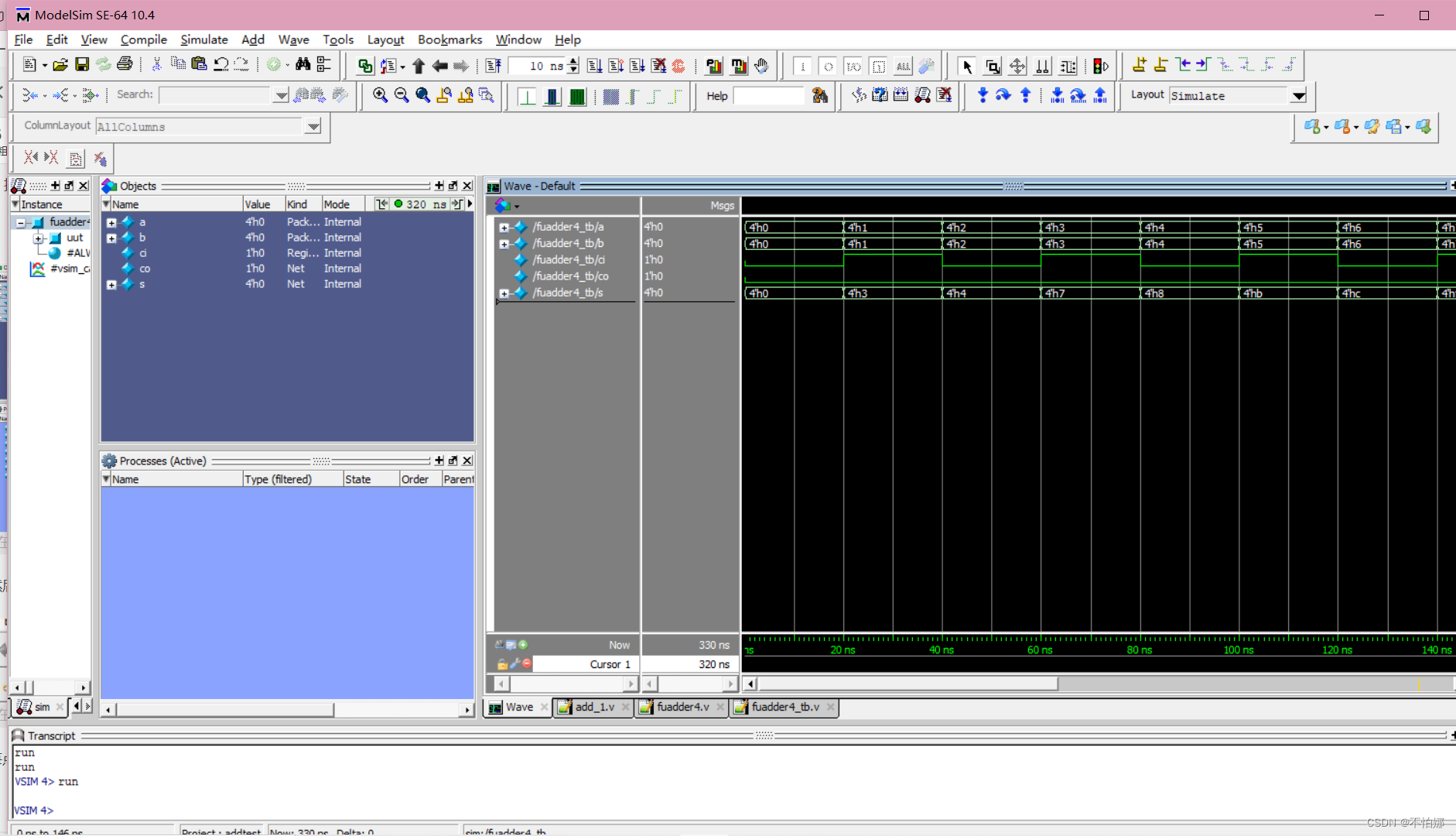

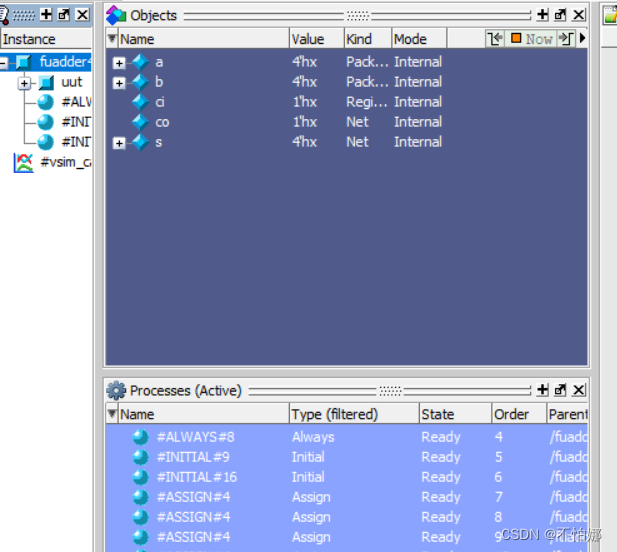

然后就可以看见这个窗口:

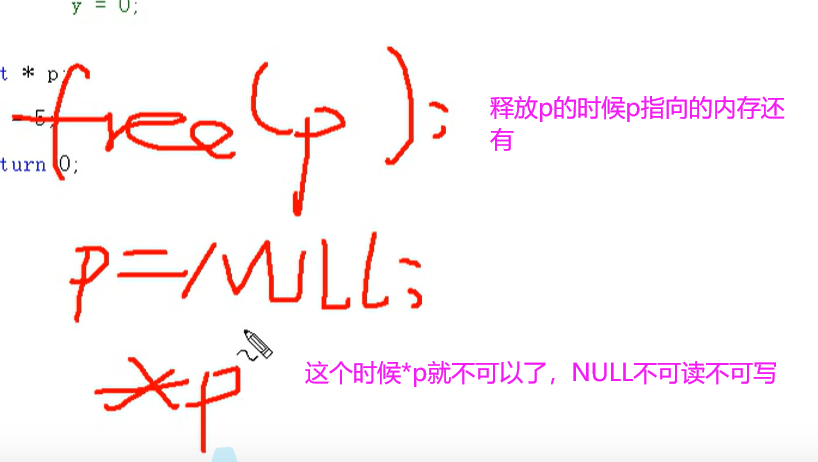

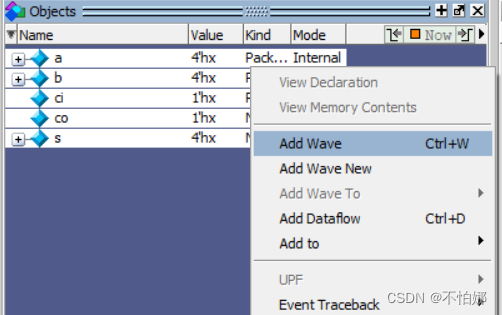

我们按住ctrl键选中想要显示的参数,然后右键选择添加波形。这里我全选了:

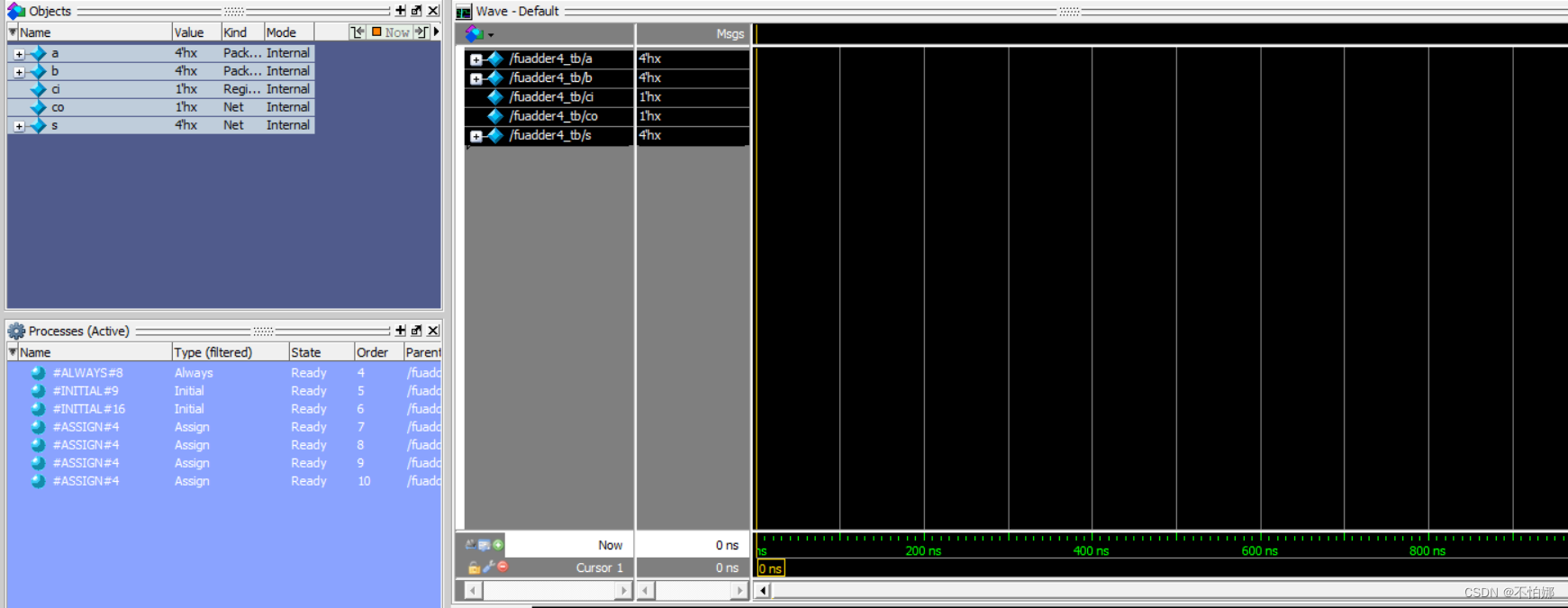

接着就会出现一个这样的界面,但是现在还没有波形:

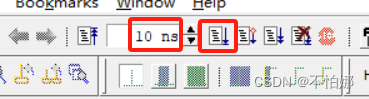

然后设置时间,启动示波器,这里我设置的是10ns,然后点击右边的选项启动:

每点一次就会执行一次,可以将时间设置的长一些,然后多点击几次就可以看到波形图了: