目录

- 一、简介

- 二、具体内容

- 2.1 APB

- 2.2 AHB

- 2.3 AXI

- 三、总线对比

- 3.1 总体对比

- 3.2 部分功能差异

- 四、其他相关链接

- 1、PCI总线及发展历程总结

- 2、SPI协议详细总结附实例图文讲解通信过程

- 3、I2C总线内容总结分享

一、简介

本文主要介绍APB、AHB和AXI总线的相关内容,同时对比三种总线的差异,附图和应用场景方便读者快速掌握。

二、具体内容

AMBA总线的系统架构:其中APB总线是AHB总线的扩展,方便外设连接到系统总线上,AHB和APB之间有一个转接桥来进行连接。

对于AMBA协议,APB的信号都是以P开头,AHB的信号都是以H开头,而AXI的信号都是以A开头。

2.1 APB

APB的全称为Advanced Peripheral Bus高级外围总线,是一种优化的,低功耗的,精简接口总线,可以技术多种不同慢速外设;主要应用在低带宽的外设上,如UART、 I2C和SPI,除了连接低速外设之外,APB总线还广泛用于配置各种IP的寄存器(这些IP预留用户控制信号,由软件进行配置,这个时候就可以选择使用APB总线来配置这些寄存器)。

APB协议不支持流水线设计,它主要应用在低带宽设计需求的接口中,高性能带宽需求可以使用AXI总线。APB协议的实现与时钟沿对齐,以简化外设接口的设计。每次传输至少需要消耗两个时钟周期。

总结特点如下:

1、低成本;

2、低功耗;

3、低带宽;

4、无流水线结构;

5、所有信号的跳变仅与时钟上升沿相关;

6、每次传输至少需要两个时钟周期。

2.2 AHB

AHB (Advanced High-performance Bus) 高级高性能总线,用于高性能、高时钟频率的系统模块,典型的应用如ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。

AHB总线强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线控制器,以及各种AHB接口的控制器等连接起来构成一个独立的完整SOC系统,还可以通过AHB-APB桥来连接APB总线系统。

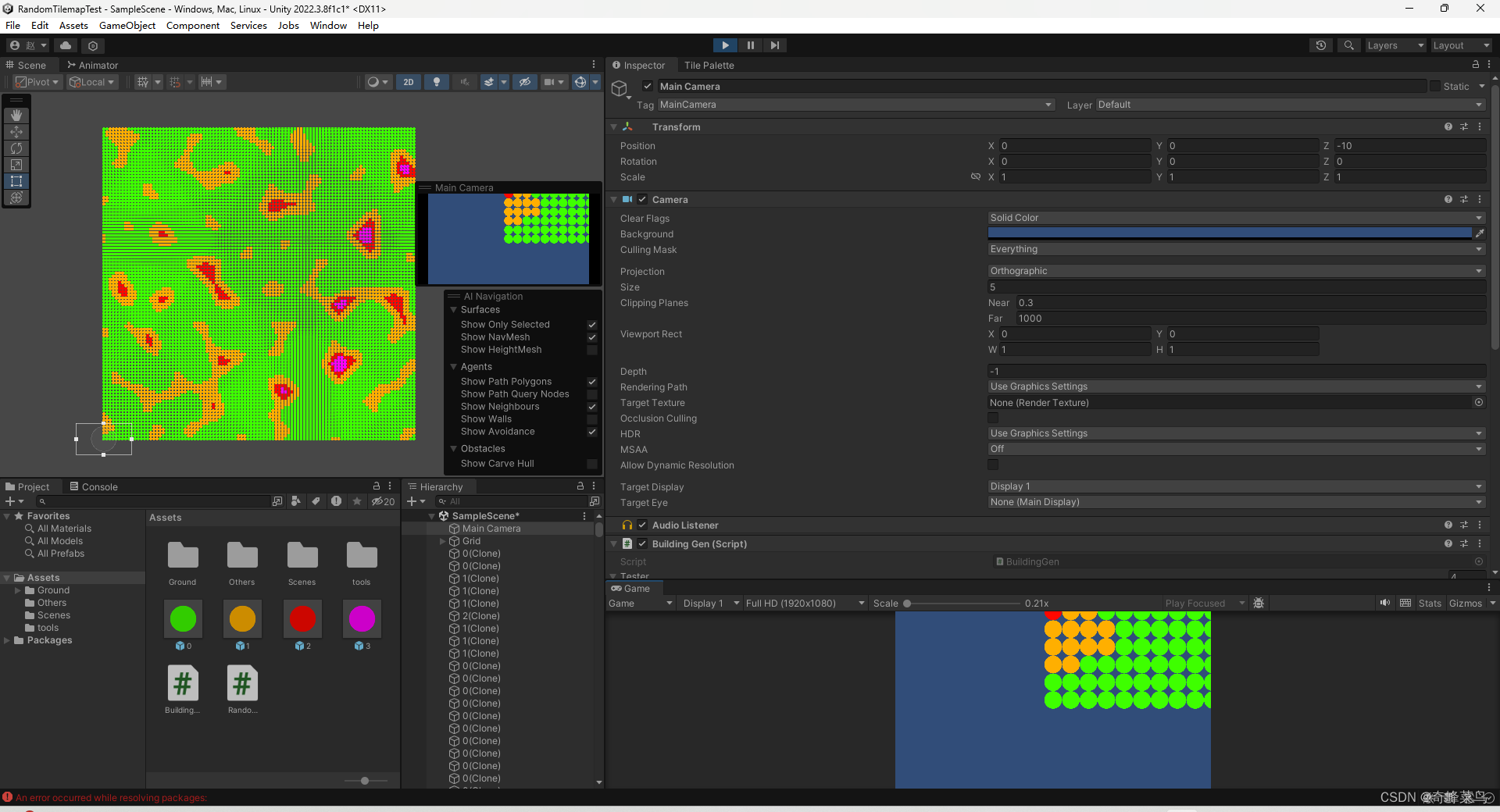

AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。基础结构则由仲裁器(arbiter)、主模块到从模块的Mux、从模块到主模块的Mux、译码器(decoder)、虚拟从模块(dummy Slave)、虚拟主模块(dummy Master)所组成。具体结构如下图所示。

AHB总线具有两级流水操作,包括地址周期和数据周期的两级流水线处理。第一个周期读地址,第二个周期写数据,用流水线操作处理,在第二个周期写数据的同时读另一个地址,这样在下一个周期就可以直接写数据,读地址写数据同时进行,这样两周期的操作在流水线开始后每周期都能写一个数据。

总结特点如下:

1、Burst传输;

2、Split事务处理;

3、单周期master移交;

4、单一时钟沿操作;

5、无三态;

6、更宽的数据总线配置(64/128);

7、流水线操作;

8、可支持多个总线主设备(最多16个)。

2.3 AXI

AXI (Advanced eXtensible Interface) 高级可拓展接口,高速度、高带宽,管道化互联,单向通道,只需要首地址,读写并行,支持乱序,支持非对齐操作,有效支持初始延迟较高的外设,连线非常多。

| AMBA版本 | AXI版本 | ACE版本 |

|---|---|---|

| AMBA3 | AXI3 | \ |

| AMBA4 | AXI4、AXI4-Lite | ACE、ACE-Lite |

| AMBA5 | AXI5、AXI5-Lite | ACE5、ACE5-Lite、ACE5-LiteDVM |

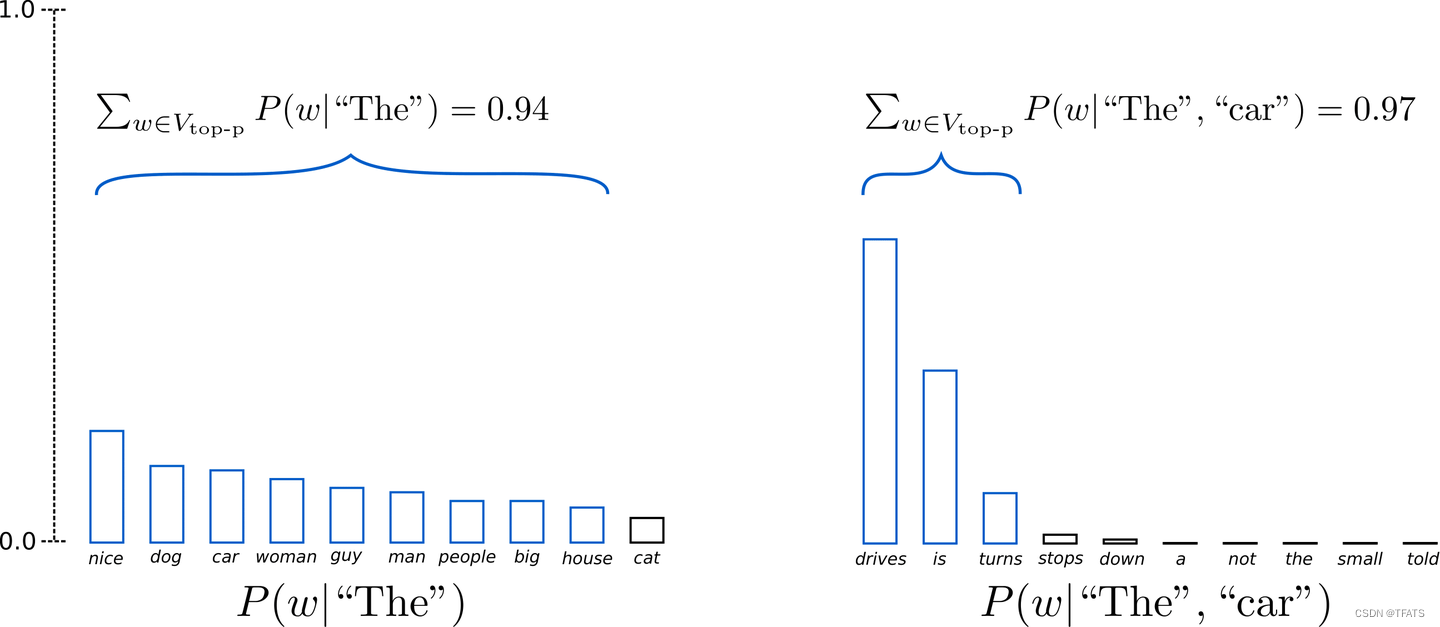

多个master和slave连接在一起构成的典型系统如下:

总结特点如下:

1、地址/控制操作与数据操作分离;

2、使用byte strobes (字节选通) 信号实现非对齐数据传输;

3、使用burst传输 (突发传输) 时只需要发送首地址,便可以发送一段数据读数据和写数据通道独立,从而支持DMA (low-cost Direct Memory Access);

4、支持outstanding功能,可以发送多个地址进行读写;

5、支持out-of-order传输;

6、Permits easy addition of register stages to provide timing closure。

三、总线对比

3.1 总体对比

| 总线 | 功能 | 通道 | 主从设备 | 数据操作 |

|---|---|---|---|---|

| APB | APB是高级外围总线 | 单通道总线,不支持读写并行 | 单主设备多从设备,主设备就是APB桥,不具有仲裁机制 | 不支持 |

| AHB | AHB是先进的高性能总线 | 单通道总线,不支持读写并行 | 多主/从设备,且通过仲裁机制实现总线控制权的分配 | 支持突发传输 |

| AXI | AXI是先进的可扩展接口 | 多通道总线,总共分为五个通道,能够实现读写并行 | 多主/从设备,且通过仲裁机制实现总线控制权的分配; | 支持突发传输,数据非对齐操作 |

3.2 部分功能差异

具体内容详细说明:

1、AHB突发传输与AXI突发传输的区别:

AHB协议需要一次突发传输的所有地址,地址与数据锁定对应关系,后一次突发传输必须在前次传输完成才能进行;

AXI只需要一次突发的首地址,可以连续发送多个突发传输首地址而无需等待前次突发传输完成,并且多个数据可以交错传递,此特征大大提高了总线的利用率;

AHB总线与AXI总线均适用于高性能、高带宽的SoC系统,但AXI具有更好的灵活性,而且能够读写通道并行发送,互不影响;更重要的是,AXI总线支持乱序传输,能够有效地利用总线的带宽,平衡内部系统。因此SoC系统中,均以AXI总线为主总线,通过桥连接AHB总线与APB总线,这样能够增加SoC系统的灵活性,更加合理地把不同特征IP分配到总线上。