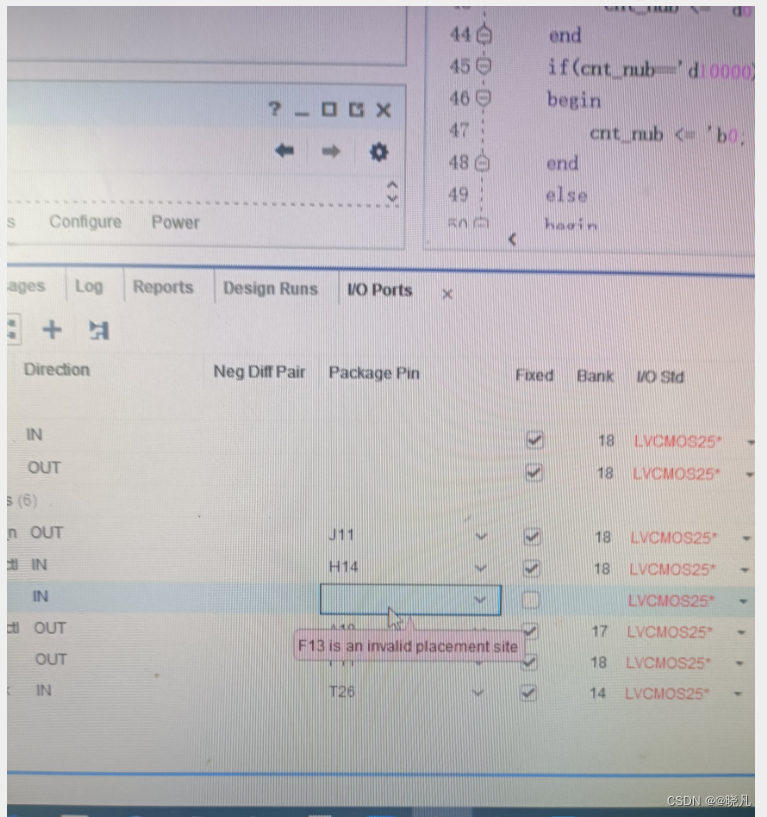

在vivado中绑定引脚时提示:F13 is an invalid placement site

f13引脚在板子上是接千兆网的rxclk端的。在进一步不排查出现这样的问题提示

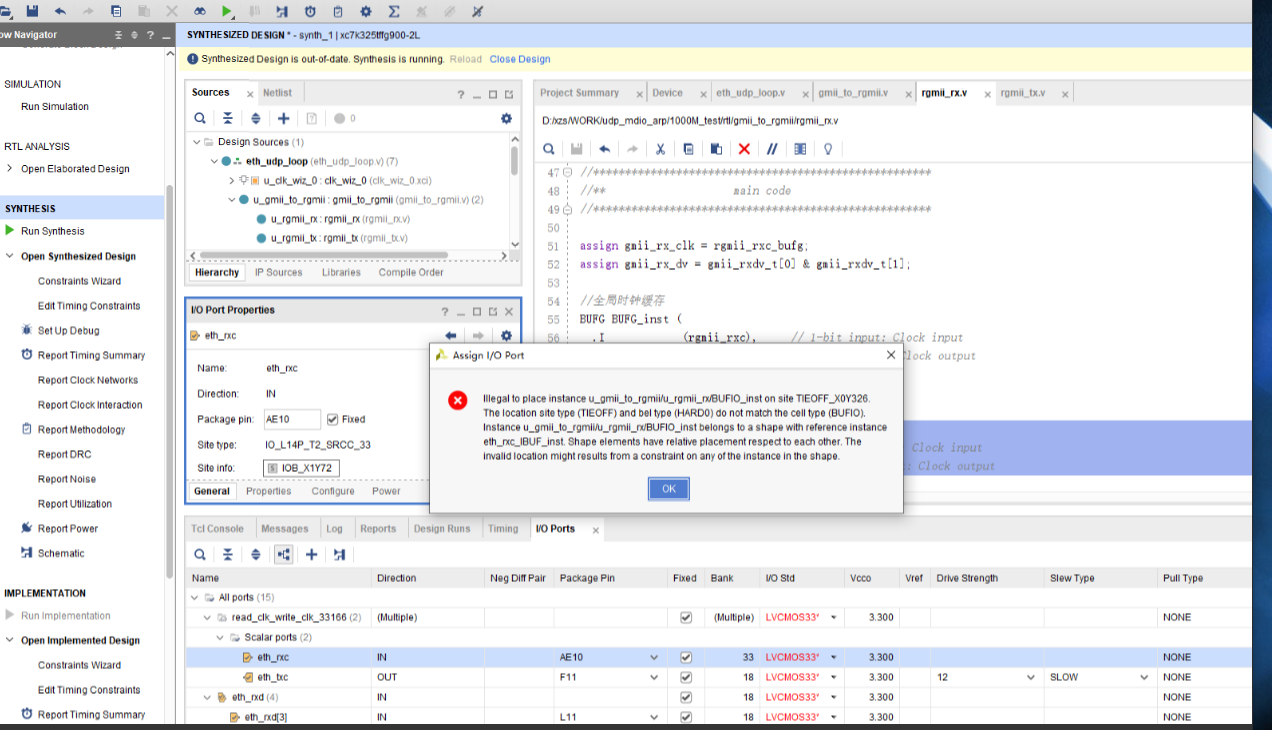

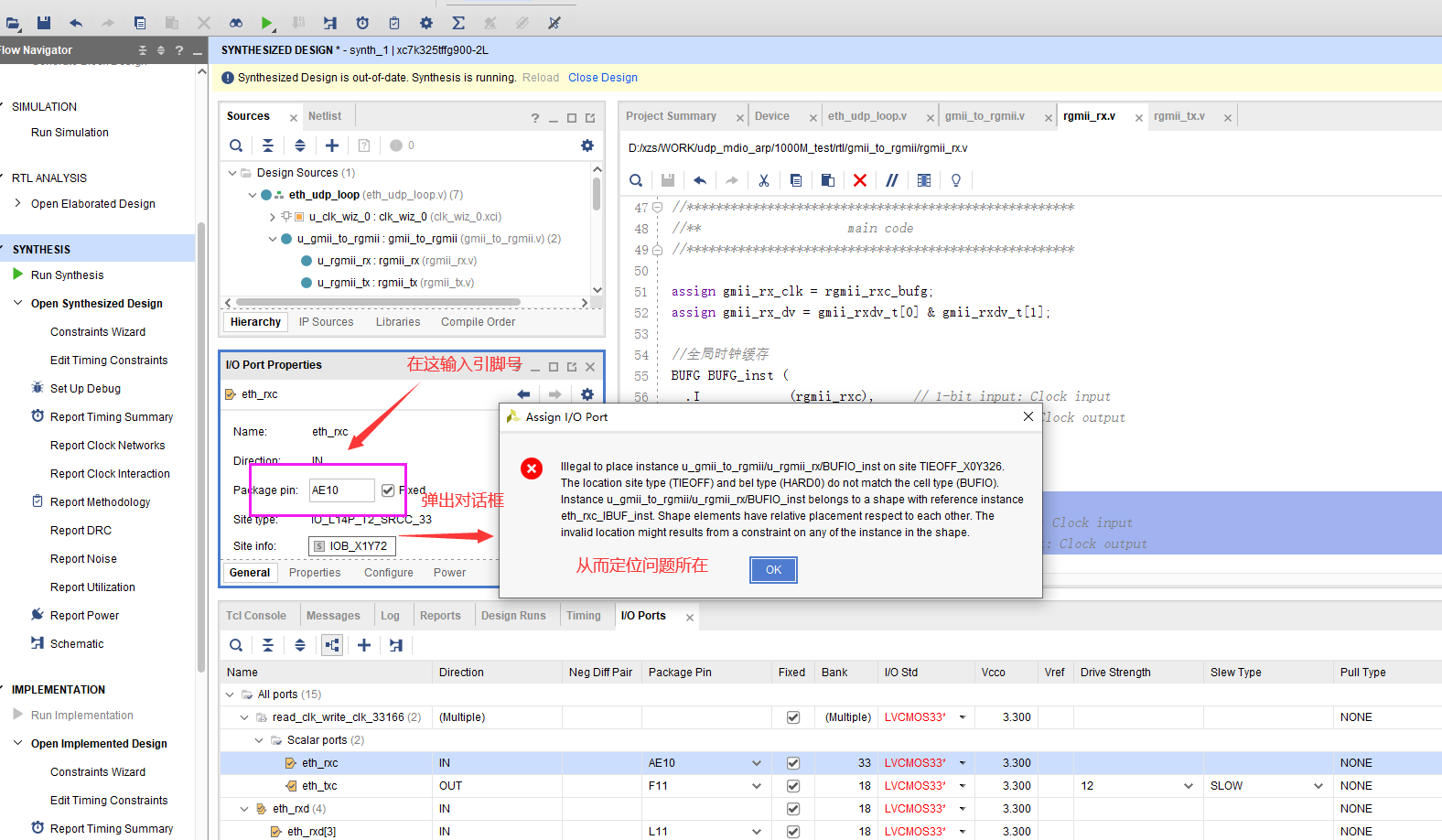

Illegal to place instance u_gmii_to_rgmii/u_rgmii_rx/BUFIO_inst on site TIEOFF_X0Y326. The location site type (TIEOFF) and bel type (HARD0) do not match the cell type (BUFIO). Instance u_gmii_to_rgmii/u_rgmii_rx/BUFIO_inst belongs to a shape with reference instance eth_rxc_IBUF_inst. Shape elements have relative placement respect to each other. The invalid location might results from a constraint on any of the instance in the shape.

中文翻译:

将实例u_gmii_to_rgmii/u_rgmii_rx/BUFIO_inst放置在站点TIEOFF_X0Y326上是非法的。位置站点类型(TIEOFF)和标签类型(HARD0)与单元格类型(BUFIO)不匹配。实例u_gmii_to_rgmi/u_rgmi_rx/BUFIO_inst属于具有引用实例eth_rxc_IBUF_inst的形状。形状元素具有相对于彼此的相对放置。无效位置可能是由于形状中任何实例上的约束造成的。

大概的意思就是端口的类型不匹配

定位到了u_gmii_to_rgmii模块,这个模块是gmii转rgmii接口的,根据提示出现的提示是BUFIO_inst端口类型不匹配。在u_gmii_to_rgmii模块中,用到了原语:BUFG和BUFIO;

//全局时钟缓存

BUFG BUFG_inst (

.I (rgmii_rxc), // 1-bit input: Clock input

.O (rgmii_rxc_bufg) // 1-bit output: Clock output

);

//全局时钟IO缓存

BUFIO BUFIO_inst (

.I (rgmii_rxc), // 1-bit input: Clock input

.O (rgmii_rxc_bufio) // 1-bit output: Clock output

);

查询了一下原语的作用:

BUFG是FPGA中的时钟缓冲器,用于将输入的时钟信号缓存并放大,以提供更稳定和可靠的时钟信号。BUFG通常用于将外部时钟信号引入FPGA芯片内部,或将FPGA内部的时钟信号传递到其他模块中。

BUFIO是FPGA中的输入时钟缓冲器,用于将外部时钟信号缓存并放大,以提供更稳定和可靠的时钟信号。BUFIO通常用于将外部时钟信号引入FPGA芯片内部,并将其用作FPGA内部逻辑的时钟信号。

BUFR是FPGA中的延迟线缓冲器,用于延迟时钟信号。BUFR通常用于在FPGA内部的时序逻辑中,以提供时序控制和延迟。时钟信号在FPGA中非常重要,因为它们控制着FPGA内部逻辑的操作。时钟信号的稳定性和可靠性对于FPGA的性能和正确性至关重要。因此,FPGA设计中需要特别注意时钟信号的布线和缓存。

解决方法:

加上错误中仅仅提示了BUFIO_inst的错误,没有提示BUFG_inst的错误,原语BUFG和BUFIO的功能是一样的,为何不能让代码中的rgmii_rxc_bufio=rgmii_rxc_bufg呢,按照这个思路,将BUFIO_inst模块注释掉,assign rgmii_rxc_bufio=rgmii_rxc_bufg。

通过上面的操作,就可以顺利绑定F13引脚了。

修改后的代码:

//全局时钟缓存

BUFG BUFG_inst (

.I (rgmii_rxc), // 1-bit input: Clock input

.O (rgmii_rxc_bufg) // 1-bit output: Clock output

);

assign rgmii_rxc_bufio=rgmii_rxc_bufg;

--晓凡 2023年10月2日于武汉书