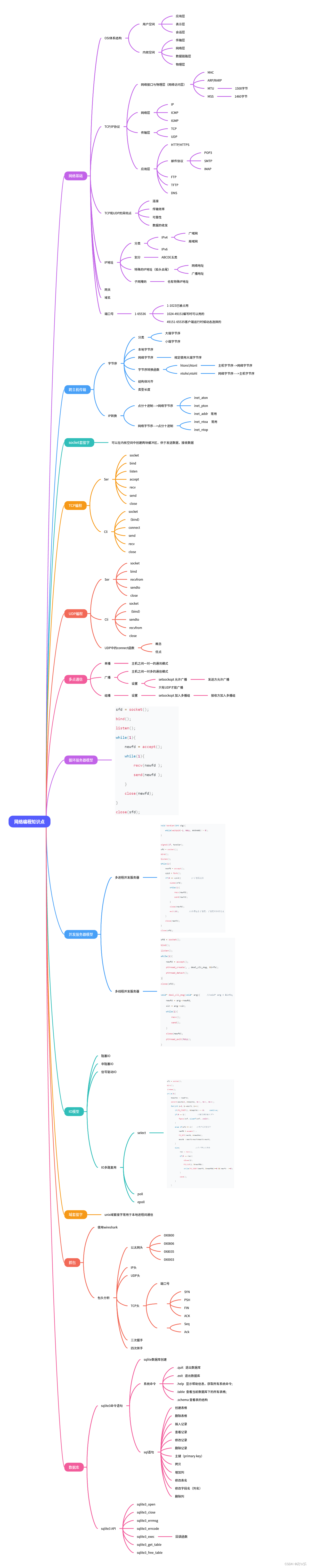

Xilinx AXI DataMover使用说明与测试

- 1 架构说明

- 2 IP设置说明

- 2.1 接口说明

- 2.2 设置说明

- 3 测试说明

- 3.1 S2MM测试

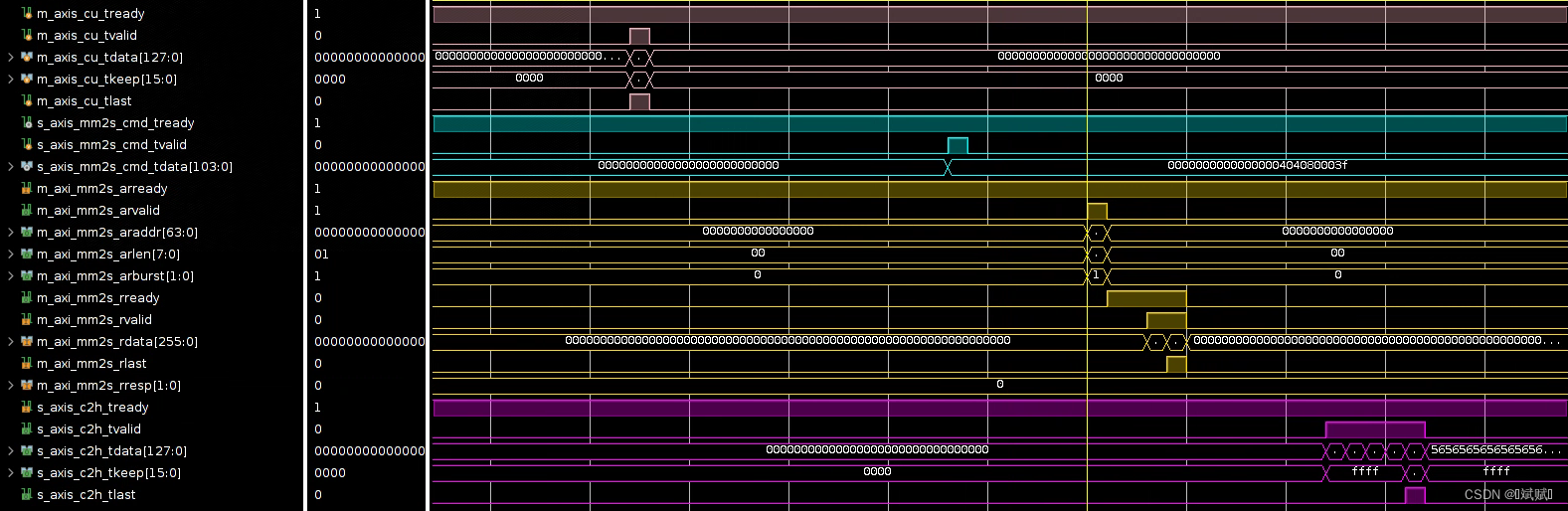

- 3.2 MM2S测试

本文主要介绍Xilinx AXI DataMover的使用和测试方法。

1 架构说明

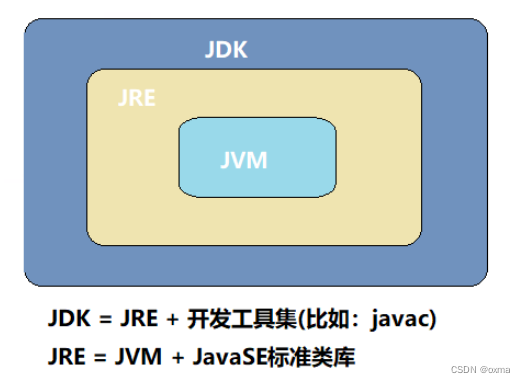

在Xilinx的数据传输总线中,AXI Memory Map接口和AXI Stream接口是最常用的两类接口,如何实现这两类总线接口的转换是比较常见的问题,Xilinx AXI DataMover是实现AXI MM接口与ST接口转换的一个常用IP。AXI DataMover有两个子模块,分别是MM2S和S2MM:

- S2MM:该子模块处理从AXI Stream到AXI Memory Map的事务。它具有专用的符合AXI Stream的命令和状态队列、重置块和错误信号。基于输入的命令和来自AXI Stream接口的输入数据,S2MM模块在AXI MM接口上发出写请求。输入流数据可以选择性地存储在S2MM模块中。数据路径接口(AXI4-Read和AXI4-Stream Master)可以选择与命令和状态接口(AXI4-Stream Command和AXI4-Stream Status)异步。

- MM2S:这个模块处理从AXI Memory Map到AXI Stream域的事务。它具有专用的符合AXI Stream的命令和状态队列、重置块和错误信号。根据命令输入,该子模块在AXI MM接口上发出读取请求,并将读取的数据转换为AXI Stream接口的数据从AXI Stream接口输出。可以选择将读取数据存储在MM2S块中。数据路径接口(AXI4-Read和AXI4-Stream Master)可以选择与命令和状态接口(AXI4-Stream Command 和AXI4-Stream Status)异步。

2 IP设置说明

2.1 接口说明

AXI DataMover的接口主要包括时钟复位信号、输入输出的ST接口、输入输出的MM接口、输入的转换指令、输出的转换状态。

| S2MM接口 | 说明 |

|---|---|

| m_axi_s2mm_aclk | S2MM时钟 |

| m_axi_s2mm_aresetn | S2MM复位 |

| m_axis_s2mm_cmdsts_awclk | S2MM CMD和STS时钟 |

| m_axis_s2mm_cmdsts_aresetn | S2MM CMD和STS复位 |

| S_AXIS_S2MM_CMD | S2MM指令 |

| S_AXIS_S2MM | 输入的S接口数据流 |

| M_AXI_S2MM | 输出的MM接口数据流 |

| M_AXIS_S2MM_STS | 输出的S2MM的状态 |

| s2mm_err | S2MM错误标识 |

| MM2S接口 | 说明 |

|---|---|

| m_axi_mm2s_aclk | MM2S时钟 |

| m_axi_mm2s_aresetn | MM2S复位 |

| m_axis_mm2s_cmdsts_awclk | MM2S CMD和STS时钟 |

| m_axis_mm2s_cmdsts_aresetn | MM2S CMD和STS复位 |

| S_AXIS_MM2S_CMD | MM2S指令 |

| M_AXI_MM2S | 输入的MM接口数据流 |

| M_AXIS_MM2S | 输出的S接口数据流 |

| M_AXIS_MM2S_STS | 输出的MM2S的状态 |

| mm2s_err | S2MM错误标识 |

2.2 设置说明

DataMover操作由控制接口输入的控制指令控制,该接口接收来自用户逻辑的传输命令。MM2S和S2MM各有一个专用的命令接口。命令在输入命令接口上加载单个数据节拍。如果是32位的AXI总线,命令字段的宽度通常是72位。如果系统地址空间超过32位,命令字宽度将被扩展(通过参数化)。例如,64位地址系统要求命令字宽度为104位,以容纳更宽的地址范围,该地址宽度由下图中的Address Width参数决定。

整个命令字段如下图所示:

- BTT:传输的数据字节数

- Type:地址转换类型,0-FIXED;1-INCR

- DSA:只有在DRR设置为1时才生效

- EOF:指示是否为最后一帧命令,影响流接口的tlast信号

- DRR:在DRE启用时生效

- SADDR:MM的起始地址,注意地址对齐

- TAG:标签字段,可传递给Status接口

- RSVD:保留

- xUSER:写入m_axis_mm2s_aruser信号

- xCACHE:写入m_axis_s2mm_awcache信号

注:AXI DataMover核心支持可选的数据调整引擎(Data Realignment Engine, DRE)。当DRE启用时,DRE允许在内存映射数据路径上将数据重新对齐到字节(8位)级别。DRE支持提供高达64位tdata宽度的AXI4-Stream接口。

整个状态字段如下图所示

- TAG:CMD传递过来的TAG信号

- INTERR:1-DataMover内部错误;0-无错误

- DECERR:1-地址编码错误;0-无错误

- SLVERR:1-从设备响应错误;0-无错误

- OKAY:1-整个数据转换过程正常;0-数据转换过程出现错误

注:IBTT功能启用时,状态字段如下图所示 - BRCVD:流接口实际接收的字节数

- EOP:流接口接收到tlast信号置一

IP的设置如下图所示

- Channel Type:Full-允许将MM2S通道配置为所有可能的组合和高级功能;Basic-基本模式,限制了一些特性,并限制MM2S仅用于32位或64位宽的数据

- Maximum Burst Size:MM接口最大的突发长度

- Width of BTT field:命令中BTT字段的宽度

- Address Width:命令中SADDR字段的宽度

- Enable Asynchronous Clocks:使能命令状态接口的时钟与数据流的时钟异步

- Allow Unaligned Transfers:使能DRE

- Enable Store and Forward:启用此参数可确保在存储和转发FIFO中存在请求传输所需的所有数据之前,不会将传输发送到AXI4写地址通道。

- Enable Indeterminate BTT Mode:启用IBTT模式。当传输命令发送到DataMover S2MM命令输入时,输入S2MM流通道上接收的字节数未知时需要启用该功能

3 测试说明

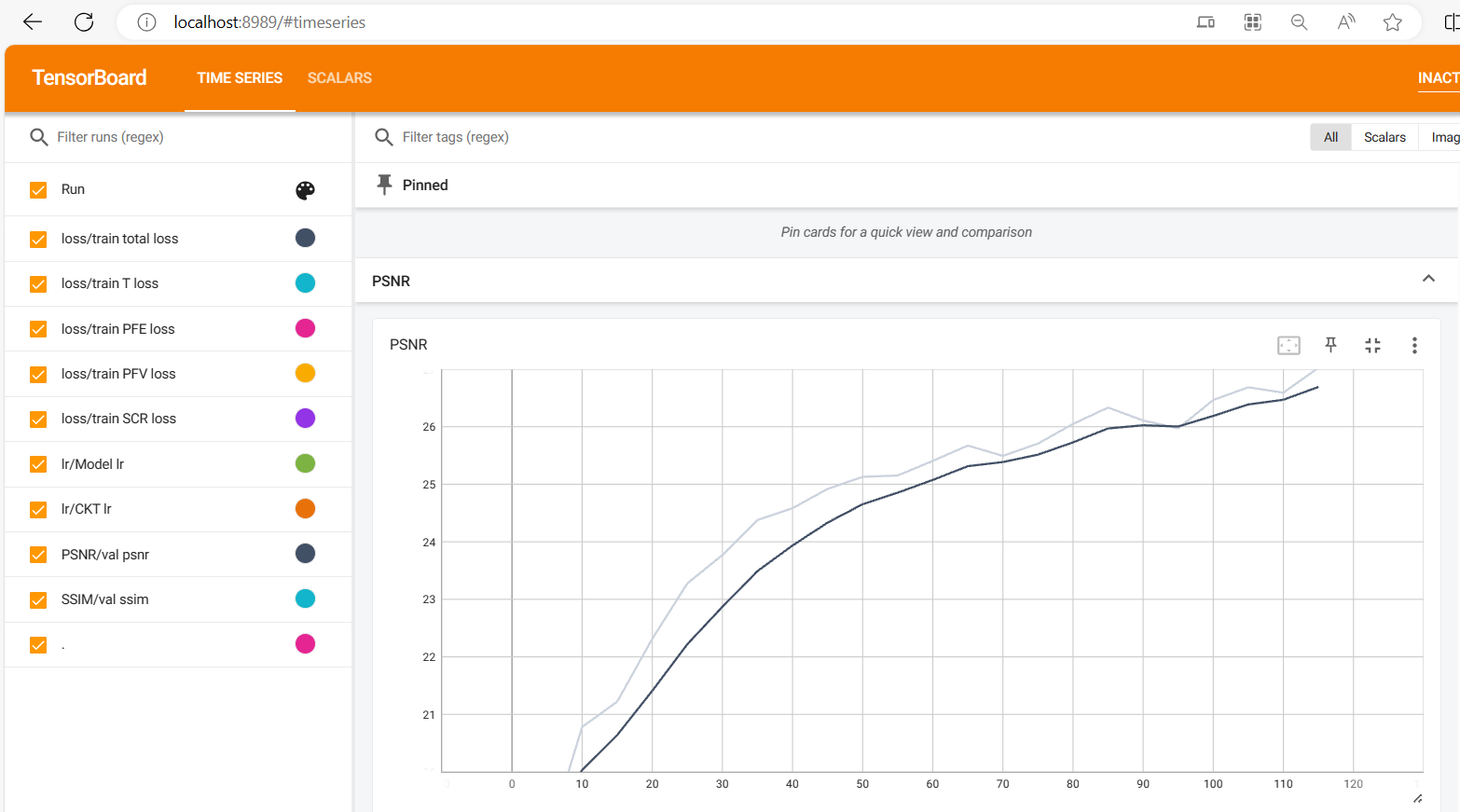

测试工程的架构如下图所示,测试工程可从GitHub下载,主要模块的功能如下所述:

- st1、st2:两个流信号,st1带指令和数据,将数据写入BRAM,st2只有指令,从BRAM读出数据

- axis interconnect:互联总线

- remove_head:拆解帧头和数据

- ctrl_command:生成转换指令

- ST2MM:接口转换模块,即DataMover IP

- add_head:合并数据和帧头

- BRAM:块存储器

3.1 S2MM测试

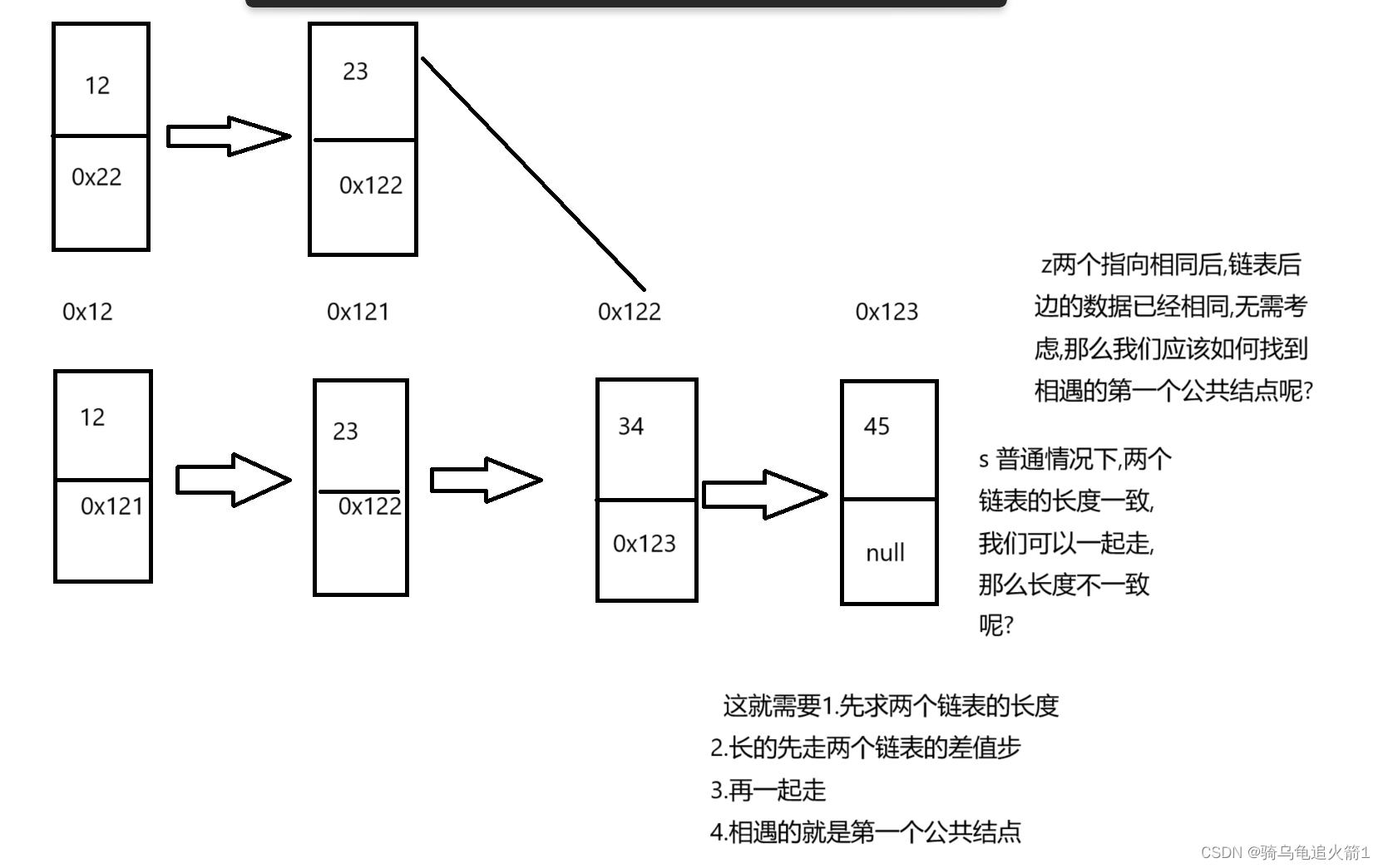

写入数据的流程如下图所示,st1接口输入帧头和数据,经过remove_head模块拆分出帧头和数据,帧头传输给ctrl_command模块生成S2MM的控制命令,数据传输给ST2MM模块,ST2MM模块将数据格式由Stream转换为MM,并将数据写入BRAM。

3.2 MM2S测试

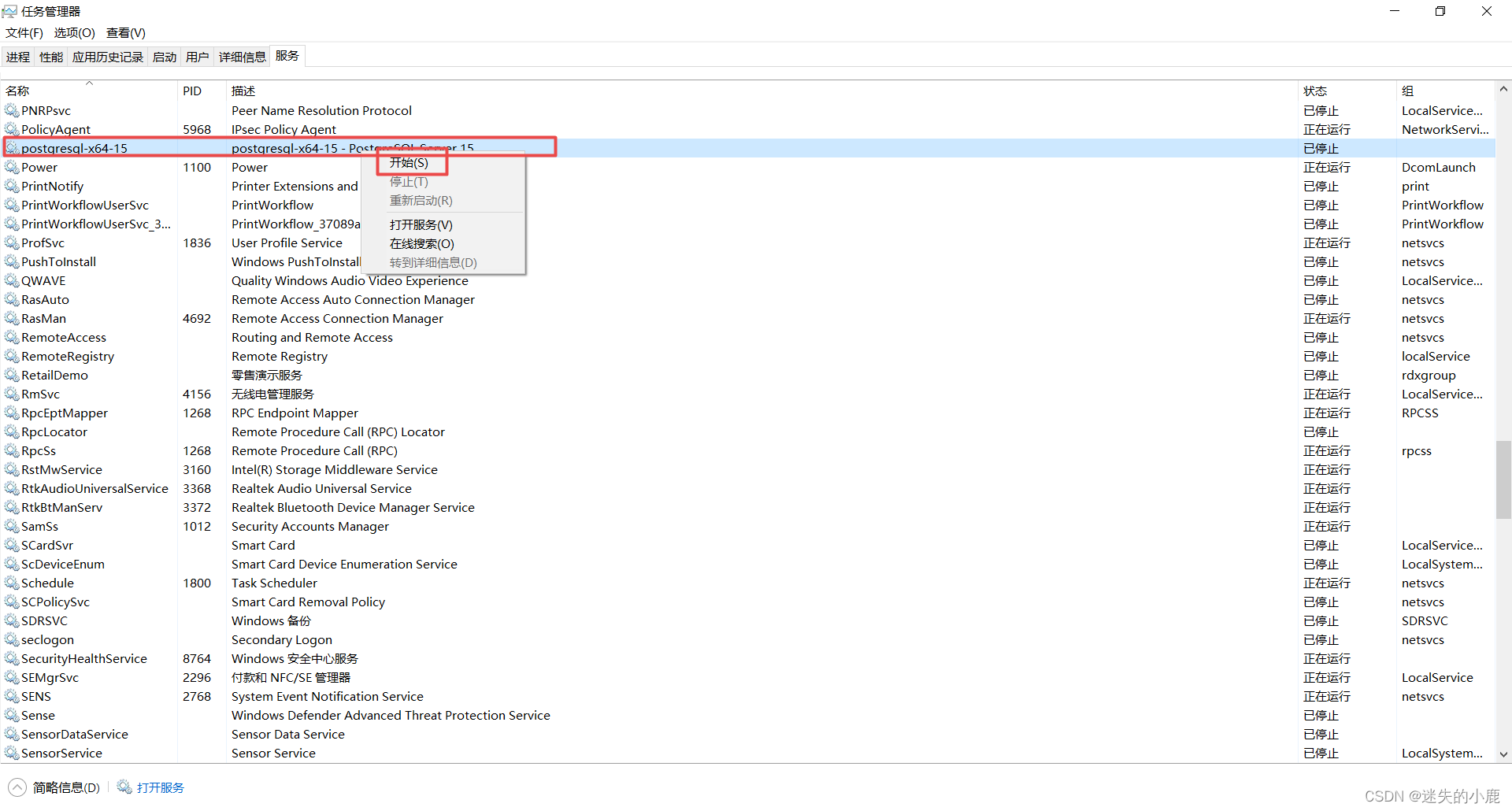

读出数据的流程如下图所示,st2接口输入帧头,remove_head模块拆分出帧头给ctrl_command模块,ctrl_command模块生成MM2S的控制命令和生成新的帧头,并将新的帧头传输给add_head模块。ST2MM从BRAM中取出数据,并转换为Stream接口的数据。add_head模块组合帧头和数据形成新的流信号。