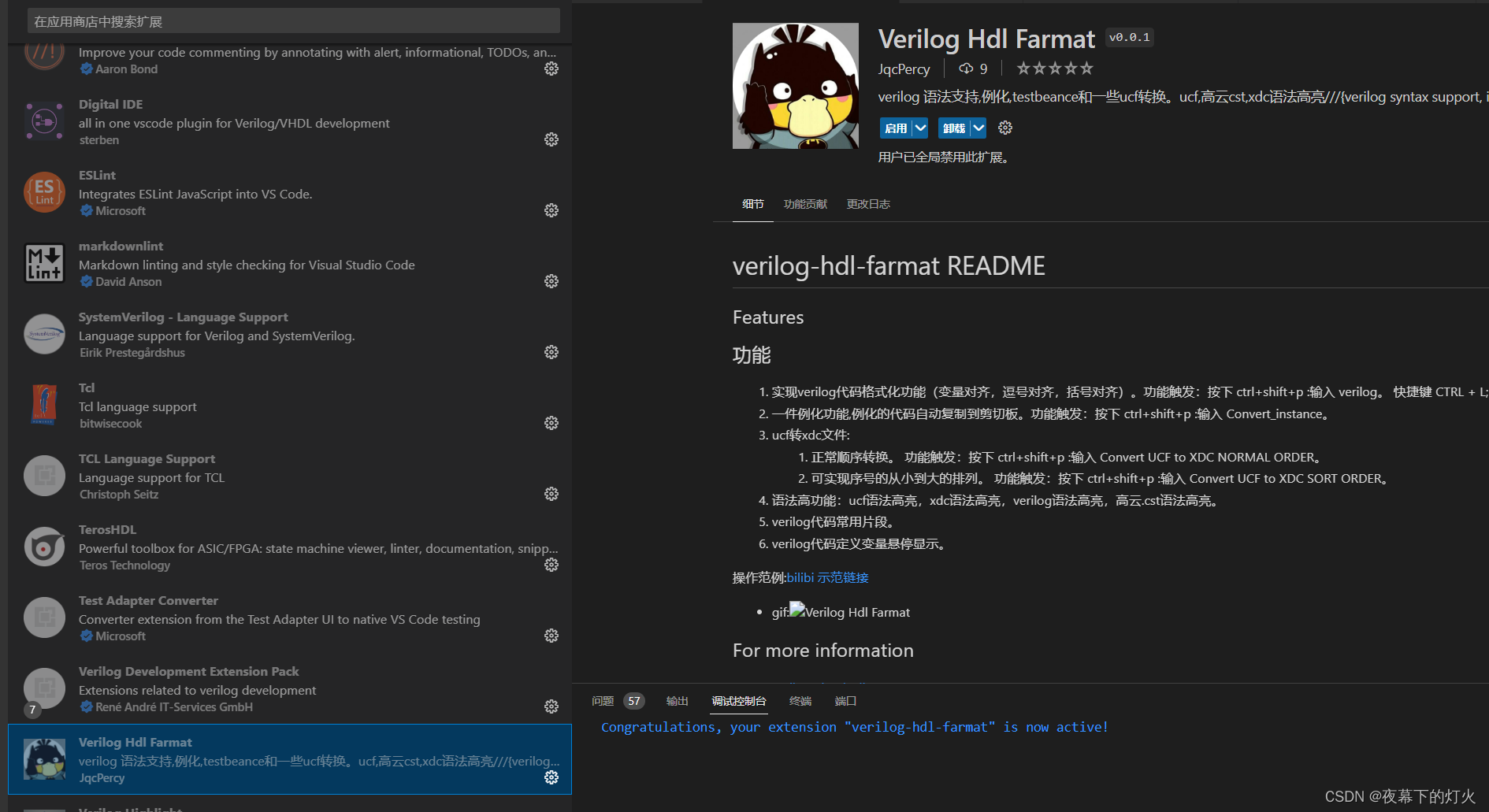

verilog-hdl-farmat README

Features

插件:verilog-hdl-farmat

功能

- 实现verilog代码格式化功能(变量对齐,逗号对齐,括号对齐)。功能触发:按下 ctrl+shift+p :输入 verilog。 快捷键 CTRL + L;

- 一件例化功能,例化的代码自动复制到剪切板。功能触发:按下 ctrl+shift+p :输入 Convert_instance。

- ucf转xdc文件:

- 正常顺序转换。 功能触发:按下 ctrl+shift+p :输入 Convert UCF to XDC NORMAL ORDER。

- 可实现序号的从小到大的排列。 功能触发:按下 ctrl+shift+p :输入 Convert UCF to XDC SORT ORDER。

- 语法高功能:ucf语法高亮,xdc语法高亮,verilog语法高亮,高云.cst语法高亮。

- verilog代码常用片段。

- verilog代码定义变量悬停显示。

- 代码错误检查:加入Verilog-HDL/SystemVerilog/Bluespec SystemVerilog的linter(verilog语法检测)功能

操作范例:bilibi 示范链接

功能介绍

-

verilog代码格式化: 按下 ctrl+shift+p :输入 verilog 或者 快捷键 CTRL + L;

gif:

-

例化功能:

gif:

-

ucf转xdc文件:

-

正常顺序转换 :gif:

-

序号的从小到大的排列转换:gif:gif

-

-

语法高功能:ucf语法高亮,xdc语法高亮,verilog语法高亮,高云.cst语法高亮:

gif:高亮gif -

代码片段:支持输入的代码片段: | module | geli | jishuqi | shangshenyan | tb | zhuangtaiji | always | dapai | assign | alwaysposclk | alwaysnegclk | begin | end | initial | case | reg | regarray | regmemory | wire | wirearray | array | parameter | localparam | integer | signed | include | def | ifdef | ifndef | elsif | endif | undef | ts | default_nettype | ternary | if | ifelse | for | while | forever | function | generate |genvar

其中 比较常用的部分:module/geli/jishuqi/shangshenyan/tb/zhuangtaiji/always/dapai

gif:

-

verilog代码定义变量悬停显示:

gif:

-

代码错误检查:

gif:

Thanks

- verilog-simplealign

- Verilog-HDL/SystemVerilog/Bluespec SystemVerilog

![[网鼎杯 2020 朱雀组]Nmap](https://img-blog.csdnimg.cn/19f78570755348d1b9a8a48e43d0d6dc.png)