目录

1.算法运行效果图预览

2.算法运行软件版本

3.部分核心程序

4.算法理论概述

5.算法完整程序工程

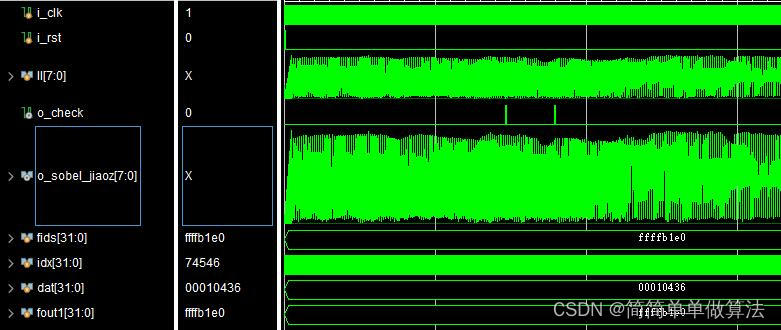

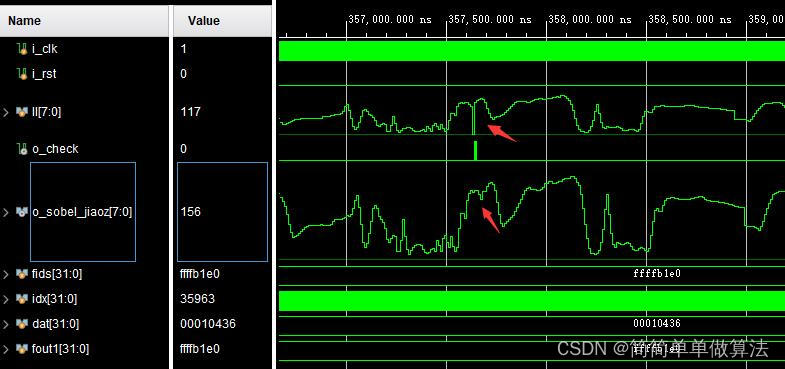

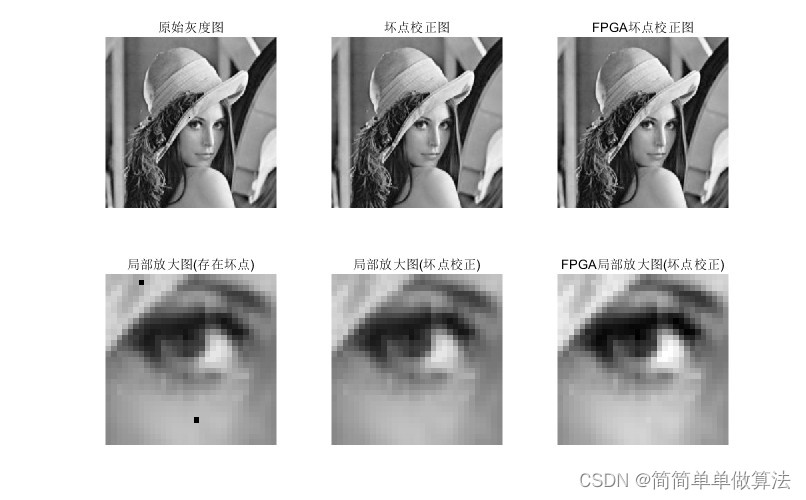

1.算法运行效果图预览

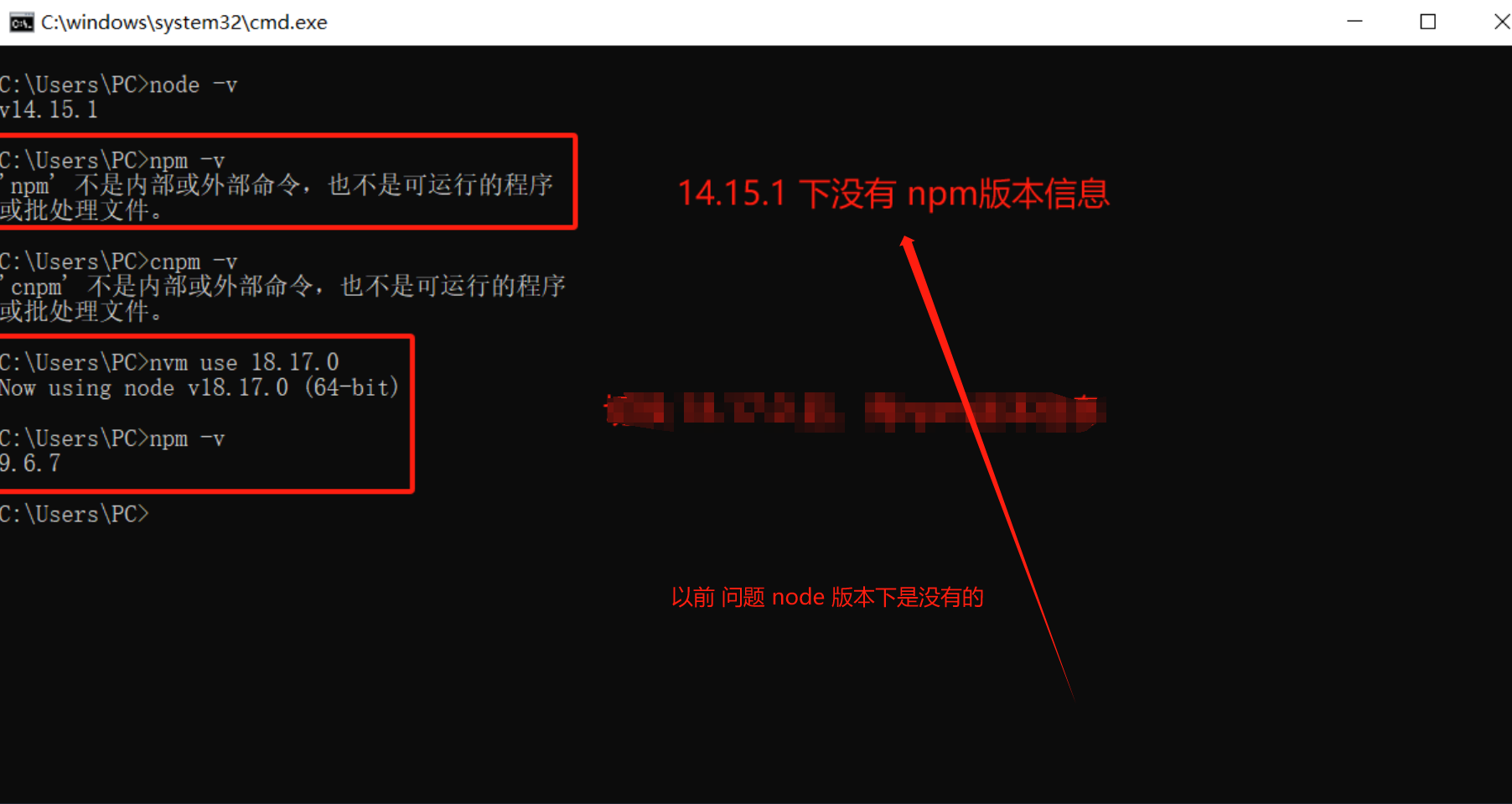

2.算法运行软件版本

vivado2019.2

matlab2022a

3.部分核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/07/31

// Design Name:

// Module Name: sobel

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

module tops(

input i_clk,

input i_rst,

input[7:0]i_I,

output reg check,

output [7:0]o_sobel_jiaoz

);

parameter LEN = 256;

parameter th = 255;

integer i;

reg[7:0]image_buff[LEN+LEN+LEN+LEN+1:1];

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

for(i=1;i<=LEN+LEN+LEN+LEN+1;i=i+1)

image_buff[i]<=8'd0;

end

else begin

image_buff[1]<=i_I;

for(i=2;i<=LEN+LEN+LEN+LEN+1;i=i+1)

image_buff[i]<=image_buff[i-1];

end

end

wire[7:0]tmps1=image_buff[1];

wire[7:0]tmps2=image_buff[1+LEN];

wire[7:0]tmps3=image_buff[1+LEN+LEN];

wire[7:0]tmps4=image_buff[1+LEN+LEN+LEN];

wire[7:0]tmps5=image_buff[1+LEN+LEN+LEN+LEN];

reg[7:0]mat11;

reg[7:0]mat12;

reg[7:0]mat13;

reg[7:0]mat14;

reg[7:0]mat15;

reg[7:0]mat21;

reg[7:0]mat22;

reg[7:0]mat23;

reg[7:0]mat24;

reg[7:0]mat25;

reg[7:0]mat31;

reg[7:0]mat32;

reg[7:0]mat33;

reg[7:0]mat34;

reg[7:0]mat35;

reg[7:0]mat41;

reg[7:0]mat42;

reg[7:0]mat43;

reg[7:0]mat44;

reg[7:0]mat45;

reg[7:0]mat51;

reg[7:0]mat52;

reg[7:0]mat53;

reg[7:0]mat54;

reg[7:0]mat55;

...........................................................

reg [7:0]r1_I;

reg [7:0]r2_I;

reg [7:0]r3_I;

reg [7:0]r4_I;

reg [7:0]r5_I;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

r1_I<=8'd0;

r2_I<=8'd0;

r3_I<=8'd0;

r4_I<=8'd0;

r5_I<=8'd0;

end

else begin

r1_I<=i_I;

r2_I<=r1_I;

r3_I<=r2_I;

r4_I<=r3_I;

r5_I<=r4_I;

end

end

reg[15:0]imagecnt;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

check<=1'd0;

imagecnt<=16'd0;

end

else begin

if(imagecnt===5*LEN)

imagecnt<=5*LEN;

else

imagecnt<=imagecnt+16'd1;

if(i_I==8'd0 & imagecnt>=5*LEN)

check<=1'd1;

else

check<=1'd0;

end

end

........................................................

endmodule

0X_011m4.算法理论概述

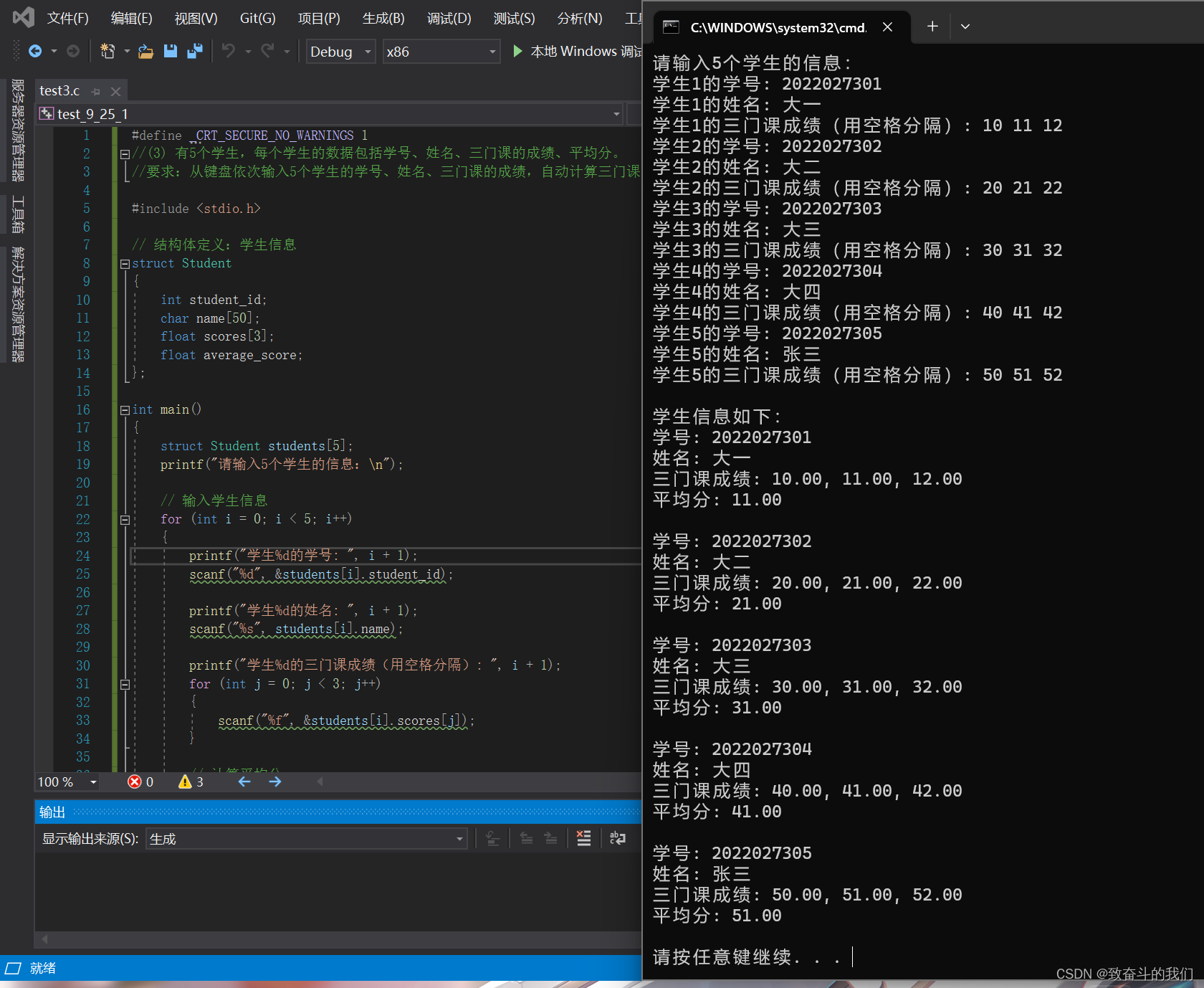

FPGA(Field Programmable Gate Array)是一种可编程逻辑电路,可以用于实现各种数字信号处理算法。在图像处理领域,FPGA也被广泛应用于各种图像修复算法,包括坏点像素修复。

首先,需要了解图像坏点修复的基本原理。图像中的坏点通常是由于摄像机传感器故障或传输错误等原因导致的。这些坏点通常会表现为异常的颜色或亮度值,与周围的像素点明显不同。因此,我们可以利用这个特点,通过比较坏点周围像素点的颜色或亮度值,用一个合适的值来替换坏点像素,以达到修复图像的目的。

具体实现上,可以采用中值滤波或均值滤波的方法。中值滤波是一种非线性滤波方法,它将坏点周围像素点的颜色或亮度值按大小排序,取中间的值作为替换坏点像素的值。这种方法可以有效去除噪声,而且对于线性变换的坏点修复非常有效。而均值滤波是一种线性滤波方法,它将坏点周围像素点的颜色或亮度值求平均,取平均值作为替换坏点像素的值。这种方法操作相对简单,本系统采用均值滤波器实现。

在基于FPGA的实现中,可以建立一个专用的硬件逻辑单元来处理坏点修复算法。首先,将输入图像数据存储在FPGA的寄存器中。然后,通过一个计数器遍历每个像素点,判断其是否为坏点。对于坏点像素,根据设定的窗口大小(如3x3或5x5),用窗口内的非坏点像素的均值或中值来替换该坏点像素的值。最后,将替换后的图像数据输出到外部存储器。

具体实现过程中,可以采用Verilog等硬件描述语言进行编程。例如,对于3x3的窗口,可以建立一个32位的移位寄存器(shift register),将窗口内的像素数据按顺序输入到寄存器中。然后,通过一个计数器控制寄存器的移位操作,将窗口内的像素数据按顺序输出到输出缓冲区(output buffer)。同时,将输出缓冲区中的数据写入到寄存器中,以实现图像数据的存储和传输。

需要注意的是,FPGA的图像处理实现是基于并行处理的,可以同时处理多个像素点。因此,对于大规模的图像数据,可以通过优化算法和调整参数来提高处理速度和精度。此外,由于FPGA具有可编程性,可以根据不同的应用需求来定制硬件逻辑单元,以实现各种复杂的图像处理算法,具有很高的灵活性和可扩展性。

5.算法完整程序工程

OOOOO

OOO

O

![[硬件基础]-快速了解I2C串行通信协议](https://img-blog.csdnimg.cn/49bc629e81da4eb4804ef0e71a55458f.jpeg#pic_center)

![[XR-FRAME] 1.O3 文档导览 || XR-FRAME / 有点寡淡,加上图像](https://img-blog.csdnimg.cn/fe286678c5b547349a68dc46343e1110.png)