前言

出笔试题汇总,是为了总结秋招可能遇到的问题,做题不是目的,在做题的过程中发现自己的漏洞,巩固基础才是目的。

所有题目结果和解释由笔者给出,答案主观性较强,若有错误欢迎评论区指出,资料整理来自于“数字IC打工人”等数字IC相关公众号,牛客网等网站真题、网络笔试真题及面经抄录。

保持更新(2023.9.25)文章内含 单选题270道、多选题106道、填空题16道、判断题17道、简答题72道、逻辑推理题3道、C语言 python 脚本编程题8道。

在本文中笔者提供的所有代码,都写成了API,可直接copy到软件编译、运行、给出结果。

题目较多,即使有前人解析和强大的ChatGPT,也难免出错,若发现错误,欢迎评论区讨论。

另外夹带一点私货~: 这一刻,我感觉一定要给.....

数字IC笔试千题解总字数已到达15w+,网页码字卡顿情况严重,故将其分割成多个部分以方便维护,链接如下:

数字IC笔试千题解--单选题篇(一)

数字IC笔试千题解--单选题篇(二)

数字IC笔试千题解--多选题篇(三)

数字IC笔试千题解--填空题篇(四)

数字IC笔试千题解--判断题篇(五)

数字IC笔试千题解--简答题篇(六)

数字IC笔试千题解--逻辑推理篇(七)

数字IC笔试千题解--编程&&脚本篇(八)

多选题

1. 信号跨时钟域时,会出现亚稳态,其失效性和哪些因素有关__________

A.信号发射端的寄存器输出信号的翻转率

B.信号发射端的寄存器时钟频率

C.信号接收端的寄存器时钟频率

D.同步寄存器的级数

答案:A,B,C,D

翻转率:指在单位时间内,一个逻辑门的输出从低电平变为高电平或从高电平变为低电平的次数。

A. 信号发射端的高存器输出信号的翻转率:亚稳态的出现是由于信号传输过程中的时序关系导致的,翻转率高的信号容易在传输过程中出现时序问题,从而导致亚稳态的产生。

B,C:频率不同的时钟传输数据,有可能会出现亚稳态。

D. 同步寄存器的级数:同步寄存器的级数越多,信号传输的延迟就越大,从而增加了亚稳态产生的风险。

2. 哪些Verilog的写法是不能综合的__________

A.输入为变量的除法

B.循环边界未在编译时指定的for循环

C.含有时序电路的function函数

D.输入为变量的乘法

答案:B,C。A选项除法可以综合,但可能会产生较大的delay和消耗大量的资源,不建议直接写“/”。

3.关于异步fifo说法正确的是____________

A.异步fifo的reset信号,可以经过时钟同步后直接使用

B.读写指针需要通过格雷码做过域处理

C.使用中,读写clock可以是同步的

D.地址格雷码过域时,信号延迟必须小于1个源时钟的周期

答案:B,C。

A选项:异步FIFO的reset信号不应该直接通过时钟同步器使用,因为异步FIFO的复位信号并没有跟读写时钟同步,会存在不同步的情况。使用异步FIFO的reset信号时,通常需要使用专门的同步电路对其进行同步,保证其同步到读写时钟的时序。

D选项,在特殊情况下,可能需要更长时间来完成信号的同步,信号延迟可以大于1个源时钟周期。

4.关于clock以下说法正确的是_____________

A.在clock path上可以使用OAI等组合控制逻辑

B.clock可以被当成data使用

C.在设计中尽可能的使用上升沿触发的逻辑

D.clock jitter越小越好

答案:A,B,C,D。A选项,clock gating就是用OAI(或与非)门控制的。B选项,在加密解密电路中,时钟信号可以用作密钥的一部分,也可以用作算法中的一个参数。C选项,时钟上升沿的稳定性通常比下降沿更好。D选项,Clock jitter是指clock信号的时钟抖动,jitter越小,clock越稳定。

5.Hold violation可以通过__________方式解决

A.降低工作电压

B.升高工作电压

C.在capture clock path上插入clk buffer

D.降低时钟频率

E.提高时钟频率

F.在data path上插入delay cell

答案:A,F。改变时钟频率对hold violation没有影响,因为hold violation的计算公式里没有clock cycle。降低工作电压可以增加ck_to_Q的时间,有利于避免hold violation。C选项,插clock buffer只会改变clock latency,而在hold violation的计算公式中, clock latency会被消掉,因此改变它不会对hold time slack产生影响。

6.以下说法正确的是__________

A.当工作电压从1.0V降低到0.9V,系统功耗会降低20%

B.当工艺从0.18um升级到0.13um,工作电压和频率不变的情况下,芯片面积减小,功耗不变

C.85C的leakage power是25C的10倍

D.降低系统时钟频率一半,延长系统运行时间一倍,会降低系统的power

答案:D。A选项,动态功耗计算公式为:CV^2*f。不考虑静态功耗的情况下,工作电压降低到0.9V,动态功耗降低到原来的81%,和选项描述不符,但在绝对多选的情况下,BC肯定错,可以选AD。B选项,功耗会变小,因为走线电容都变小了。 C选项:按照统计数据,85c的leakage大约是25c的8倍左右,即温度每升高20度,leakage翻一倍。

7. 以下哪些是第三代移动通信标准

A EDGE

B TD-SCDMA

C LTE

D WIFI

答案:B。

第三代移动通信标准通常指的是3G标准,主要包括以下几种:

-

CDMA2000(Code Division Multiple Access 2000):是由3GPP2(3rd Generation Partnership Project 2)制定的一种3G标准,主要应用于北美和亚太地区,提供高速数据传输、语音和多媒体服务。

-

WCDMA(Wideband Code Division Multiple Access):是由3GPP(3rd Generation Partnership Project)制定的一种3G标准,主要应用于欧洲和亚洲地区,支持高速数据传输、语音和多媒体服务。

-

TD-SCDMA(Time Division-Synchronous Code Division Multiple Access):是由中国自主研发的一种3G标准,主要应用于中国境内,支持高速数据传输、语音和多媒体服务。

-

WiMAX(Worldwide Interoperability for Microwave Access):是由IEEE(Institute of Electrical and Electronics Engineers)制定的一种3G标准,采用OFDM技术,主要应用于宽带无线接入领域。

A. EDGE是一种用于GSM网络的高速移动数据传输技术,其速率可达到384kbps,属于2.5G移动通信标准。

B. TD-SCDMA是中国自主研发的3G移动通信标准之一,全称是Time Division-Synchronous Code Division Multiple Access。

C. LTE(Long-Term Evolution)是一种4G移动通信标准,是目前主流的4G技术之一,具有高速数据传输、低时延、高可靠性等特点。

D. WIFI是一种局域网技术,属于无线局域网标准,其速率通常较快,但覆盖范围较小,适用于家庭或办公室等小范围网络。

8.下面哪个选项不可以消除hold time violation()

A 插入buff

B 提高时钟频率

C 降低时钟频率

D 提高电压

答案:B,C,D。A选项,在数据端插入buffer,可以让数据更迟到达后一个寄存器(增加logic delay),进而缓解hold time violation。由STA理论可知,hold time slack计算公式中没有clock cycle,所以改变时钟频率不会改善hold time violation。D选项,提高电压,会让电路中晶体管充放电速度更快,导致数据更早到达,会使得hold time violation更容易发生。

9. 下面那些是基于Systemverilog的验证方法学?()

A VMM

B OVM

C UVM

D AVM

答案:A,B,C,D。

10. 下面哪种方式可以对时序进行检查()

A 即时断言

B 开发断言

C 建立时间约束

D 保护时间约束

答案:C,D。都属于时序分析的部分。

11. 芯方中设计中功耗密度过大,会产生什么不良影响()

A Hot-spot

B电压下降

C不满足时序约束

D封装成本变高

答案:A,C,D。A选项,当芯片中设计的功耗密度过大时,会出现局部的温度升高,即出现“热点”(hot-spot)。B选项,温度升高导致晶体管临界电压下降,这可能会导致电路的电性能发生变化,从而导致电路行为不稳定,不满足时序约束等问题。D选项,温度升高也会对封装造成不良影响,例如,可能会导致封装材料失效,从而增加封装成本。

12. 数字电路的验证维度有哪些()

A完备性

B复用性

C高效性

D满足性能

答案:A,B,C,D。参考博客:芯片验证全视之三: 验证能力的五个维度_OnePlusZero的博客-CSDN博客

13. 在验证中下列关于代码覆盖描述错误的是()

A代码覆盖率包括语句覆盖率

B代码覆盖率包括条件覆盖率

C代码覆盖率包括功能

D代码覆盖率达到100%说明所有Bug已清除

答案:C,D。代码覆盖率不包括功能覆盖,而是只包括代码执行路径的覆盖情况。

14. 关于systemerilog中new操作的下列描述中,错误的是()

A 它可以用来动态创建对象和对象数据

B使用它创建对象时调用构造函数

C new操作被定义成一个需要有返回类型的函数

D使用它创建对象数组时必须指定对象的初始值

答案:C,D 。构造函数不仅分配内存,还初始化变量。在默认情况下,它将变量设置成默认数值(二值变量为0,四值变量为X)等等。可以通过自定义new函数将默认值设成你想要的数值。所以new函数也称为“构造函数”。但是new函数不能有返回值,因为构造函数总是返回一个指向类对象的句柄,其类型就是类本身。

15. 以下同步逻辑电路和异步逻辑描述正确的是()

A同步逻辑电路是时钟之间没有固定的因果关系,异步逻辑电路是各时钟之间有固定的因果关系

B同步逻辑是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有的操作都是在严格的时钟控制下完成的。

C异步逻辑电路不同时钟域之间不需要进行时钟同步

D 异步逻辑可能存在多个时钟信号,或者不存在时钟信号,电路中一个逻辑的变化就会引起整个电路逻辑的变化。

答案:B,D。A选项,说反了。同步逻辑电路是由时钟信号进行驱动的,各个时钟信号之间有固定的相位关系,而异步逻辑电路是没有时钟信号进行驱动,不同部分之间没有固定的相位关系。C选项,跨时钟与需要同步。

16. 超大规模集成电路计中,为了高速设计,采取以下哪些措施()

A 流水线设计

B 并行化设计

C 资源共享

D 串行化设计

答案:A,B。A选项,切流水减小寄存器之间组合逻辑delay,从而可以增加系统最大运行频率,进而实现告诉设计。B选项,并行化设计,以牺牲数倍资源的代价,提升系统数倍性能。C选项, 资源共享有助于降低面积和功耗。D选项, 串行化设计则会导致系统速度降低,因此不是高速设计的措施。

17. 竞争冒险现象可以怎样消除?()

A 加入滤波电容

B引入同步机制

C不加选通信号

D增加冗余逻辑

答案:A,B,D。A选项,加入滤波电容,滤除毛刺,同时可以对窄脉冲起到平波的作用。B选项,加入同步机制,消除因为组合逻辑传输延时不一致引起的信号竞争。D选项,增加冗余逻辑,来改善组合逻辑传输路径延时不一致的问题,进而避免信号竞争。

18. 下列关于Setup/Hold Time说法正确的是?()

A如果DFF的Hold时间不满足,通常可以通过增加数据路径延时来解决

B如果DFF的Setup时间不满足,通常可以通过增加数据路径延时来解决

C如果DFF的Hold时间不满足,通常可以通过增加时钟路径延时来解决

D如果DFF的Setup时间不满足,通常可以通过增加时钟路径延时来解决

答案:A,D。数据路径延时指的是从前一个DFF到后一个DFF数据传输的delay。时钟路径延迟指的是时钟到后一个DFF的delay t2减去时钟到前一个DFF的delay t1。增加时钟路径延迟,可以让后一个寄存器更慢采样,有利于避免setup violation。减少时钟路径延迟,可以让后一个寄存器更快采样,有利于避免hold violation。

DFF的hold时间不满足,代表数据到达后一个DFF的速度太快了,数据还没保持足够长的时间就被更新了,因此可以通过增加数据路径延时来解决或者减短时钟路径延时,让后一个寄存器采样时间更早,选A正确。DFF的setup时间不满足,代表数据到达后一个寄存器的时间太慢了,应该在后一个寄存器DFF的数据采样窗口之前到来,可以通过

19. 下列数据类型中属于四状态类型的有哪些()

A int

B logic

C bit

D time

答案:B,D。

总结一下system verilog变量数据类型:

四值逻辑类型:integer、reg、logic、wire、tri、time。

二值逻辑类型:byte、shortint、int、longint、bit。

有符号类型:byte、shortint、int、longint、integer。

无符号类型:bit、logic、reg、wire、tri、time。

简答题第6题有张绿皮书sv数据类型的截图,可以参考。

20. 低功耗电路实现的方法有()

A 降低工作电压

B增加负载电容

C降低电路面积

D尽可能提高电路性能

答案:A,C。B选项,增加负载电容会导致电路在充电和放电时需要更多的电荷移动,因此需要更多的电流,进而导致功耗增加。D选项,提升电路性能(提高时钟频率)会增加动态功耗。

21. 请找出以下总线中的串行总线()

A AXI

B SDIO

C UART

D IIC

答案:C,D。

-

AXI(Advanced eXtensible Interface)总线:是ARM公司提出的高性能、可扩展的片上总线,支持高带宽和多处理器访问。主要应用在SoC(System on Chip)中。

-

SDIO(Secure Digital Input/Output)总线:是一种专门用于存储设备(如SD卡、MMC卡等)的输入输出接口,可以支持高速数据传输和安全数据存储。

-

UART(Universal Asynchronous Receiver/Transmitter)总线:是一种异步串行通信总线,用于将数据从一台设备传输到另一台设备。常用于计算机和外部设备(如调制解调器、打印机等)之间的数据传输。

-

IIC(Inter-Integrated Circuit)总线:是一种串行双向通信总线,用于连接集成电路芯片和其他外设,主要用于短距离、低速率的通信,例如连接温度传感器、EEPROM等设备。

需要注意的是,UART和IIC虽然都是串行总线,但它们的应用场景和传输方式是不同的。UART是异步传输,即每个数据字节都有起始位和停止位,而IIC是同步传输,不需要起始位和停止位。

22. 下列哪些方式可以减少亚稳态问题的影响()

A 提升系统时钟频率

B 用反应更快的FF

C 架构上增加data toggle rate

D 改善时钟质量

答案:B,D。用反应更快的FF,可以减少T ck_to_Q,有利于避免setup violation。改善时钟质量,有利于减少clock jitter对时序的影响。

23. 正则表达式描述了一种字符串匹配的模式,可以用来检查一个串是否含有某种子串、将匹配的子串替换或者从某个串中取出符合某个条件的子串等,字符集是指在单个位置上能匹配的各种模式字符的集合,部分字符集的简写形式如下表所示。

| 简写 | 匹配 |

| \d | 十进制数字 |

| \D | 非十进制数字 |

| \s | 空白字符 |

| \S | 非空白字符 |

| \w | 单词字符([A-Za-z0-9_]) |

| \W | 非单词字符 |

| \n | 换行符 |

请问:“\W*\s*input\s*wire\s*(\[\d+\:\d+\])*\s*(\w+)\s*”可以匹配到下边哪个或哪些选项?

A. input wire [3:0] num1

B. // input wire num2

C. // input wire [WIDTH-1:0] num3

D. Input wire [10:0] num4

E. input wire [BIT:0] num5

答案:A,B。\W* 匹配尽可能多非单词字符;\s*匹配尽可能多空白字符;input 字符串;\s*匹配尽可能多空白字符;wire 字符串;\s*匹配尽可能多空白字符;圆括号表示分组(\[\d+\:\d+\])*,匹配尽可能多的字符串中形如"[数字:数字]"的字符串;\s*匹配尽可能多空白字符;(\w+)匹配尽可能多单词字符;\s*匹配尽可能多空白字符。这里*表示0-多个;+表示1-多个。

C选项,WIDTH错误;D选项,Input错误;E选项,BIT错误。

24. 下列属于DFT故障模型的是:()

A.stuck-at

B.transition-delay

C.brige

D.IDDQ

答案:A,B,C,D

Stuck-at 故障是最常用的故障模型,某些互连线出现了问题,导致线上的电平永远固定在0或者1。

Bridging Faults 当电路中的两条或更多条互联线意外连接在一起时,就会发生 Bridging Fault。

Transition Delay Faults 跳变故障因逻辑门故障节点延时,导致未能在期望时间内由1翻转为0或由0翻转为1。

IDDQ Faults,芯片在工作状态下的静态电流偏高,导致电压下降,影响芯片正常工作。

参考博客:可测性设计学习笔记_lu-ming.xyz的博客-CSDN博客

25. 下列属于芯片中时钟树综合质量评价指标的有:

A.时钟网络延时

B.时钟信息偏差

C.时钟周期

D.时钟树功耗

答案:A,B,D。

A. 时钟网络延时:时钟信号从源头到达各个时钟触发器的传输延时,影响芯片的时序约束,延时越小越好。

B. 时钟信息偏差:时钟信号在经过长路径后,由于晶体管的温度、电压等因素的影响,可能会出现时钟信息偏差,导致时序违例,因此需要对偏差进行补偿或者增加时钟校准电路。

D. 时钟树功耗:时钟树的功耗应该尽可能小,但是过小会导致时钟树的延时过大,影响芯片的性能。因此,需要在时钟树综合中平衡时钟树的功耗和时钟树延时。

26. 下列属于降低芯片静态压降的方法有:()

A.增大电源网络密度

B.减小封装电感

C.增加芯片内电容

D.降低工作效率

答案:A,B,C,D。

选项A,增大电源网络密度可以提高芯片的电源供应稳定性,减少电源波动对芯片静态压降的影响,降低芯片静态压降。

选项B,减小封装电感可以降低电感值,从而减少电感对芯片静态压降的影响,降低芯片静态压降。

选项C,增加芯片内电容可以提高芯片的电容性质,从而降低芯片的电阻值,减少静态压降。

选项D,降低工作效率可以降低静态压降。

27. 关于异步处理,以下说法正确的是

A.静态配置信号可以不做异步外理

B.异步处理需要考虑发送和接收时钟之间的频率关系

C.异步FIFO采用格雷码的原因是为了提高电路速度

D.单比特信号打两拍后可以避免亚稳态的发生

答案:A,B。

C选项,异步FIFO采用格雷码是为了解决数据转换时出现的不确定状态问题,而不是提高电路速度。

D选项,双比特信号打两拍不能完全避免亚稳态问题的发生,只是减小了亚稳态问题的可能性。

28. 以下哪一种门电路属于通用逻辑门(可以组合搭建出任何逻辑电路)()

A.AND

B.NAND

C.OR

D.NOR

E.XOR

答案:B,D。与非门和或非门。

参考博客:逻辑电路nand_通用逻辑门(NAND,NOR)_cumt30111的博客-CSDN博客

29. 下面哪些是AHB的特性

A.split transaction

B.burst transfer

C.non-tristate implementation

D.out-of-order data transmission

答案: A,B,C。乱序发送是AXI的特性。

AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下一些特性:

单个时钟边沿操作;

非三态的实现方式;

支持突发传输;

支持分段传输;

支持多个主控制器;

可配置32位~128位总线宽度;

支持字节、半字和字的传输。

流水线方式

一个周期内完成总线主设备( master )对总线控制权的交接

30. 请选出以下能实现burst传输的片内总线

A.APB

B.AHB

C.SPI

D.AXI

答案:B,D。APB和SPI不支持burst传输,这个需要自己去学习AMBA总线4.0,以及常用的串行总线运行规则。

31. 以下同步逻辑电路和异步逻辑电路描述正确的是

A 同步逻辑电路是时钟之间没有固定的因果关系,异步逻辑电路是各时钟之间有固定的因果关系

B 同步逻辑是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有

的操作都是在严格的时钟控制下完成的。

C 异步逻辑电路不同时钟域之间不需要进行时钟同步

D 异步逻辑可能存在多个时钟信号,或者不存在时钟信号,电路中一个逻辑的变化就会

引起整个电路逻辑的变化。

答案:B,D。A选项,说反了。C选项,错误,异步逻辑电路中各时钟域之间需要进行时钟同步,否则可能会出现数据错误和稳态震荡等问题。

32. 超大规模集成电路设计中,为了高速设计,采取以下哪些措施

A.流水线设计

B.并行化设计

C.资源共享

D.串行化设计

答案:A,B。流水线和并行化都是面积换速度的案例。

33. Verilog与其他编程语言有哪几种接口机制?

A.PLI

B.DPI

C.NPI

D.VPI

答案:A,B,C,D

PLI(Programming Language Interface)是Verilog的原始扩展接口,它允许用户通过C语言编写的动态链接库将自定义函数嵌入到Verilog模拟器中。这些函数可以被Verilog中的testbench调用,以提供一些额外的仿真控制和数据分析能力。

NPI(Native Programming Interface)是SystemVerilog中的一种扩展接口,它提供了一种新的、更简单的方法来实现Verilog和C/C++的互操作性。与PLI不同,NPI使用C++语言来实现,允许用户以原生C++的方式编写代码,而无需使用C语言和动态链接库。

Verilog可以与EDA工具的接口进行集成,例如与模拟器、综合器、布局布线工具等进行接口通信。这些接口机制通常使用VPI (Verilog Programming Interface)或DPI (Direct Programming Interface)。

34. UPF描述了以下哪些信息( )?

A.power distribution architecture

B.power data

C.power strategy

D.usage of special cell

答案:A,B,C,D。

UPF (Unified Power Format) 是一种格式,用于描述芯片级别的电源管理信息,其中包括用于控制电源管理的设计元素,如电源域、电源模式、电源网、电源对象等。

A选项,描述了电源网络架构;B选项,描述了每个电源域的电源需求、功耗限制等信息。C选项,功耗策略。D选项,使用特殊单元(special cell)进行电源管理是一种在UPF描述中经常用到的技术。特殊单元是具有特殊电源控制功能的电路单元,可被用来提供更精细的电源管理能力。

35. 芯片设计关注的PPA具体指哪几个方面?

A.Performance

B.POWER

C.Architecture

D.Area

答案:A,B,D。PPA,power、performance、area。

36. 代码覆盖率主要包含

A.行覆盖率

B.条件覆盖率

C.toggle覆盖率

D.功能覆盖率

答案:A,B,C。

代码覆盖率主要包含:

-

行覆盖率(Line Coverage):指被执行到的代码行占总代码行数的比例。

-

分支覆盖率(Branch Coverage):指对于if语句、switch语句等分支结构,所有可能的执行路径被覆盖到的比例。

-

条件覆盖率(Condition Coverage):指所有可能的布尔表达式的取值都被覆盖到的比例。

-

路径覆盖率(Path Coverage):指对于代码中所有可能的路径,是否都被执行到的比例。

-

翻转覆盖率(toogle Coverage):翻转覆盖率衡量的是哪些单比特变量的值为0或1,表明代码中信号的0到1和1到0的翻转情况。

6.有限状态机覆盖率(FSM coverage):有限状态机覆盖率衡量的是状态机中哪些状态和状态转换已经被访问过。表明状态机中各个状态的覆盖情况。

37. 在验证中下列关于代码覆盖率描述错误的是

A.代码覆盖率包括语句覆盖率

B.代码覆盖率包括条件覆盖率

C.代码覆盖率包括功能

D.代码覆盖率达到100%说明所有Bug已消除

答案:A,B。C选项,代码覆盖率不包括功能覆盖率。D选项,代码覆盖率只能表示代码的所有地方都被跑过了一遍,但不代表功能均正确。

38. EDA验证中,下面哪种方式可以对时序进行检查

A.即时断言

B.并发断言

C.建立时间约束

D.保护时间约束

答案:C,D。断言属于功能验证的需求,它并不直接对电路时序进行检查,而是通过对逻辑行为进行验证来检查电路是否符合设计规范。

39. 以下哪些是power special cell ( )?

A.buffer

B.level shifter

C.power switch

D.isolation

答案:B,C,D。

A. buffer:缓冲器,用于在信号路径上提供放大和缓冲功能。

B. level shifter:电平转换器,用于将一个电平转换为另一个电平,通常用于不同电源电压下的电路之间。

C. power switch:功率开关,用于在电路中打开或关闭电源,以控制电路的功耗。

D. isolation:隔离单元,用于在电路中隔离电源或信号,以防止信号冲突或电路损坏。

40. 关于时序逻辑电路Pipeline设计说法正确是( )?

A.Pipeline可以提高吞吐率

B.Pipeline可以降低单个任务的latency

C.Pipeline可以提高时钟频率

D.Pipeline需要对流水线进行切割,设计时要对流水线进行均衡,以保证时序的接近

答案:A,C,D。

pipeline只是提高系统的吞吐量,不能改善单个任务的latency。

41. Which of the following factors are considered to evaluate the quality of a clock tree? ( )

A.Insertion delay

B.Skew

C.Local cell density

D.Dynamic power consumption

答案:A,B,C,D。

时钟树的好坏通常从以下几个方面进行评价:

-

时钟偏移和抖动:时钟树的设计应尽量减少时钟偏移和抖动,以保证时钟信号在整个芯片内的稳定性。

-

时钟功耗:时钟信号是芯片中功耗最大的信号之一,时钟树的设计应尽量降低功耗。

-

时钟频率:时钟树的设计应该使时钟频率稳定,减少时钟周期变化和波动。

-

时钟延迟:时钟树的设计应该减少时钟延迟,保证时钟信号的传输速度,减少时钟树对芯片的性能影响。

-

时钟分布:时钟树的设计应尽可能均匀地分布在芯片上,以避免时钟信号在某些区域过于密集而导致的问题,例如时钟插入、时钟抖动和EMI等问题。

-

时钟树的可测试性:时钟树的设计应考虑可测试性,方便后续测试和故障排除。

-

时钟树的成本:时钟树的设计应考虑成本因素,包括设计时间、布局面积、功耗等方面的成本。

42. We need to define clock specification in SDC file, using commands like below:

create_clock -name GFXCLK -period 600 -waveform {0 300}

what can we know from this command? ()

A.Clock frequency

B.Clock duty cycle

C.Clock source latency

D.Clock name

答案:A,B,D。-name给了名字,-period给了占空比,waveform {0 300} 表示时钟信号的起始时间是 0 纳秒,时钟周期为 300 纳秒。

43. Why should we use double width and double spacing rule for clock net routing? ()

A.Reduce resistance

B.Avoid noise

C.Increase capacitance

D.Take more routing resource

答案:A,B。用更大的线宽可以减小电阻。用更大的线间距,可以减少导线与导线之间的耦合电流,减小噪声,同时减小电容。

44. Developing FPGA or ASIC solution to meet same function requirement. Which description are correct? ( )

A. FPGA is fast time to market

B. FPGA is more flexible to be developed and programmed in keeping changing area

C. ASIC’s per chip cost is cheaper

D. FPGA has better power performance

答案:A,B,C。FPGA确实比ASIC要灵活,但平均成本ASIC会比FPGA低,并且ASIC是专用集成电路,不会像FPGA一样为了编程的灵活性增加很多逻辑,因此ASIC功耗会比FPGA少很多,所以选ABC。

45. Which among the following types are USB Transfer types? ( )

A.Control Transfer

B.Isochronous Transfer

C.Asynchronous Transfer

D.Interrupt Transfer

E.Bulk Transfer

答案:A,B,D,E。

USB(Universal Serial Bus)是一种常用的串行总线标准,用于连接计算机和各种外围设备,以实现数据传输和电源供应等功能。在USB标准中,数据传输可以分为以下几种类型:

-

Control Transfer:用于在USB设备和主机之间进行命令和控制信息的传输,如设置设备地址、读取设备描述符等。Control Transfer是必须被支持的数据传输类型。

-

Bulk Transfer:用于传输大量数据,无需保证实时性和可靠性,适合用于打印机、存储设备等应用。

-

Interrupt Transfer:用于传输实时数据,要求保证低延迟和可靠性,适合用于鼠标、键盘等应用。

-

Isochronous Transfer:用于传输对时间敏感的实时数据,如音频和视频数据等,需要保证数据带宽和传输速率的稳定性和实时性。

46. About MOSFET, which is/are right? ( )

A.gm=Ig/Vgs

B.MOSFET consist of mental, oxide and semiconductor

C.Improving W/L can increase the Ig

D.The channel direction of MOSFET is related to crystal orientation

答案:B,C。选项A,gm=△Ig/△Vgs。选项D,沟道方向和晶向无关,和电压与衬底有关。

47. Which are proper prototype? ( )

A.Int funct(char x, char y);

B.Double funct(char x);

C.Void funct();

D.Char x();

答案:A,B,C。D选项,首先声明数组的时候应该用[],其次声明的数组没有给长度。

48. 下列属于DFT质量的衡量指标有:( )

A、测试覆盖率

B、测试电路面积开销

C、测试时间

D、故障模型

答案:A,B,C。

DFT(Design for Testability,测试性设计)的质量主要考虑以下几个指标:

-

故障覆盖率(Fault Coverage):指测试集合能够检测出的故障占全部可能故障的比例。故障覆盖率越高,说明设计的可测性越好。

-

测试模式数目(Test Pattern Count):指设计所需的测试集合中测试模式的数量。测试模式数目越少,说明设计的可测性越好。

-

测试时间(Test Time):指进行完整的测试所需的时间。测试时间越短,说明测试效率越高,设计的可测性越好。

-

灵活性(Flexibility):指设计的测试方法是否适用于各种不同的测试需求。灵活性越好,说明设计的可测性越高。

-

可靠性(Reliability):指测试结果的准确性和稳定性。可靠性越高,说明设计的可测性越好。

-

设计开销(Design Overhead):指增加可测性所需要的设计开销。设计开销越小,说明设计的可测性越好。

49. 下列关于OCC(on chip clock controller)行为描述正确的是:( )

A、用于控制高频和低频测试时钟的切换

B、用于控制产生指定数目的shift时钟

C、用于控制产生指定数目的capture时钟

D、切换过程可能产生毛刺

答案:A,B,C。选项D,OCC是一个有寄存器构成的电路,不会产生毛刺。

OCC(On-Chip-Clock)含义及功能和结构_cy413026的博客-CSDN博客

50. 下列属于芯片流片前的检查有:( )

A、设计规则检查

B、天线效应检查

C、电路与版图一致性检查

D、形式验证

答案:A,B,C。

芯片流片前的检查主要包括以下几个方面:

1.逻辑电路检查:对设计电路的原理图进行全面的逻辑验证,包括逻辑正确性、时序正确性、时序收敛等方面的验证。

2.物理电路检查:对电路布局进行全面的电气验证,包括布局规则是否符合要求、元件是否正确布置、布局连线是否符合电气规范等方面的验证。

3.DRC/LVS检查:通过设计规则检查(DRC)和电路验证规则检查(LVS)等软件工具对电路进行检查,确保电路设计符合芯片工艺的制造规范和标准,避免因为设计规则违反导致制造失败。

4.电磁兼容性检查:对芯片的电磁兼容性进行检查,包括对芯片的辐射和敏感度等方面的检查,确保芯片符合电磁兼容性标准,避免因为电磁干扰导致芯片运行不正常。

5.热分析检查:对芯片的热分析进行检查,包括对芯片的功耗、散热等方面的检查,确保芯片在正常工作状态下不会过热,避免因为芯片过热导致芯片运行不正常。

6.仿真验证:对芯片进行仿真验证,包括逻辑仿真、时序仿真等方面的验证,确保芯片设计符合预期要求,避免因为设计缺陷导致芯片运行不正常。

51. 下列哪些因素与标准单元动态功耗有关?( )

A、工作频率

B、工作电压

C、亚阈值泄漏电流

D、输出负载

答案:A,B,D

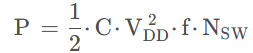

动态功耗公式为:

选项D影响的是公式中的电容C。

52. 关于16点FFT描述正确的是( )

A、共有4级分解;

B、每级有8个蝶形算法;

C、每个蝶形算法需要1次复数乘法;

D、每个蝶形算法需要1次复数加法;

答案:A,B,C。

FFT特点:

1.共有 级运算,16点FFT即4级运算。

级运算,16点FFT即4级运算。

2.每一级有N/2个蝶形运算。

3.每个蝶形需要一次复数乘法和两次复数加法。

53. 以下哪些活动可以通过形式验证保证( )

A、RTL和RTL的一致性

B、RTL的功能完整性

C、RTL和综合网表的一致性

D、两张不同网表的一致性

答案:A,C,D。

形式验证的目标:

1. RTL与RTL:确认新的RTL与原来RTL在功能上是否一致。

2. 门级网表与RTL:确定DC综合的逻辑是正确的。

3. 两个门级网表之间:确认版图输入信息与版图输出信息。

54. 根据约束关系set_clock_groups -async -group{CLK1}{CLK2CLK3},下图中哪些路径会进行时序检查

A、Path1

B、Path2

C、Path3

D、Path4

答案:A,C,D。

set_clock_groups命令禁用所识别的时钟组之间的时序分析,而不禁用同一组内的时钟之间的时序分析。

-asynchronous 表示两个时钟组是异步的,没有固定相位关系。

-group 对时钟编组。

这句约束的意思就是 时钟组{CLK1} 和 时钟组{CLK2 CLK3} 是异步的。

所以跨这两个时钟域的信号不会进行时需检查。

参考博客:FPGA时序约束学习(1)-如何约束时钟_lu-ming.xyz的博客-CSDN博客

55. 随着IC电路设计工艺的进步,漏电功耗占比越来越大,不考虑温漂的影响,以下那些技术能够用于降低漏电功耗?( )

A、clockgating(时钟门控)

B、DVFS(动态电压频率调整)

C、power gating(电源门控)

D、DFS(动态频率调整)

答案:B,C。漏电功耗,主要和电压有关。

56. 在SOC验证应用中,以下哪些选项属于Emulator(仿真加速器)的特点( )

A、比基于FPGA的原型验证平台频率更高

B、加速软件开发,降低验证周期

C、系统级验证,模拟真实场景

D、支持带时序的后仿

答案:A,B,C,D。Emulator是专门用来加速验证的,相对于基于FPGA的原型验证平台,Emulator的仿真速度更快,可以更快地验证设计。Emulator可以支持更大规模的设计,可以加速大规模设计的验证,而基于FPGA的原型验证平台的规模受限于FPGA的大小。支持带有时序的仿真。

57.假设,在某SoC环境中,有一个UART控制器,将其链接至主机并打开串口工具进行连接后,假设已排除所有的硬件电路故障,那么以下说法正确的是:

A、假设终端显示的字符均为乱码,则很有可能是波特率设置不正确

B、假设没有任何显示,则很可能是代码对UART控制器未进行初始化

C、假设该串口输出正常,却无法接收输入的字符,则很可能是UART的中断信号未正确连接

D、假设UART的输出完全正常,但是无法接收输入的字符,则很可能是未设置正确的波特率

答案:A,B,C。选项D,输出完全正常,可以排除波特率的问题。

58. Which are the basic steps about logic synthesis?

A. Translate

B. Mapping

C. Optimization

D. Over Constraint

答案:A,B,C。

Synopsys综合工具DC处理流程 :synthesis=translation+mapping+optimization

translation:把设计的HDL描述转化为GTECH库元件组成的逻辑电路;GTECH库是Synopsys公司提供的通用的、独立于工艺的元件库。

mapping:将GTECH库元件映射到某一特定的半导体工艺库上,此时的电路网表包含了相关的工艺参数。

optimization:根据设计者设定的时延、面积、线负载模型等综合约束条件对电路网表进一步优化的过程。

59. Which of the following methods could reduce power consumption for a chip? ( )

A. Use higher advanced process

B. Shut down some useless logic modules

C. Raise voltage

D. Lower frequency

答案:A,B,D。

A选项,芯片制程越先进,更低的供电电压产生更低的动态功耗。B选项,关停一些逻辑,动态、静态功耗都下降。C选项会增加静态功耗。D选项会降低动态功耗。选择ABD。

60.How to fix hold violation in ECO stage?( )

A. Insert delay cells

B. Sizing up cells

C. Add delay in capture clock tree

D. Add delay in launch clock tree

答案:A,D。

ECO(Engineering Change Order)是芯片设计中的一个阶段,通常在设计流程的后期。这个阶段的目的是通过对设计进行修改,来解决各种问题,如功耗,时序,信号完整性,容量等方面的问题。ECO的过程通常涉及到修改电路的逻辑、物理布局等,以满足设计要求。

A选项,插buffer可以修复hold violation。B选项,Sizing up cells是指修改晶体管尺寸,对修复hold violation起不到什么大作用。C选项,应该在launch端增加delay。

61. ESD (Electrostatic discharge) is the sudden flow of electricity between two electrically charged objects cansed by contact, an electrical short, or dielectric breakdown. What are the ESD cases in daily life?( )

A. The static electricity you can feel after drying clothes in a tumble dryer

B. Rub a carpet and then touch a metal door handle

C. Touch a metal stick with anti-static gloves

D. The shock when touching the banister of an escalator

答案:A,B,D。

生活中静电放电 ESD (Electrostatic discharge) 的例子:

A: 用滚筒烘干机烘干衣服后能感受到的静电

B:摩擦地毯,然后触摸金属门把手

C: 使用防静电手套接触金属棒

D: 触摸扶梯扶手时的点击

62. Dynamic power is proportional to( )

A. Frequency

B. Load Capacitance

C. Work temperature

D. Threshold Voltage

答案:A,B。

63. Which of the following descriptions is correct about inverter?( )

A. CMOS inverter VTH is about 1/2VDD

B. When input is low, the output voltage=VDD

C. Inv is an important device for Memory

D. We want smaller SNM in the circuit

答案:A,B。

Latch和FF对Memory很重要,跟inverter没啥关系。SNM是静态噪声容限,SNM越大代表电路的抗干扰性越好。

64.PN结的特性包括哪些

A. 单向导电性

B. 电容特性

C. 电阻特性

D. 击穿特性

答案:A,B,D。

65. PC协议的层次包括哪些

A. Transaction Layer

B. Data Link Layer

C. Physical Layer

D. Network Layer

答案:A,B,C。

PC(Peripheral Component Interconnect)是一种常用的计算机总线标准,其协议层次包括以下四个部分:

1.物理层(Physical Layer):主要负责传输数据的物理部分,包括总线宽度、时钟频率、传输速率等硬件相关的细节。

2.数据链路层(Data Link Layer):负责数据的传输、流量控制、错误检测和纠正等功能,确保数据的可靠性。

3.传输层(Transaction Layer):负责管理数据的传输、缓存和重传等操作,处理多个数据传输请求和响应之间的关系。

4.应用层(Application Layer):为上层软件提供一系列的访问和控制接口,实现数据的传输、存储和处理等功能。

66.which of following code would print “hello”( )

A.

int main(){

int num= 100;

char*p= NUL;

char str[]="hello";

num= strcpy (p,str);

printf ("%s\n", str);

return 0;

}

B.

int main(){

char*p=NULL;

char str[]="hello";

sprintf (p,str);

printf ("%s\n",p);

return 0;

}

C.int main() {

int num=100;

char*p=(char*)malloc(20);

char str[]="hello";

num=strcmp(p,str);

printf ("%s\n", p);

free(p);

return 0;

}

D.

int main(){

char*p=(char*)malloc(20);

char str[]="hello";

sprintf (p,str);

print("%s\n", p);

free(p);

return 0;

}A. A

B. B

C. C

D. D

答案:A,D。

在C语言中,sprintf()函数用于将格式化的数据写入到一个字符串中,其语法如下

int sprintf(char *str, const char *format, ...)其中,第一个参数是指向目标字符串的指针,第二个参数是格式化字符串,后面的参数是要格式化输出的数据。sprintf()函数返回写入到字符串中的字符数。

例如:

#include <stdio.h>

int main()

{

char str[100];

int num = 123;

float f = 3.14159;

sprintf(str, "The number is %d and the float is %f", num, f);

printf("%s\n", str);

return 0;

}输出结果为:

The number is 123 and the float is 3.141590A:strcpy:char *strcpy(char *dst, const char *src);

这里将str复制给p,不过最终输出str。

B:sprintf: int sprintf( char *buffer, const char *format [, argument,…] );

将字符格式化输出到另一个字符串。

这里指针没有指向已开辟的空间。

C: strcmp() 函数用于对两个字符串进行比较(区分大小写)。

int strcmp(const char* stri1,const char* str2);

67. 以下关于verilog的叙述中,正确的是:( )

A.描述组合逻辑的always块中,可以通过在最开始给变量赋初值的方式避免综合出锁存器(latch)

B. generate语句可以用来多次例化某一模块

C.用于综合的代码里,对同一寄存器的赋值可以出现在两个always块中

D. systemverilog用于验证的语言,因此不能被综合

E.状态机的状态编码等常量一般用parameter定义

答案:ABE。

68.下列可以用于消除电路中竞争冒险的方法是:( )

A.在组合逻辑输出端接入小的滤波电容

B.修改逻辑设计

C.引入选通脉冲

D.在设计中增加冗余项

答案:BCD。A选项不是解决竞争冒险的方法,而是用于平滑掉数字信号中的抖动。

69.以下关于亚稳态的叙述中,正确的是:( )

A.数据的跨时钟域传输,一定会导致亚稳态出现

B.时序电路中建立时间或保持时间违例会导致亚稳态

C.寄存器发生亚稳态时,在最终稳定之前,不能确定其输出端是逻辑高或是逻辑低

D.如果不对亚稳态进行处理,错误数据或亚稳志可能在电路中传播,导敦芯片功能错误

答案:BCD。

70.下列说法错误的是:( )

A.(10101.001)2对应的10进制数为15.125

B.在余三码中,0110与1000的和为1110

C.霍夫曼编码的结果都是等长的码字

D.在BCD码中,5+7的结果是1100

答案:ACD。

A.(10101.001)2对应的10进制数为(1 × 2^4 + 0 × 2^3 + 1 × 2^2 + 0 × 2^1 + 1 × 2^0 + 0 × 2^-1 + 0 × 2^-2 + 1 × 2^-3)10 = 21+ 0.125 = 21.125。因此选项A错误。

B.在余三码中,0110的反码为1001,1000的反码为0111,因此两者之和为1110。因此选项B正确。

C.霍夫曼编码的结果是不等长的码字,常用于数据压缩等领域。因此选项C错误。

D.在BCD码中,5用二进制表示为0101,7用二进制表示为0111,将它们相加得到(0001)BCD,即0001 + 0101 + 0111 = 1101BCD,因此选项D错误。

71.以下关于FIFO的叙述中,正确的是:( )

A.异步FIFO中格雷码到二进制码的转换电路是为了产生访问存储器的地址

B.读写时钟频率相同时,读写地址可以不使用格雷码编码

C.跨时钟域导致的“虚满”喊“虚空”不会引起功能错误

D.对深度为32的异步FIFO,读地址指针需要5bit

E.同步FIFO因为读写时钟相同,不会出现溢出

答案:ACD 。选项B错误,格雷码是为了解决亚稳态问题采用的。选项E错误,读写时钟相同,不代表读写速率相同。

72.下列说法错误的是:( )

A.推挽输出需要设置上拉电阻

B.开漏输出需要设置上拉电阻

C.开漏输出可以用于线与的实现

D.推挽输出不能输出真实的低电平

答案:AD。

参考博客: 推挽输出&&开漏输出_推挽输出和开漏输出_翔在天上飞的博客-CSDN博客

73.一个设计好的CMOS逻辑电路标准单元的延时主要取决于下面哪些因素?( )

A、Input transition

B、Output transition

C、Input load

D、Output load

答案:ACD。

选项A,Input transition,即输入信号的上升时间和下降时间,输入信号的变化越快,延时通常越大。

选项C,Input load,即输入负载,也就是连接到输入端口的电容负载,负载越大,延时通常越大。

选项D,Output load,即输出负载,也就是连接到输出端口的电容负载,负载越大,延时通常越大。

74.如果到达某个寄存器的timing path存在hold违例,下面哪些方法可以修复违例?( )

A、在该寄存器的数据端增加buffer以增大数据延迟

B、在该寄存器的时钟端增加buffer以增大时钟延迟

C、在前一级寄存器的时钟端增加buffer以增加前一级寄存器时钟的延迟

D、在该寄存器与前一级寄存器之间增加latch

答案:AC。让该寄存器数据慢点到来,让前一寄存器时钟慢点到来。

75.以下C语言声明语句,其中阐述正确的是( )

extern int *x;

extern int y[];

A、第一条语句声明x是个int类型的指针

B、第一条语句声明x是个int类型的数据

C、第二条语句声明y是个int类型数组,长度未确定

D、第二条语句声明y是个int类型数组,长度确定

答案:AC。

76.UVM中virtual sequencer有哪些特点( )

A、virtual sequencer控制其它的sequencer

B、virtual sequencer并不和任何的driver相连

C、virtual sequencer并不处理item

D、virtual sequencer主要协调不同的sequencer的执行

答案:ABCD。

参考博客:UVM基础-Sequence、Sequencer(二)_uvm sequencer_不吃葱的酸菜鱼的博客-CSDN博客

77.以下关于verilog function和task描述正确的是( )

A、Function结构中可以加入延时控制

B、Task结构中可以加入延时控制

C、Function中可以调用task

D、Task结构中可以调用function

答案:BD。function和task的区别

task:

任务能调用另一个任务,也能调用另一个函数;

任务可以在非0仿真时刻执行;

任务可以包含延迟、时间或者时序控制声明语句;

任务可以没有或者有多个输入(input)、输出(output)和双向(inout)变量;

任务不返回任何值,任务可以通过输出(output)或者双向(inout)变量传递多个值;

任务的调用是通过一条单独的任务调用语句实现;

任务调用只能出现在过程块中;

任务的执行可以由disable语句进行中断。

function:

函数能调用另一个函数,但不能调用另一个任务;

函数总是在仿真时刻0就开始执行;

函数一定不能包含任何延迟、事件或者时序控制声明语句;

函数至少有一个输出变量,可以有多个输入变量;

函数只能返回一个值,函数不能有输出(output)、或者双向(inout)变量;

函数不能单独作为一条一句出现,它只能以语句的一部分的形式出现;

函数调用可以出现在过程块或者连续赋值语句中;

函数的执行不允许由disable语句进行中断。

78.关于跨时钟处理以下描述正确的是( )

A、单bit信号跨时钟同步时可直接用目标时钟打2拍

B、多bit信号跨时钟同步时可直接用目标时钟打2拍

C、异步FIFO读写指针同步时需要使用格雷码

D、同步FIFO读写指针相互传递时可以不使用格雷码

答案:ACD。

79.systemverilog中C语言可以通过以下哪些方式访问到DUT中的信号?( )

A、PLI

B、VPI

C、DPI

D、force或deposit

答案:ABC。

选项A,PLI(Programming Language Interface):PLI接口与VPI类似,也可以在C/C++代码中读写SystemVerilog中的变量或调用SystemVerilog中的函数。但是,PLI接口是Verilog语言的一部分,只能在Verilog编译器中使用。PLI接口提供了一系列的回调函数,可以用于访问和操作Verilog中的各种对象。

选项B,VPI(Verilog Programming Interface):VPI接口与DPI类似,可以在C/C++代码中读写SystemVerilog中的变量或调用SystemVerilog中的函数。VPI是一种面向对象的接口,提供了一系列的函数和回调函数,可以用于访问和操作SystemVerilog中的各种对象。

选项C,DPI(Direct Programming Interface):使用DPI可以将SystemVerilog与C/C++代码集成。通过DPI接口,可以在C/C++代码中直接读写SystemVerilog中的变量或调用SystemVerilog中的函数。

80.下列关于同步复位和异步复位的区别,说法正确的是( )

A、同步复位在时钟边沿判断复位条件,完成复位动作

B、异步复位不管时种状态,只要复位条件成立就完成复位动作

C、异步复位信号一般同步释放的

D、同步复位信号不允许出现毛刺

答案:ABCD。同步复位、异步复位都应该同步释放,以免出现亚稳态。

81.CMOS芯片设计中动态功耗和下列哪些因素相关( )

A、电压

B、频率

C、电阻

D、负载电容

E、工艺

F、工作温度

答案:ABD。考虑动态功耗,动态功耗公式1/2V^2Cf,根据公式可以确定ABD。选项E工艺是否选择不确定。

82.与FPGA全局时钟资源相关的有( )

A、BUFG

B、DCM

C、NOT

D、DFF

答案:ABD。BUFG(Buffered Universal Global Buffer)和DCM(Digital Clock Manager)是与FPGA全局时钟资源相关的两个重要组件。BUFG是一种特殊的时钟缓存器,可以将来自FPGA器件边缘的时钟信号传输到FPGA器件内部的任何位置,并确保时钟信号的延迟和抖动保持最小。DCM是一种时钟管理器,可以生成时钟信号,并且可以对时钟信号进行相位偏移、频率调整、时钟倍频和分频等操作。

NOT是逻辑非门,与时钟无关。DFF通过全局时钟控制锁存数据。

83.下面属于双状态数据类型的是( )

A、byte

B、logic

C、bit

D、integer

答案:AC。

84.在静态时序分析中计算时钟延迟需要考虑以下哪些因素( )

A、时钟源的抖动(jitter)

B、寄存器的建立和保持时间

C、时钟树不平衡引入的偏差(skew)

D、工艺特性造成的on-chip variation

答案:ACD。计算时钟的延迟,和寄存器无关,注意审题。

85.以下逻辑(A,B,D)能实现:输入三个1bitA,B,C变量,若其中两个以上变量为1,则输出1:

A、x=(A&B)|(B&C)|(C&A)

B、x=(~A&B|~B&A)^C

C、x=(~A&B|~B&A)?C:A

D、x=(~A&B|~B&A)?C:B

答案:ACD。特殊值法。

86.如下verilog描述中哪个或者哪几个会生成寄存器( )

A、always@(clk)

reg_a<=reg_b;

B、always@(negedge clk)

reg_a<= reg_b;

C、always@(posedge clk)

reg_a<=reg_b;

D、assign reg_a=reg_b;

答案:BC。只有BC是时钟边沿触发。

87.在不增加pipeline的情况下,如何解决一条critical path的setup时序不满足的问题?( )

A、将部分组合逻辑电路搬移到前级path上

B、使用更先进工艺的工艺库

C、降低时钟频率

D、在这条path上插入寄存器

答案:ABC。选项D插入寄存器增加了pipeline。

88.关于重载,下面描述正确的有( )

A、函数、任务可以被重载

B、transaction可以被重载

C、sequence不能被重载

D、UVM factory机制的重载要求重载的类必须派生自被重载的类

答案:ABD。sequence可以被重载。在UVM中,重载是指在同一作用域内定义具有相同名称但参数类型和数量不同的函数、任务、task、方法等。通过重载,可以提高代码的复用性和灵活性,同时使代码更加易读易懂。

89.对改善亚稳态问题有效果的方法是( )

A、引入同步机制,如加两级触发器

B、降低时钟频率

C、改善时钟质量,用边沿变化快速的时钟信号

D、用反应更快速的DFF

答案:ABCD

90.有关virtual sequencer描述正确的是( )

A、virtual sequencer并不和任何driver相连

B、virtual sequencer可以控制其他sequencer

C、sequence并不在virtual sequencer里产生和传递

D、virtual sequencer自身可以传递transaction

答案:ABC。

参考博客:UVM基础-Sequence、Sequencer(二)_uvm sequencer_不吃葱的酸菜鱼的博客-CSDN博客

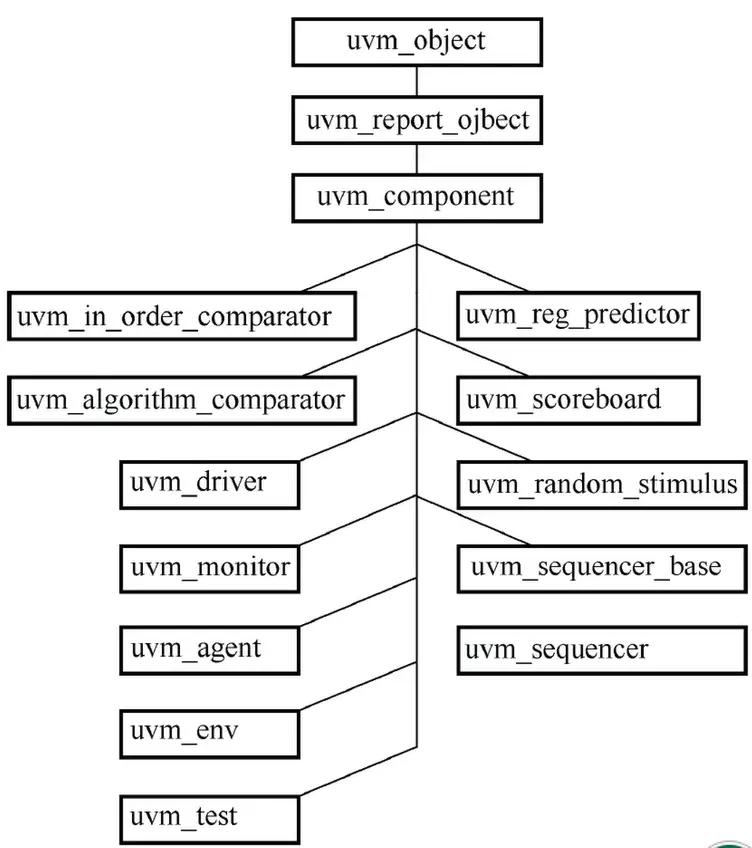

91.下列哪些class派生来自uvm_component( )

A、Sequencer

B、Monitor

C、Transaction

D、Driver

答案:ABD

92.关于线程,以下描述正确的是( )

A、disable语句可以提前结束所有线程

B、fork...join、fork... join_none、fork...join_any语句块都是以并发方式执行

C、fork...join_none内部的任意一个语句块执行完成之后,父线程才能继续执行

D、fork...join_any内部的所有语句块执行完成之后,父线程才能继续执行

答案:AB。

93.给定正则表达式/^[0-5]?[0-9]$/,满足此匹配条件的字符串是()

A.9

B.10

C.00009

D.999

E.99

答案:这个正则的意思是匹配行首[0-5]零次或一次,同时匹配行尾[0-9]一次,满足要求的为AB。选项C错在0重复了不止一次。

94.处理器中哪些相关会引起流水线冲突()

A.数据相关

B.结果相关

C.指令相关

D.资源相关

E.控制相关

答案:ADE

流水线冲突是在CPU流水线中发生的一种现象,通常是由于某些指令在执行过程中依赖于之前的指令或者因为数据相关性引起的。处理器中下面几个相关的情况可能会引起流水线冲突:

-

数据相关:当一条指令需要用到另一条指令的运算结果时,就会产生数据相关性。如果这两条指令之间的间隔时间不足,那么就会导致数据相关的流水线冲突。

-

资源相关:当多条指令需要使用同一部件时,例如ALU、寄存器等,就会产生资源相关性。如果这些指令在同一时钟周期内需要访问这些部件,就会导致资源相关的流水线冲突。

-

控制相关:当一个指令需要改变程序计数器(PC)的值时,就会产生控制相关性。这种情况下,处理器必须等待上一条指令完成才能确定下一条指令的地址,因此也会导致流水线冲突。

处理器中还有一些优化技术,如预测分支、超标量执行等,可以减少流水线冲突的发生。但是,这些技术并不能完全消除流水线冲突,因此在编写程序时,需要尽可能地减少相关性以提高程序的执行效率。

95.下列关于cache写命中时处理错误的是()

A.直接将数据存储至主存中,不再调入Cache中

B.将被访问次数最少的存储行换出,并将行计数器清零

C.不直接修改主存,只改cache,设置脏位,标记数据是否已经被修改

D.把数据同时写入Cache和主存,使用写缓冲

答案:ABD。

选项C正确,不直接修改主存,只改Cache,设置脏位,标记数据是否已经被修改。

在处理器访问Cache时,如果Cache中已经有该数据,即发生了Cache写命中,那么处理器就不需要再次访问主存了,可以直接在Cache中进行数据的读取和修改。但是,为了保证数据的一致性,在Cache中修改数据时,需要设置脏位,表示数据已经被修改过,并且将修改后的数据存储到Cache中,而不是直接修改主存中的数据。

选项A是不正确的,因为直接将数据存储至主存中会导致Cache和主存中的数据不一致。

选项B也是不正确的,因为被访问次数最少的存储行并不一定包含要修改的数据,换出该行对数据一致性没有影响。

选项D也不正确,因为在写缓冲中的数据并没有被写入主存和Cache中,可能会导致数据不一致性。写缓冲主要用于优化写入操作的速度。

96.Which descriptions are correct for System-Verilog language?( )

A. Inheritance

B. Classed based OOP

C. Prototype -based OOP

D. Polymorphism

E. Encapsulation

答案:ABDE。

SystemVerilog与C++类似,是基于类的面向对象。基于原型(prototype-based)典型的是JavaScript。

SystemVerilog面向对象的三个特征:

-

封装 Encapsulation

-

继承 Inheritance

-

多态 Polymorphism

97.Memory BIST can test below elements in the design. ( )

A. Address decoder

B. Memory Array

C. ECC(Error Check & Correct) logic

D. Memory access control logic

答案:。DFT知识,不确定。

98.Select the items which could contribute to functional coverage? ( )

A. SV Cover groups

B. SV Assert Property

C. PSL

D. SV Cover Property

答案:ABD。

选项A. SV覆盖组:覆盖组用于对覆盖项进行分组,并在仿真中跟踪其覆盖率。通过使用覆盖组,您可以为设计指定覆盖目标。

选项B. SV断言属性:断言可用于验证设计是否满足某些功能要求。通过在测试台中添加断言,可以检查设计是否正确运行。

选项C. PSL:PSL(属性规范语言)是用于指定设计必须满足的属性的语言。可以使用PSL检查设计是否满足某些功能要求。

选项D. SV覆盖属性:覆盖属性用于为设计指定覆盖目标。通过使用覆盖属性,您可以跟踪设计中特定信号或事件的覆盖率。

99.Which are the main components of a testbench? ( )

A. Monitor

B. Checker

C. Scoreboard

D. Reference model

E. FIFO

答案:ABCD。

参考博客:从零开始,搭建一个简单的UVM验证平台(一)_不吃葱的酸菜鱼的博客-CSDN博客

100.We need to define clock specifications in SDC file, using commands like below:

Create_clock -name GFXCLK -period 600 -waveform {0 300 }

what can we know from this command? ( )

A. Clock frequency

B. Clock duty cycle

C. Clock source latency

D. Clock name

答案:ABD。

-name:指定一个字符串作为时钟名字。

-period:定义时钟周期。

-waveform:时钟信号的占空比。{上升沿时间, 下降沿时间}

101.Which ways are efficient for cross talk fix?( )

A. Use wide net

B. upsize driving cell

C. add keep out margin

D. downsize driving cell

答案:ACD。

-

使用宽线:减少交叉干扰的一种方法是在受影响的信号之间使用更宽的线。更宽的线会创造更多距离,减少干扰的可能性。

-

添加保留间隙:保留间隙是围绕关键元件或敏感信号周围的空白区域。在敏感信号周围添加保留间隙可以防止其他信号干扰它。

-

减小驱动单元的大小:在某些情况下,驱动单元可能太大,强度过强,从而干扰了信号。在这种情况下,通过减小驱动单元的大小来降低信号强度可以减少交叉干扰。

102.How to fix the EM problem on signal net?

A. set non default rule for violation signal net, increase wire width

B. set non default rule for violation signal net, decrease wire width

C. decrease the signal net fanout

D. increase the signal net output load

答案:ACD

A. 设置违规信号网络的非默认规则:这可能涉及更改信号迹线之间的间距规则,调整过孔的尺寸或位置,或添加地面层或屏蔽。增加导线宽度:这可能有助于降低导线中的电流密度,减少电磁问题。但是,增加导线宽度可能会增加电容和信号延迟,需要平衡权衡。

选项C. 减少信号网络扇出:这可能有助于减少信号网络中流动的电流量,从而减少电磁问题。但是,减少扇出可能也会影响设计的性能和功能。

选项D. 增加信号网络输出负载:这可能有助于减少信号网络中的峰值电流并减轻电磁问题。但是,增加输出负载可能也会影响电路的功耗和信号完整性。

103.Which solutions can be used to reduce parasitic for critical net? ( )

A. Reducing Interconnect Resistance

B. Increasing Wire Spacing

C. Reducing parasitic for Correlated Nets

D. Routing in lower (thinner) metals

答案:ABC。选项D,用更薄的金属会增加互联电阻,增加寄生效应。

-

降低互连电阻:通过使用更宽的金属线或增加金属层的厚度来减少线路的电阻,从而降低寄生效应。

-

增加线间距:通过增加线之间的距离,可以减少线之间的电容,从而降低串扰的影响。

-

使用屏蔽技术:可以在关键网络附近使用屏蔽技术,如金属屏蔽、阻抗匹配等,来降低噪声和干扰的影响。

-

优化布局:合理的布局可以减少信号路径的长度和复杂性,从而减少寄生效应的影响。

104.请判断以下哪些电路是时序逻辑电路()

A.计数器

B.寄存器

C.译码器

D.触发器

答案:ABD。

判断一个器件是否属于时序逻辑电路,可以通过以下几个方面进行考虑:

-

器件的作用:时序逻辑电路通常用于存储、控制、计数等需要考虑时间因素的应用中。如果该器件的作用与这些应用相关,则可能属于时序逻辑电路。

-

器件的输入输出特性:时序逻辑电路的输出结果受到输入信号的时间顺序和状态的影响,因此,器件的输入输出特性也可以是判断其是否属于时序逻辑电路的重要依据。

-

器件的内部结构:时序逻辑电路通常由触发器、计数器、状态机等组成,这些器件内部具有存储器件、时钟信号控制等结构,因此,可以通过分析器件的内部结构,来判断其是否属于时序逻辑电路。

如果一个器件的作用与存储、控制、计数等需要考虑时间因素的应用相关,并且具有时序逻辑电路的特征,例如内部结构具有存储器件、时钟信号控制等结构,则可以判断该器件属于时序逻辑电路。

105.Which of the following descriptions is true of digital signals()

A. It is a discrete signal in time, but it cannot be a discrete signal numerically

B. The signal is discontinuous in time and always occurs in a sequence of discrete moments

C. Numerically quantized, can only be evaluated by a finite number of increments or steps

D. It is a continuous signal in time, and it must be a discrete signal numerically

答案:BC。选项A,数字信号在时间和数值上都是离散信号。选项B,信号在时间上是不连续的,并且总是发生在一系列离散的时刻中(边沿触发,电平触发)。选项C正确,数字信号表示连续变量需要做近似,例如用数字信号表示函数sinx,对离散x取值、计算、存表查询。选项D,信号在时间上连续明显错误。

106.What are commonly used techniques to reduce dynamic power in low power design?

Pick ONE OR MORE options

A. Bus signal encoding, bus decoding (5 points)

B. Clock gating

C. Power gating

D. Dynamic voltage and frequency scaling(DVFS)

E. Body biasing

答案:ABCDE。选项A,总线信号编码,可以降低总线上信号的变化次数,从而降低动态功耗。

选项E,Body biasing是一种在数字电路中用来优化电路性能和功耗的技术。它可以通过改变晶体管的阈值电压来调整其开启和关闭的电压,从而调整电路的速度和功耗。body biasing可以使晶体管在其最优工作点附近工作,从而降低晶体管的开关延迟,并且降低晶体管在切换时的能量消耗,从而降低动态功耗。此外,通过调整晶体管的阈值电压,可以改变晶体管的饱和电流和漏电流,从而降低静态功耗。这也可以通过body biasing来实现。

107.对于设计中所使用的Pipeline,说法中正确的有

A.使用Pipeline会导致数据延时增加,但如果工作频率不变,系统的吞吐量不会改变。

B.使用Pipeline会对时序有好处,STA更容易通过。

C.使用Pipeline一定可以减少面积。

D.使用Pipeline可能会导致面积增大。

答案:ABD。

使用pipeline可能使得面积增大。如果原本组合逻辑深度较深,为了达到目标工作频率,综合会使用大推力的cell,或者使用特殊的电路结构(比如加法器用超前进位加法器),这时候切了pipeline,减少了每级的组合逻辑深度,虽然增多了寄存器,但是组合逻辑可能cell变少;如果组合逻辑深度没有那么极限,切pipeline后增多了寄存器,反而使得面积变大。

108.下列哪些设计可能会对芯片DFT产生不利影响

A.门控时钟设计

B.使用双沿时钟设计

C.内部三态门总线

D.使用内部产生的时钟

答案:ABD。

选项A. 门控时钟的边沿可能会影响测试模式的注入和扫描链的推移。

选项B. 在扫描链中可能会有未知状态或无法控制的状态。

选项C. 内部三态门总线并不一定会对DFT测试产生不利影响,因为它可以实现扫描链和测试模式的注入。

选项D. 使用内部产生的时钟可能无法与测试模式注入的时钟同步,导致测试失败。

109.下列表达式中,哪些可以使用一个或多个二输入与非门器件实现

A.常数1

B. A

C. A+B

D. AB

答案:ABCD。

参考博客:用与非门实现与戓非_计算机系统要素:从零开始构建现代计算机_笑到自然醒的博客-CSDN博客

110.多比特信号A,在时钟域clk_ a存在从8'd100到8'd101到的变化过程中,若在时钟域clk_b直接采用D触发器采样,可能采样到数据是

A.8'h65

B.8'b01100101

C.8'h64

D.8'd100

答案:ABCD。数据线只有一位变化了,其他位不会有亚稳态问题,可能会是8'd101 或者8'd100

111.Formality是由Synopsys公司开发的一种形式验证(Formal Verification)工具,用于两个Design之间的等价性验证。它可以支持如下哪些等价性验证?

A门级网表对门级网表

B. RTL级对RTL级

C. RTL级对门级网表

答案:ABC。

112.

①: always @(posedge clk or negedge rst_n) begin

if(!rst_n)

din_dly <='h0;

else

din_dly <= din;

end

②: always @(posedge clk) begin

din_dly <= din;

end

③: always @(posedge clk) begin

if(!rst_n)

din_dly <= 'h0;

else

din_dly <= din;

end上面三段代码,说法正确的是:

A.②属于无复位寄存器,其PPA更优

B.①属于异步复位逻辑

C.同步复位和异步复位都是在复位时将寄存器状态初始化,所以没有区别

D.③属于同步复位逻辑,rst_n可能通过组合逻辑连接到寄存器D端。

答案:ABD。

113.基于FPGA和ASIC芯片设计的差异需要关注的有

A.时钟复位

B.时钟顿率

C.memory控制

D.上下电流程

答案:ABCD。都要关注

114.报文处理设计规格:

支持的报文长度为36-256字节,其余长度的报文直接丢弃;

接收的报文长度小于64字节时填充PAD (任意数据)使报文长度达到64字节,然后再转发;下面描述错误的是:

A.因为填充PAD是任意数据,因此随便挑一组特殊值,例如全0验证即能够保证功能正确

B.因为大于256B的报文被丢弃了,所以不需要验证该点

C.因为小于36B的报文被丢弃了,所以不需要验证该点

D.该报文处理长度的边界点包含两个值,分别为36和256

答案:ABC。spec上说报文被丢弃了,但你不确定设计是否真的将报文丢弃了,需要验证。

115.下列哪些是必须的,在Post-Layout时序仿真时?

A.Post-Layout网表

B.综合网表

C.标准延时格式文件

D.RTL代码

答案:AC。在进行Post-Layout时序仿真时,必须具备Post-Layout网表以及标准延时格式文件,因为这两个文件包含了物理信息和时序信息,可以提供比综合网表更为精确的仿真结果。

116.当模块的代码覆盖率达到100%时,下列说法错误的是

A.并不能确保验证工作已经完成

B.可确认各类用例的激励构造已经完备

C.可确认各种边界点的测试已经足够充分

D.可确认功能验证充分

答案:BCD。

117.System Verilog中,关于logic类型描述错误的是

A. logic 初始值为'x'

B. logic可以完全替换wire类型

C. logic可以完全替换reg类型

D. logic类型是四值逻辑

答案:BC。logic初始值是x。logic为四值逻辑。