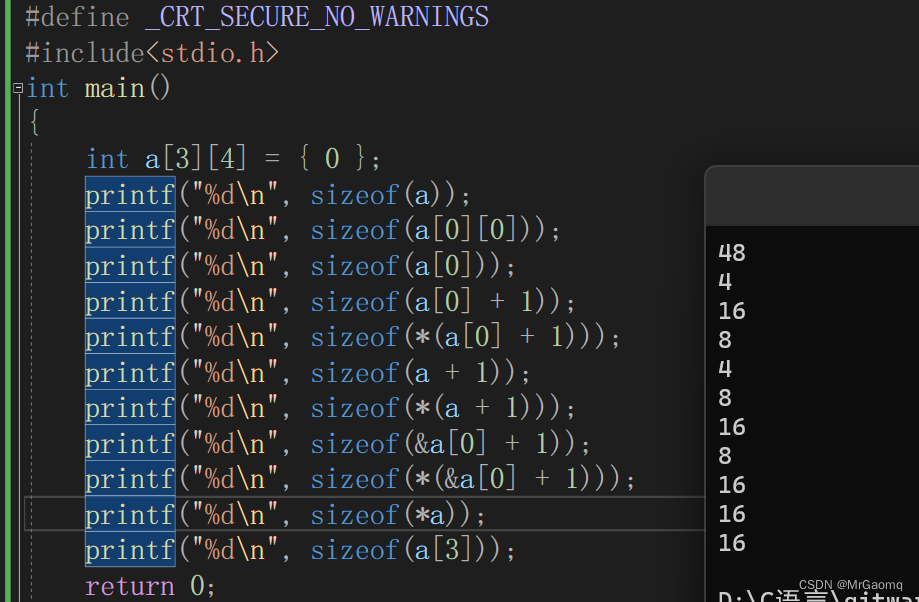

刚开始写的代码如下:

刚开始写的代码如下:

module top_module (

input clk,

input [7:0] in,

output [7:0] pedge

);

reg [7:0] in_pre;

always @(posedge clk)begin

in_pre <= in;

end

assign pedge = in & ~in_pre;

endmodule

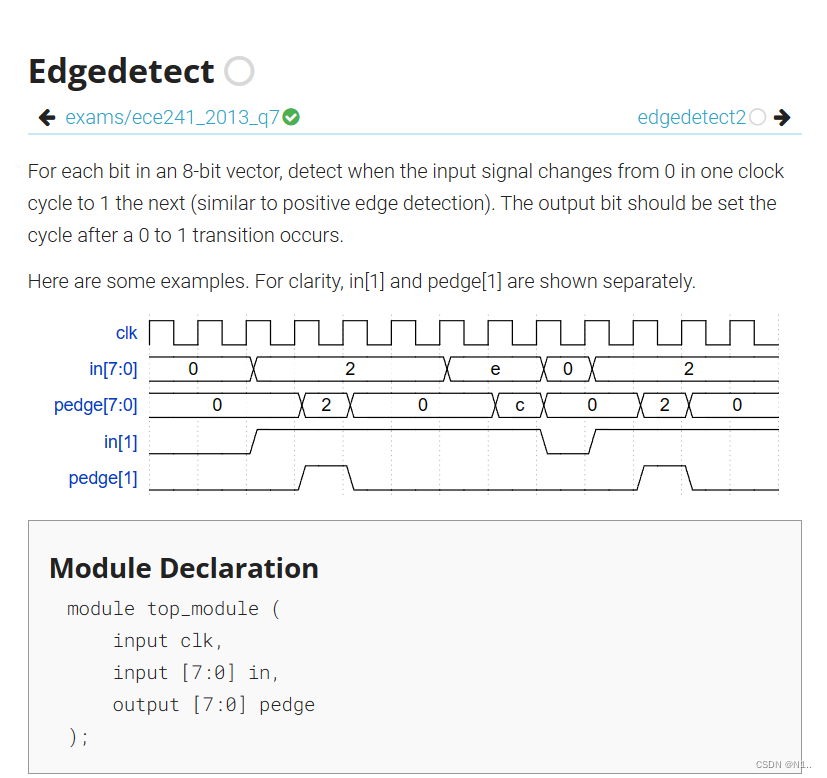

但是提交结果是错误的。猜想原因如下:

assign pedge = in&~in_pre; 表明通过一个门 将in 与 in_pre处理后 输出连接到pedge,那么只要in 或者 in_pre发生变化,那么 pedge结果就会立即发生变化。

但是该题的思路是通过一个寄存器,将输入延迟保存一个周期,通过检测现在的输入和上一周期的输入即可判断是否有上升沿。因此 ,应该将 pedge的赋值语句写在 always @(posedge clk)中,那么,每当一个周期,in_pre发生变化时, 才对pedge进行更改。

以下是正确的代码:

module top_module (

input clk,

input [7:0] in,

output [7:0] pedge

);

reg [7:0] in_pre;

always @(posedge clk)begin

in_pre <= in;

pedge <= in & ~in_pre;

end

endmodule