萌新编写RiscV之经典计算机组成与设计RISCV书记录 总4

其实我一开始不想做这个因为实在是实现的功能复杂 但是都差不多的逻辑

基本目的

实现下列操作

条件分支指令branch if equal (beq)。

算术逻辑指令 add sub and or

条件分支指令branch if equal (beq)。

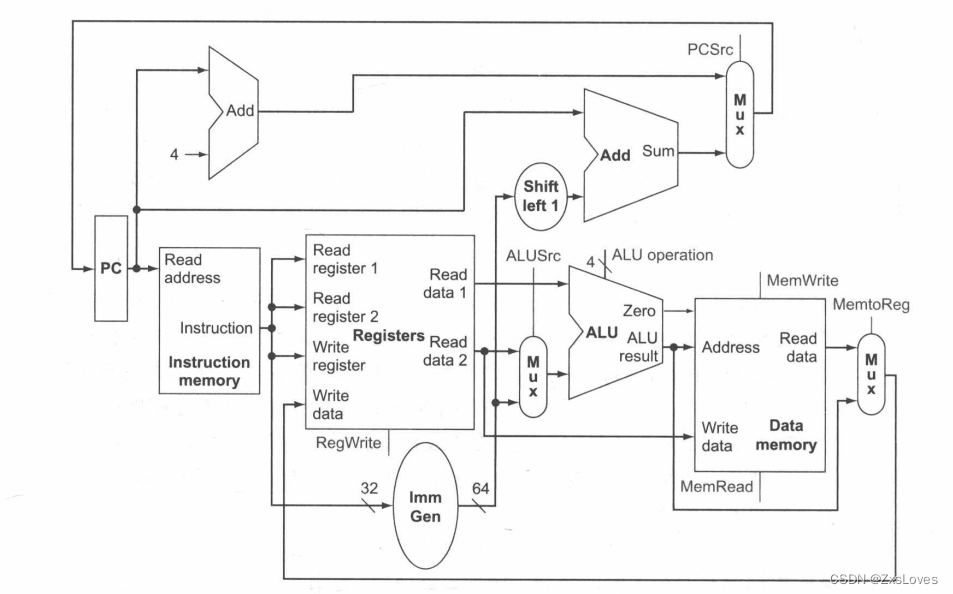

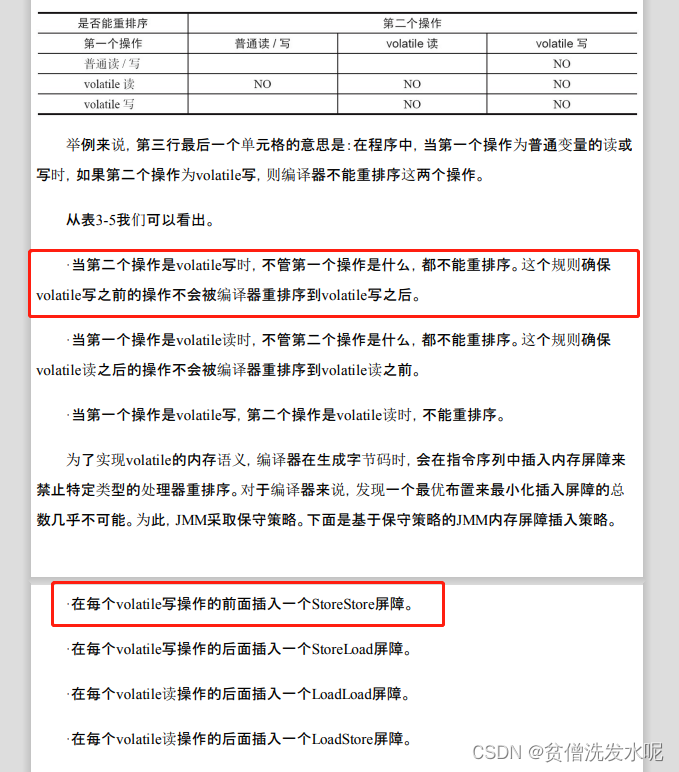

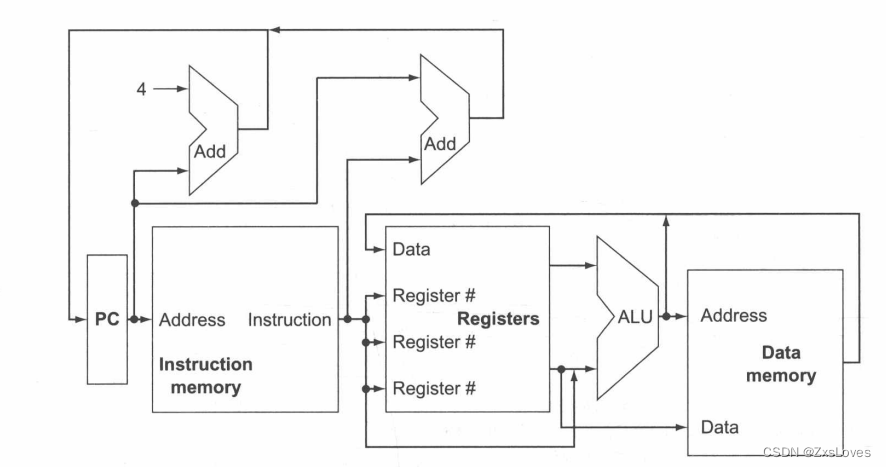

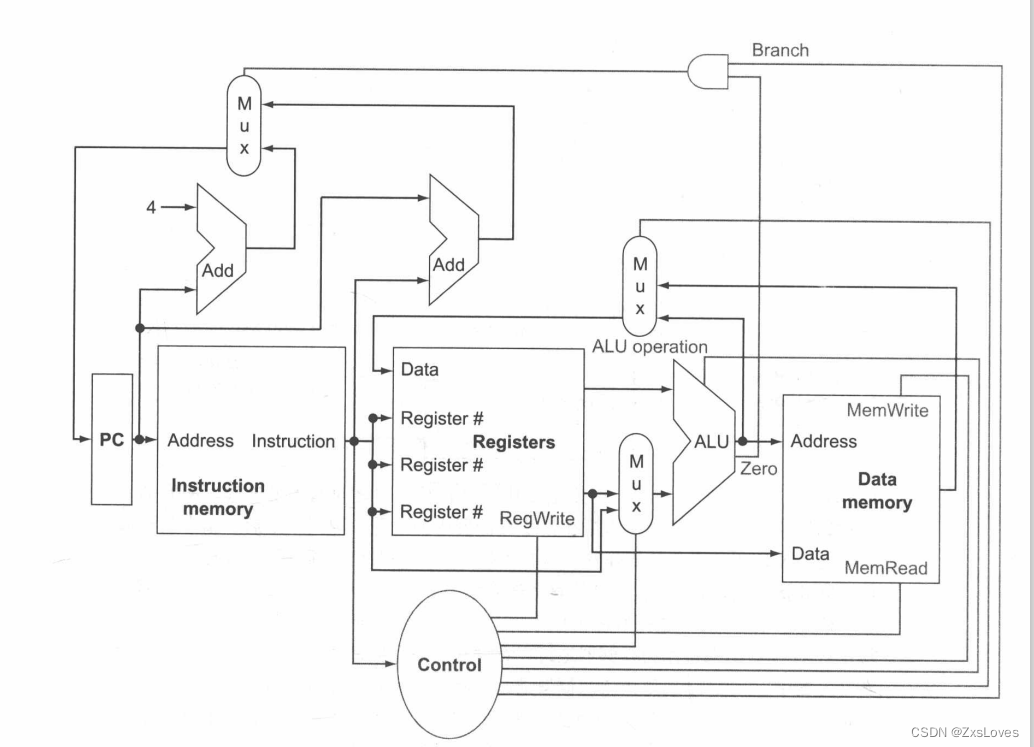

我们确定一下CPU的基本逻辑可以发现对于绝大部分指令来说前几步都是一样的。

1.程序计数器(PC)发送到指令所在的存储单元,并从中取出指令。

2.根据指令的某些字段选择要读取的一个或两个寄存器。对于1 d指令,只需要读取一个寄存器,但大多数其他指令需要读取两个寄存器。

例如,所有类型的指令在读取寄存器后都使用算术逻辑单元(ALU)。存储器访问指令用ALU进行地址计算,算术逻辑指令用ALU来执行运算,而条件分支指令用ALU进行比较。但是经过ALU后,完成各类指令所需的操作就不同了。存储器访问指令需要访问存储器以读取数据或存储数据。算术逻辑指令或载人指令需要将来自ALU或存储器的数据写回寄存器。而条件分支指令需要根据比较结果更改下一条指令的地址;否则,下一条指令的地址会通过PC加4来获得。

1读取指令 2.访问寄存器 3.再通过ALU进行判断 下一步该如何实现

我们现在面对的整个逻辑 实现功能是 先从1.PC程序计数器获得指令在指令存储器中的地址 (PC取到的是指令的地址)

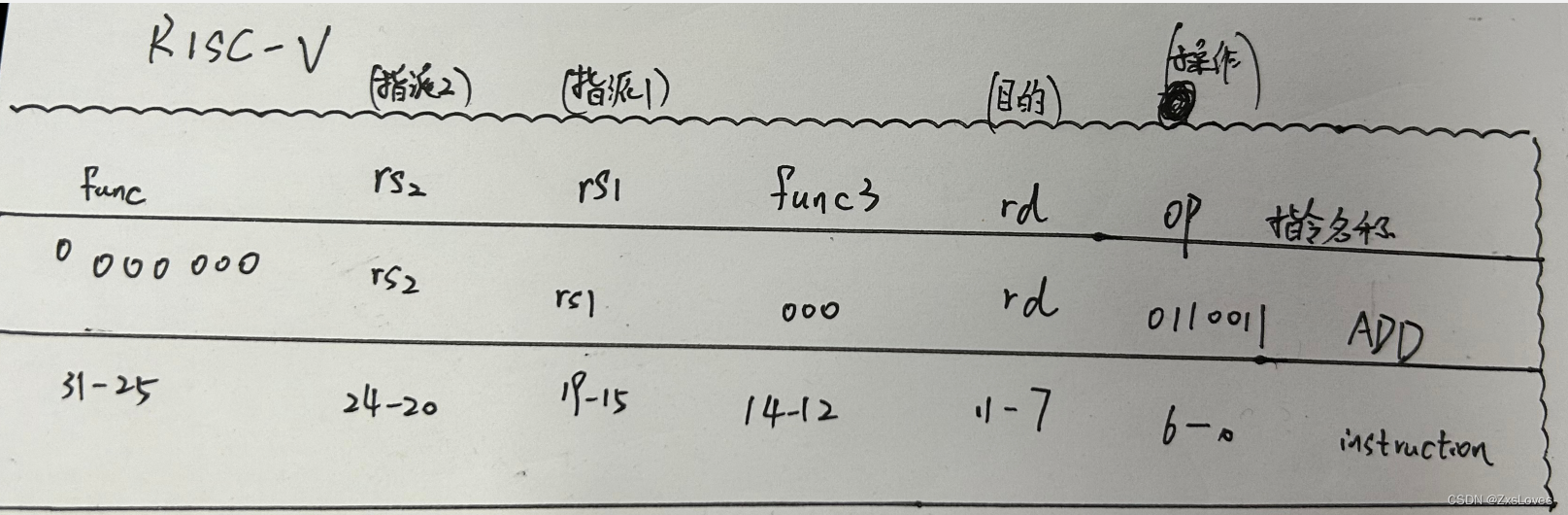

2.我们再通过指令寄存器这一媒介将传入的疑似32位数据 分段成各个我们想要的东西 例如经典的指令ADD

func rs2 rs1 func3 rd op

就像这样 其实我看一些risc 的设计中将读指令和指令分段2个项目结合和分开 其实都可以

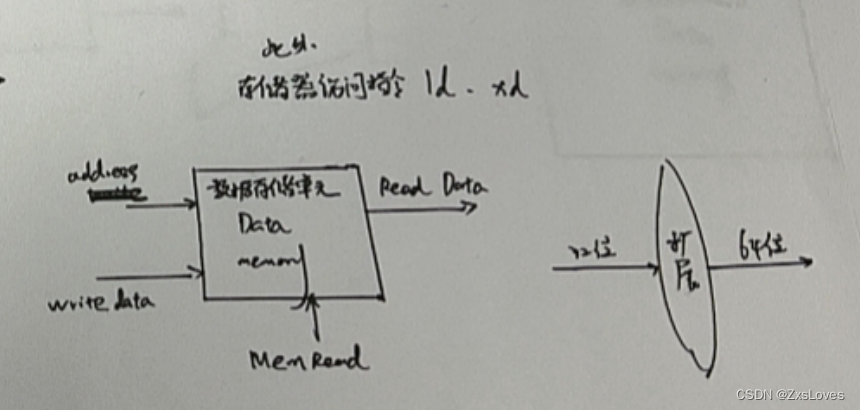

接下来 我们将数据传入ALU 让ALU进行操作 因为是基本的形式 我们ALU只能简单的进行数据的回传 加 利用传过来的数据简单的操作 注意很多时候我们的存取操作需要加入另一个Data memory 来辅助实现

这样形成的CPU功能是孱弱的 我们改进一下加入一个 大的control 控制 来改进问题的实现

我们的目的是实现

我们目前所需要的注意的是 RISC-V

内部的数据通路分为2个单元 一个是处理数据的组合逻辑单元

和存储状态的存储单元

我们会使用D触发器 作为 存储状态的单元 因为 D触发器是最简单的带有2个输入和一个输出 并且由简单的clk时序控制

在本书中会大多数选用 上升沿作为触发的标准

然后我们开始考虑如何建立数据通路的问题

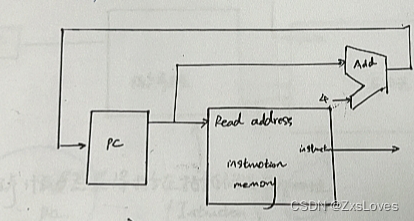

我们把整体的结构分成三部分来便于理解 1 指令寄存器 2 PC 3 自增Add(加法器)

PC叫程序计数器 用以保存当前指令的地址 并会用上半部分的加法器 增加PC的值获得下一条地址

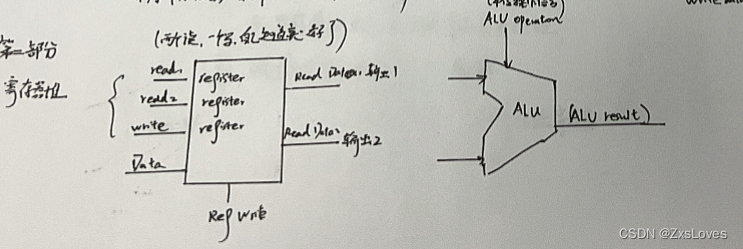

第二部分 寄存器堆 和ALU

为了保证指令的合理性和便利性

我们在指令寄存器上添加了多个端口 两个读取 一个写入 还有一个data 传输用来接收 来自data memory传输的信号 然后有两个输出

第三部分就是一个Data memory 和 立即数的扩展

将整个电路图进行组合就可以形成 一个简易处理多条指令的 CPU结构