课程链接:

计算机组成_北京大学_中国大学MOOC(慕课)

5 - 3 - 503-运算指令的控制信号(14-'58-'-')_哔哩哔哩_bilibili

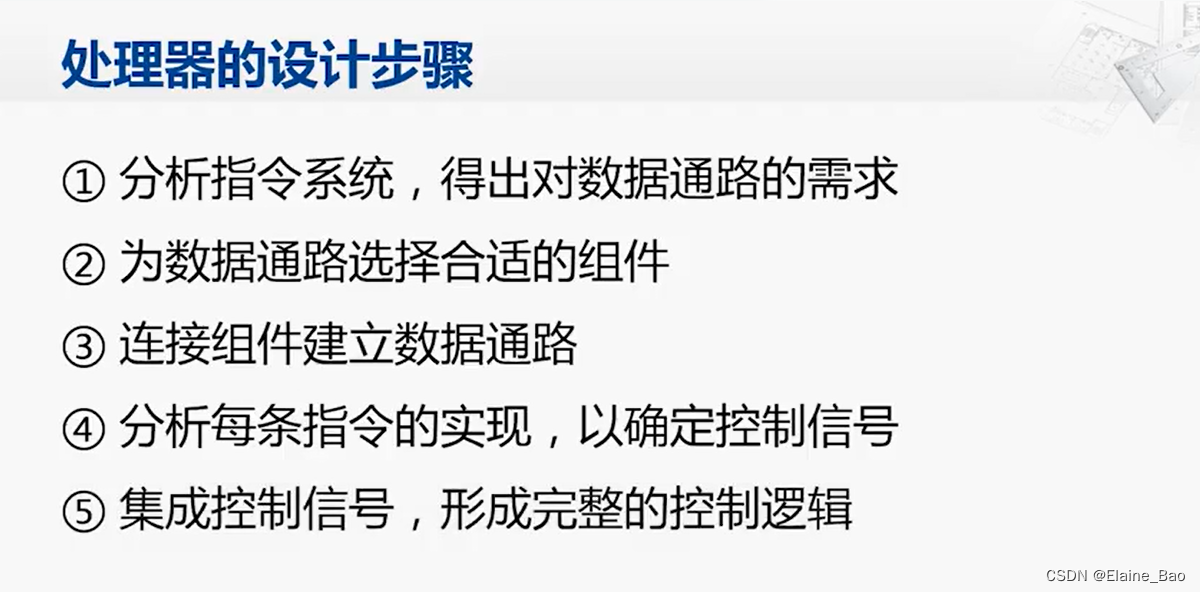

【计算机组成 课程笔记】5.1 处理器的设计步骤-CSDN博客 中介绍了处理器的设计步骤中的前三步,接下来我们继续介绍控制信号相关的逻辑。

4. 确定控制信号

1. 运算指令的控制信号

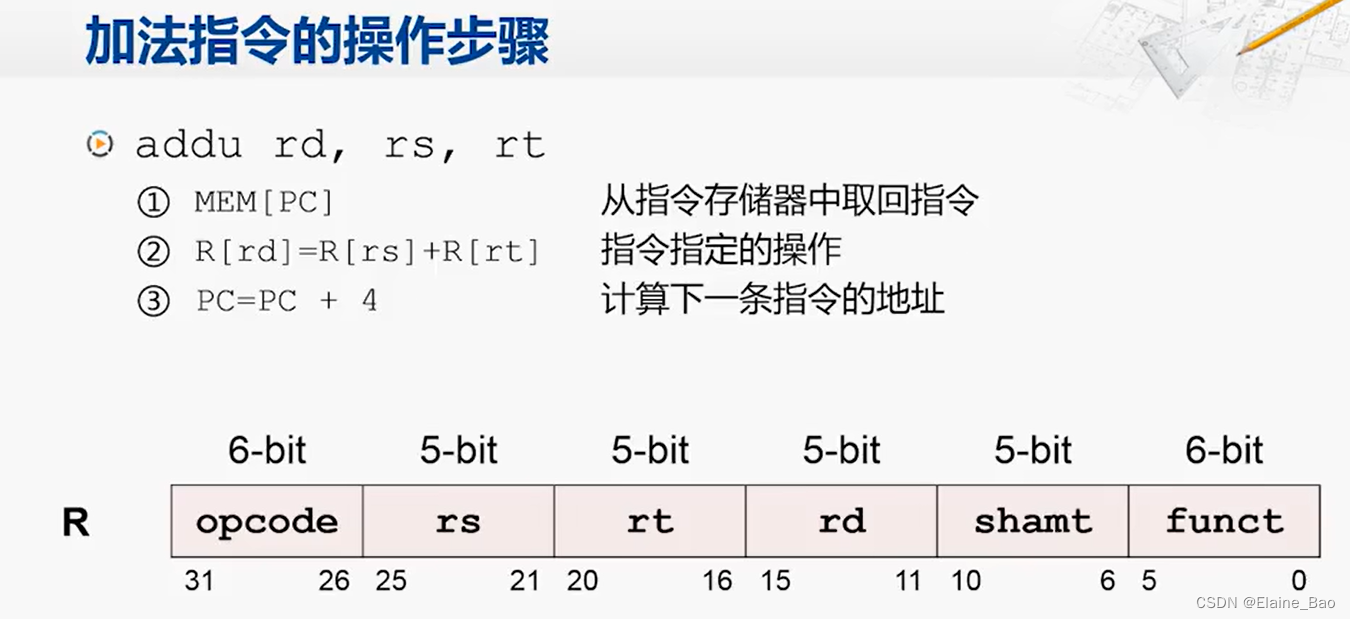

以加法指令为例。加法指令的操作可以分为三个步骤,首先从指令寄存器中取回指令;然后将rs和rt指定的寄存器的内容相加,运算结果保存在rd寄存器中;最后是计算下一条指令的地址,由于加法指令是顺序执行的,所以PC=PC+4。

那我们依次来看这些步骤。

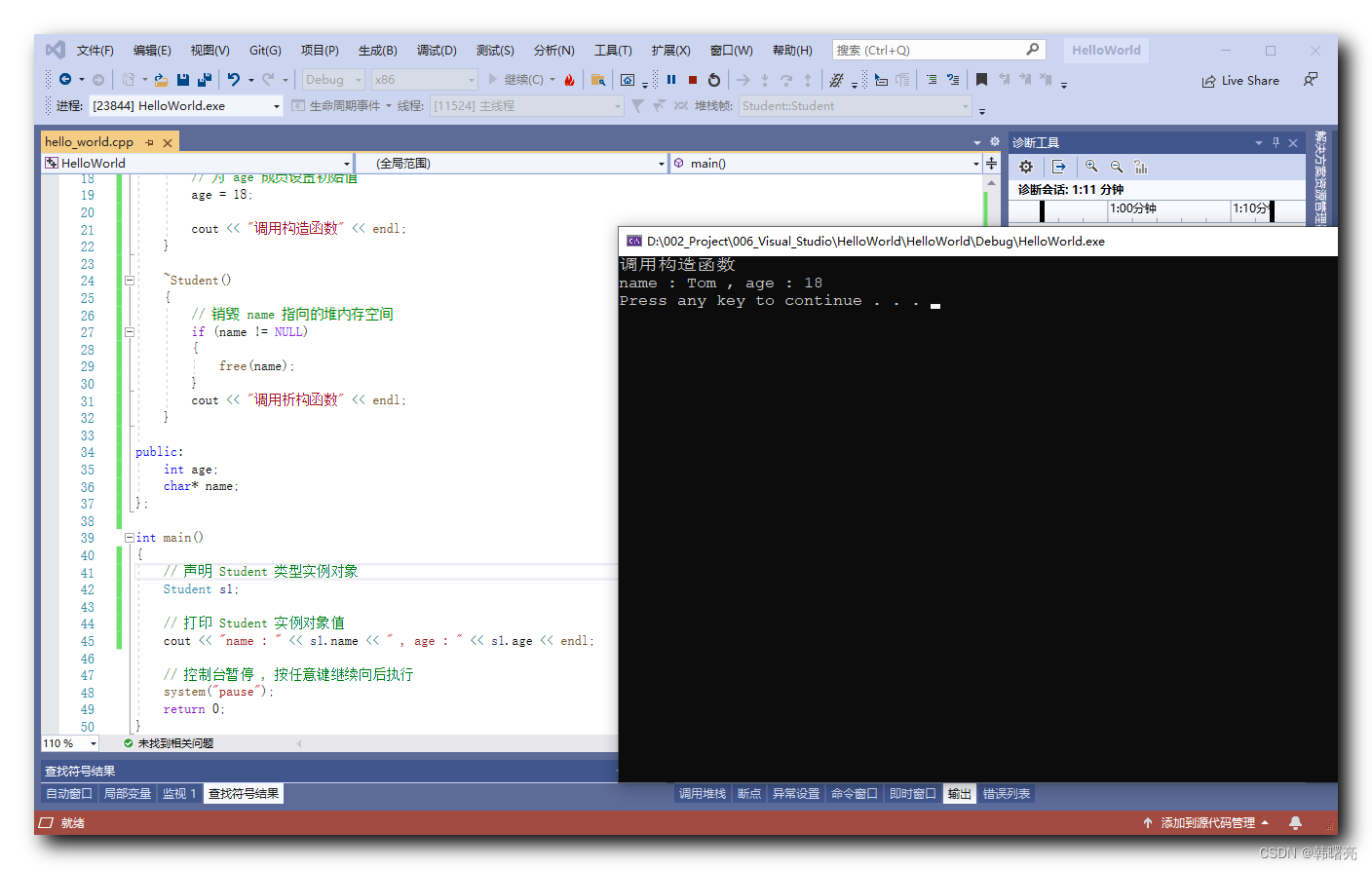

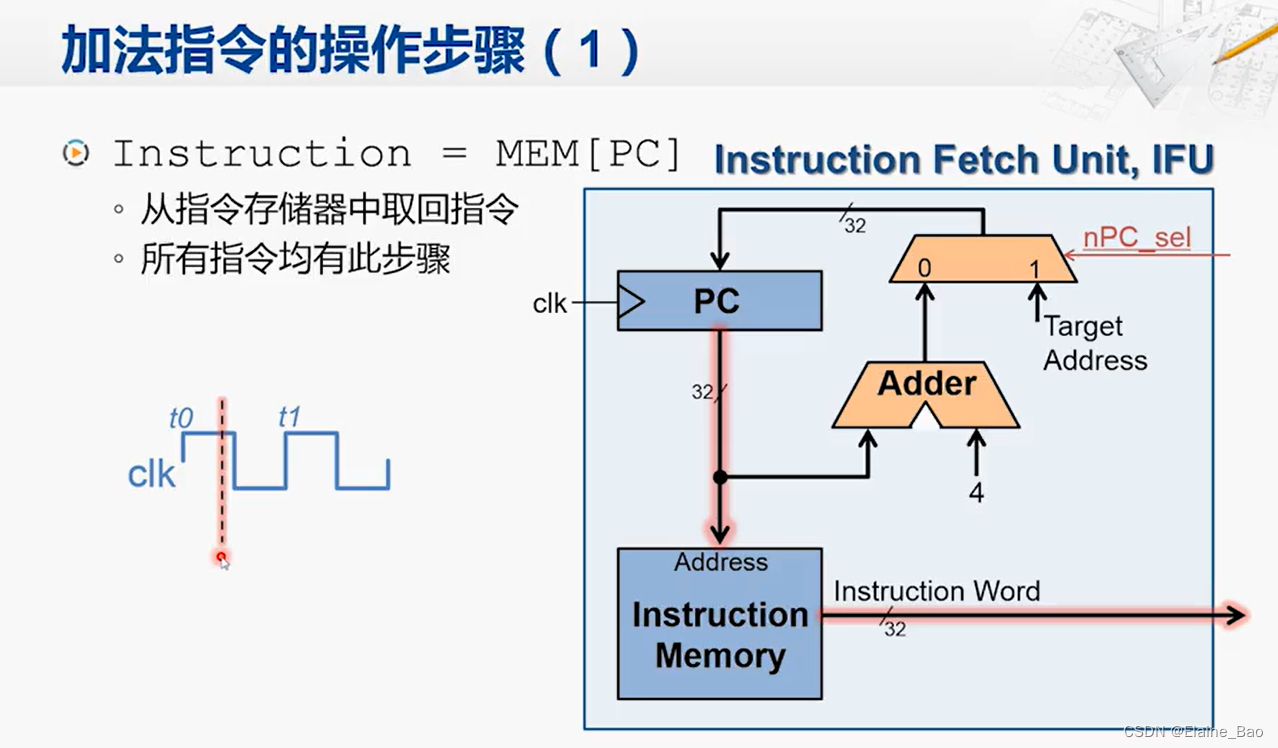

对于第一步来说,并不是加法指令特有的,所有指令都有这个步骤。这个操作是在取指部件IFU中完成的。在t0时钟上升沿之后很短的时间,PC寄存器的输出已经稳定,它的输出就是当前要取回的这条指令的地址,这个信号会连接到指令存储器的地址输入端,那经过一小段访问时间之后,指令寄存器就会将这个地址所指定的存储单元中的内容放在其输出端,也就是我们要取回的指令的二进制编码。

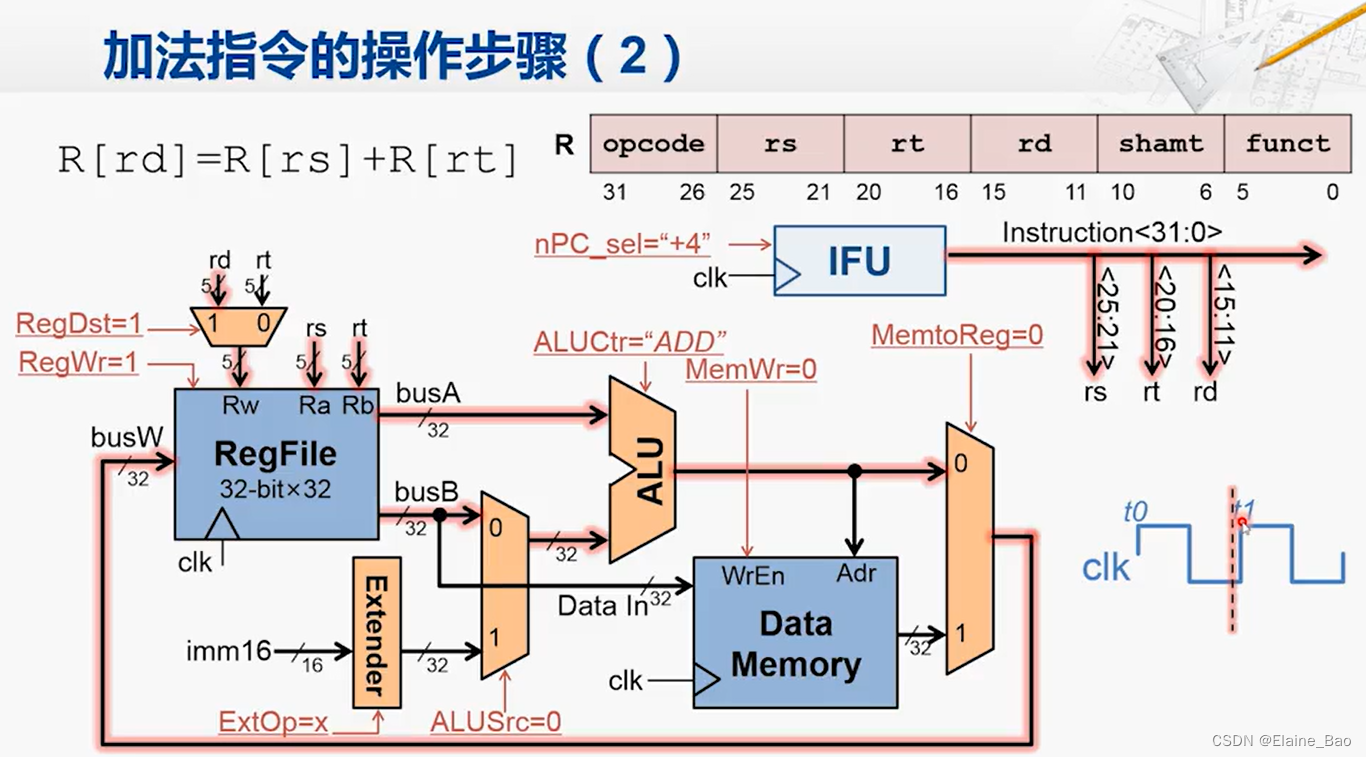

第二步我们要执行加法运算。不过运算前我们还要从寄存器中取操作数,寄存器的地址是在刚才取回的指令编码中的,根据R型指令的位域分布,我们可以从32位指令中选取对应的部分,例如25-21位组成rs,20-16位组成rt,15-11位组成rd。这三个信号就会被连接到寄存器堆的输入端,这样rs所对应的寄存器的内容就会输出到busA端,rt所对应的寄存器的内容会输出到busB端。

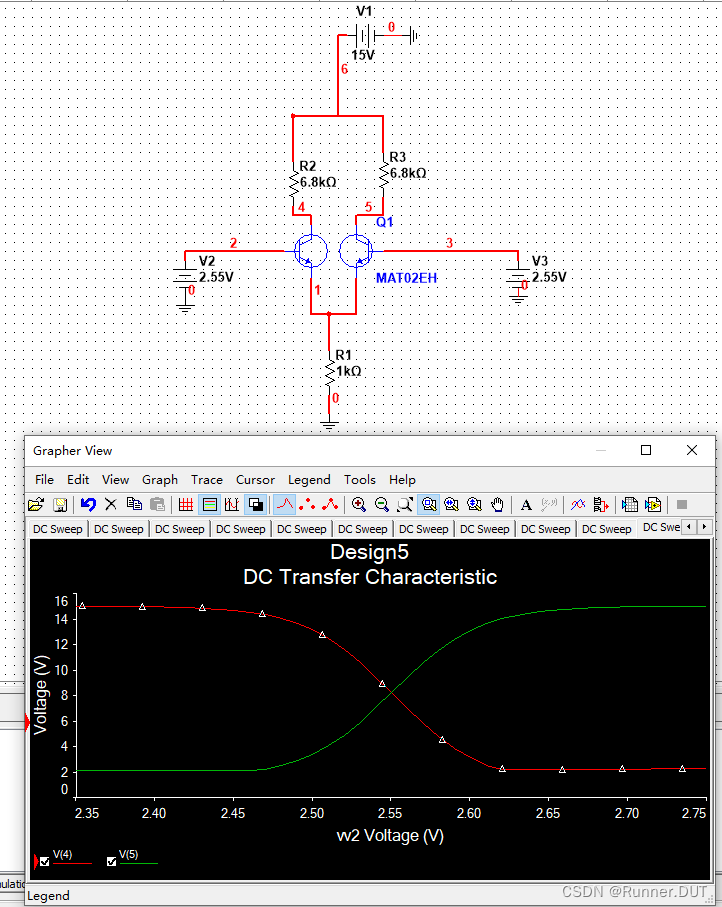

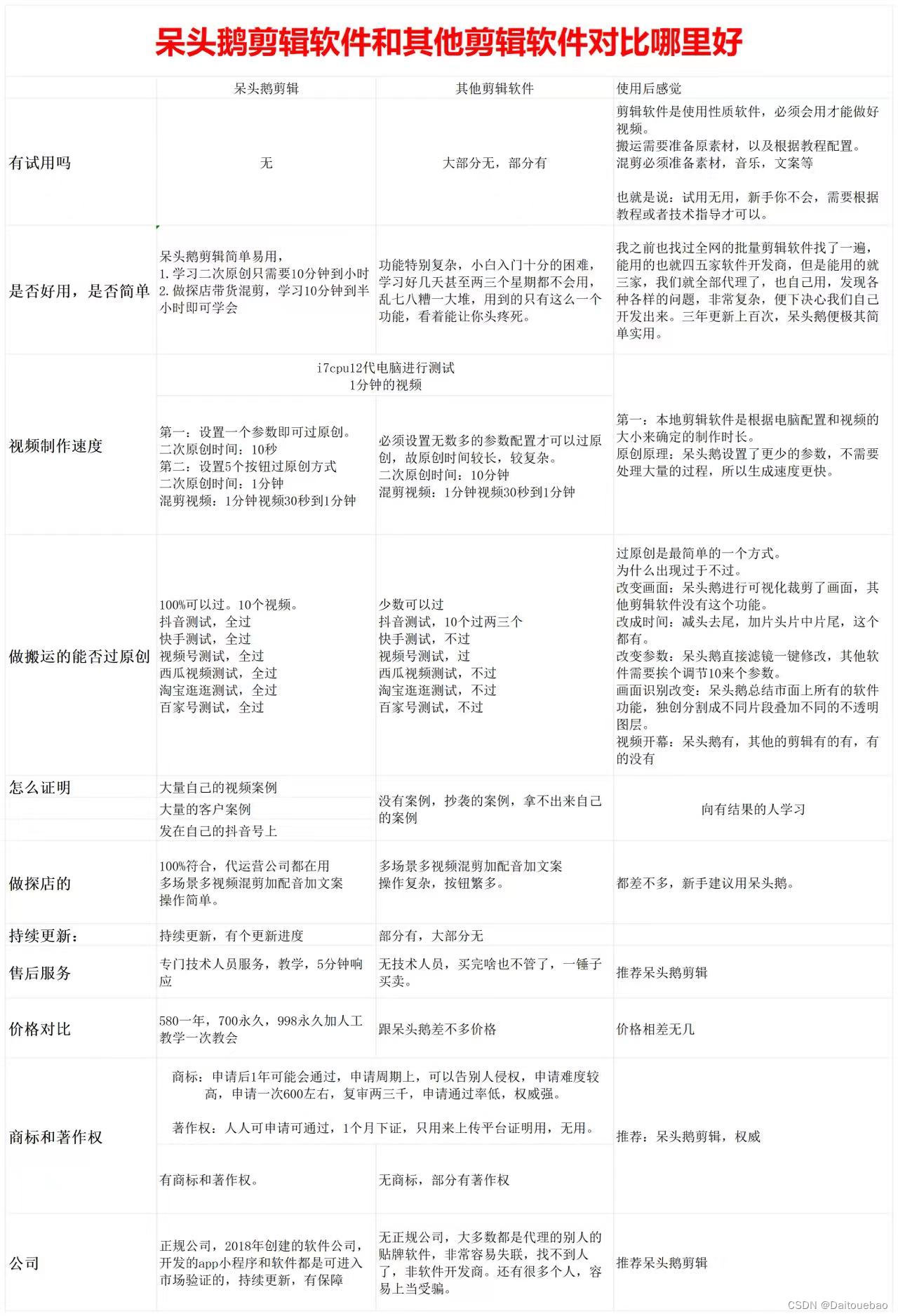

接下来对这些数要做哪些操作,就由标成红色的控制信号们来决定了。下图给出了加法运算所需要的控制信号的值。

最后一步,更新PC寄存器的内容。除了分支指令以外,其他指令都是顺序执行,因此PC=PC+4。当时钟上升沿t1来临时,PC寄存器就会更新会PC+4。

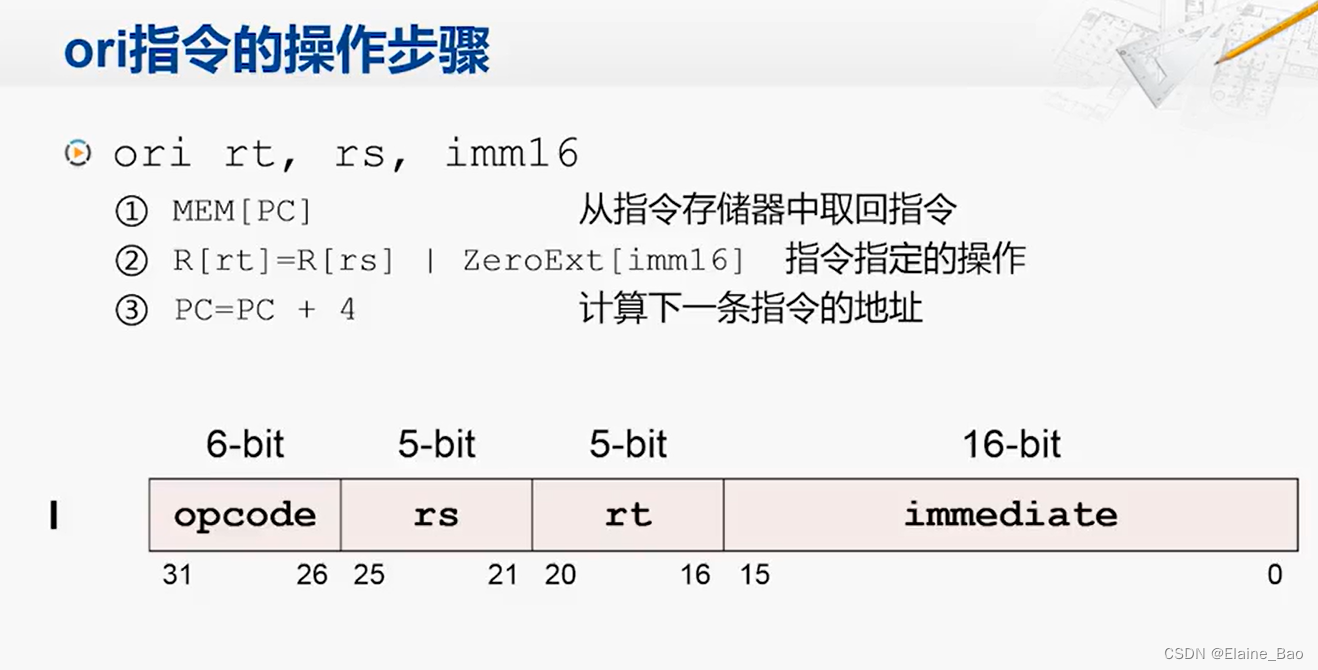

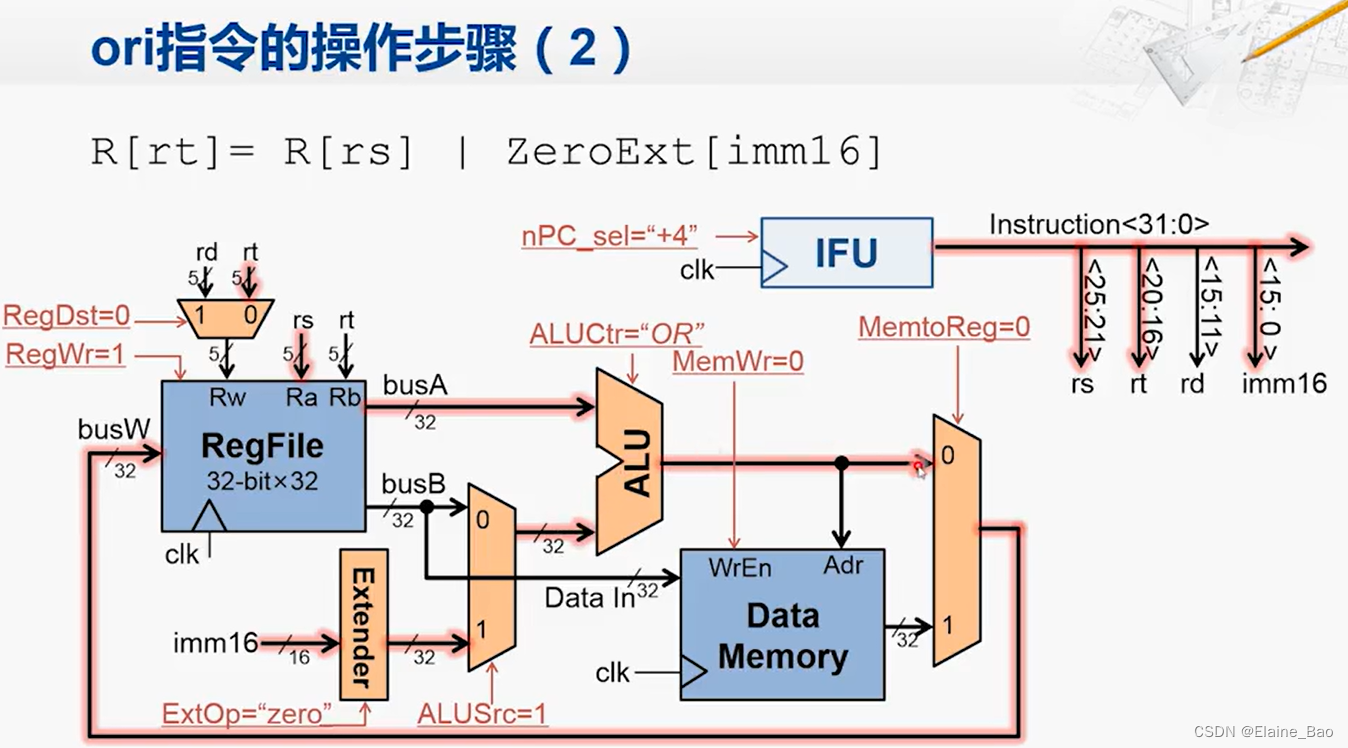

我们再来看另一类指令,运算指令中I型格式的指令,以逻辑或指令为例。这条指令同样也分为三步,其中第一步和第三步和之前的加法指令一致。第二步是rs寄存器中的内容和16位立即数进行零扩展以后的32位数进行或运算,结果保存到rt寄存器中。

由于I型指令的15-0位是立即数,因此和刚才加法指令IFU的输出不同的是,我们要再加一组信号,表示低16位的立即数。这个信号也会连接到数据通路上,只是连接的位置有所不同,连接到了扩展功能部件。

那根据这条指令,控制信号又该如何设置呢?如下图所示。

2. 访存指令的控制信号

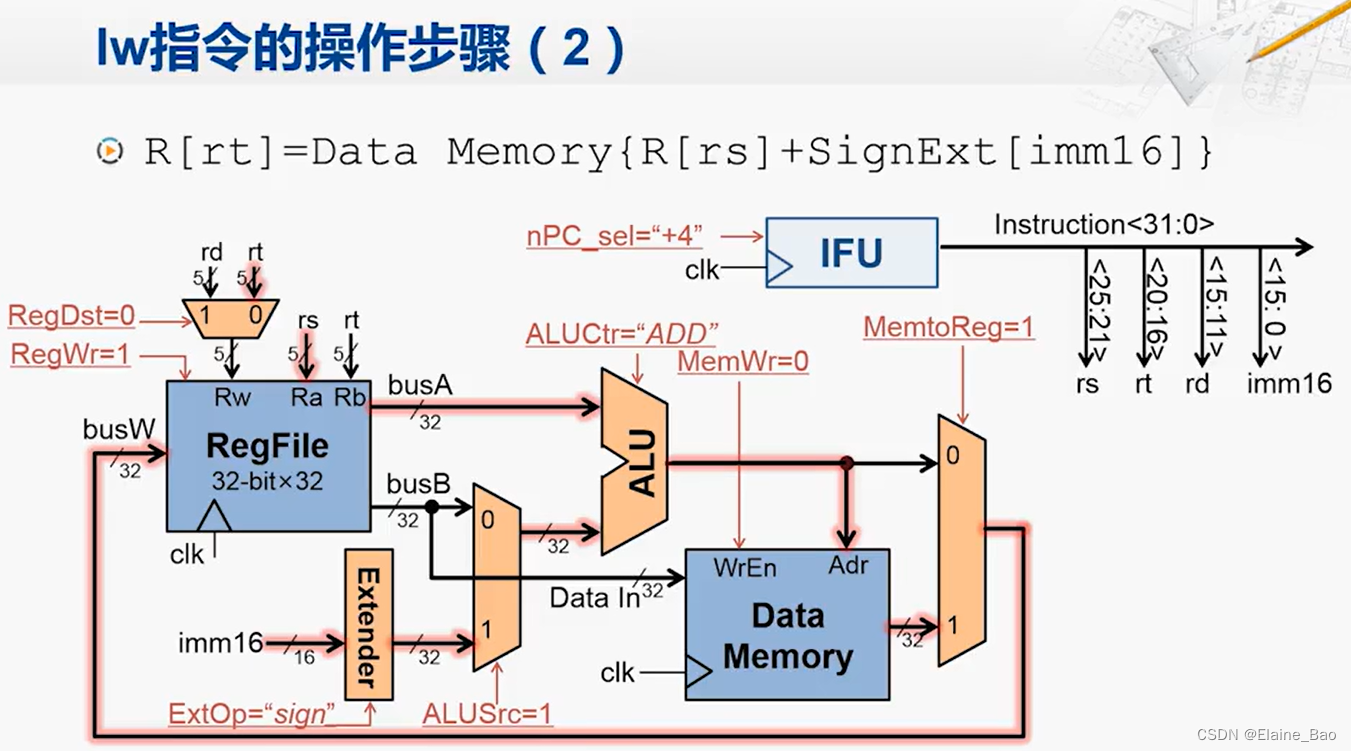

对于LOAD指令,第一步和第三步与运算指令都是一样的。在这里我们只讲解第二步相关的操作。

这是我们的数据通路,如果当前IFU取得的是一条LOAD指令,这些控制信号会如何设置呢?

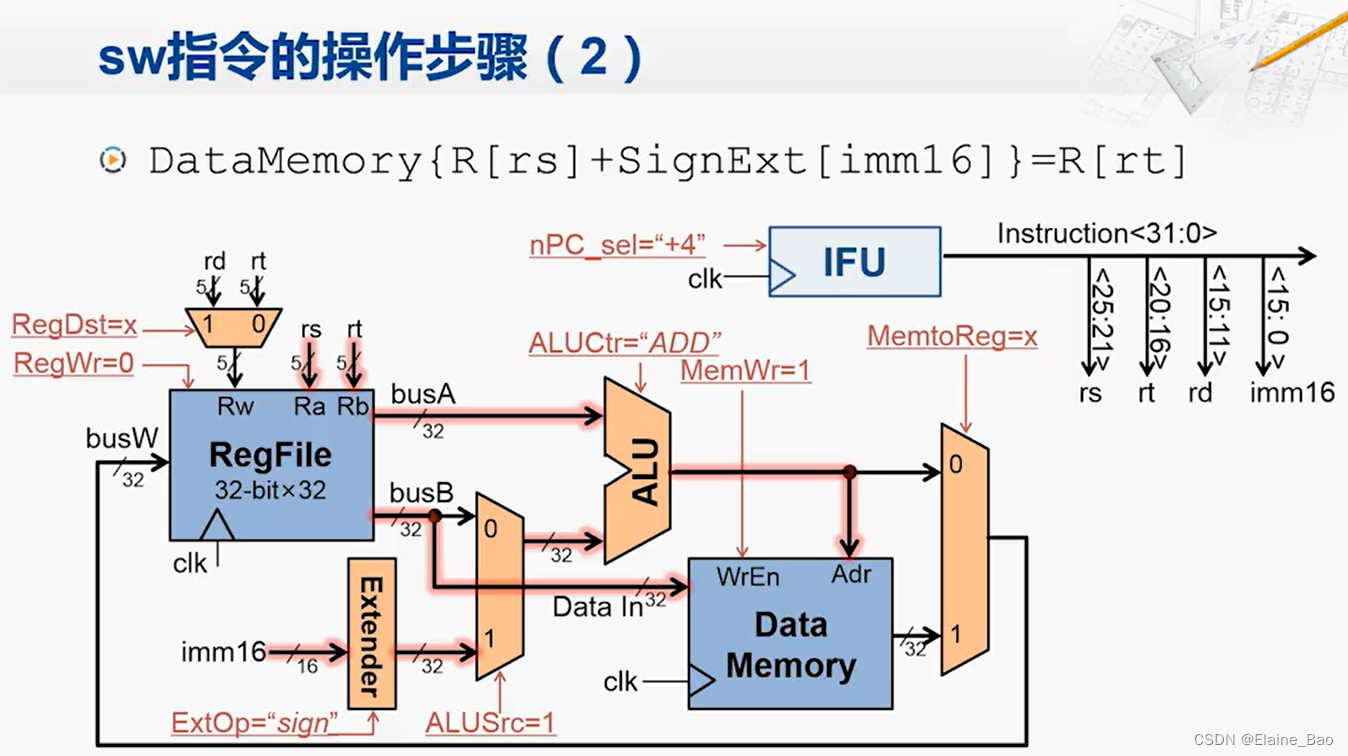

然后我们来看STORE指令,STORE指令我们也只看第二步相关的操作。

3. 分支指令的控制信号

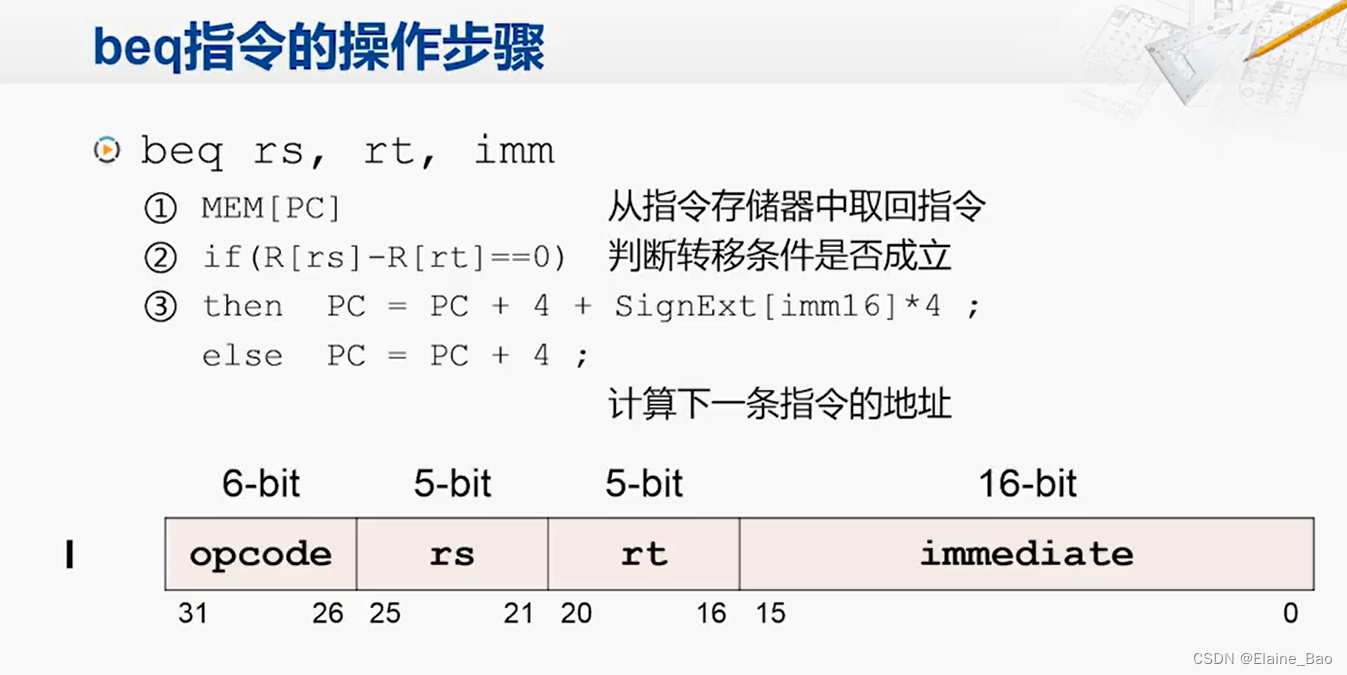

分支指令是一类特殊的指令,它能够改变程序的流向。beq指令的操作同样可以分为三步,第一步同样是取指令;第二步是判断rs和rt两个寄存器的内容是否相等,可以通过一个减法来进行判断;第三步是更新PC寄存器,对于beq指令来说,所谓的分支就是如何改写PC寄存器,所以它的重点在于第三步。当第二步的转移条件不成立时,和其他指令一样,顺序执行,则PC=PC+4。而如果转移条件成立,则需要跳转到PC+4+立即数的符号扩展*4,也就是说beq指令中所携带的这个立即数表示的是转移目标地址和下一条指令地址之间的差值,而且这个差值是以4个字节也就是32位为单位的。这个规则是在指定MIPS指令系统时约定的。

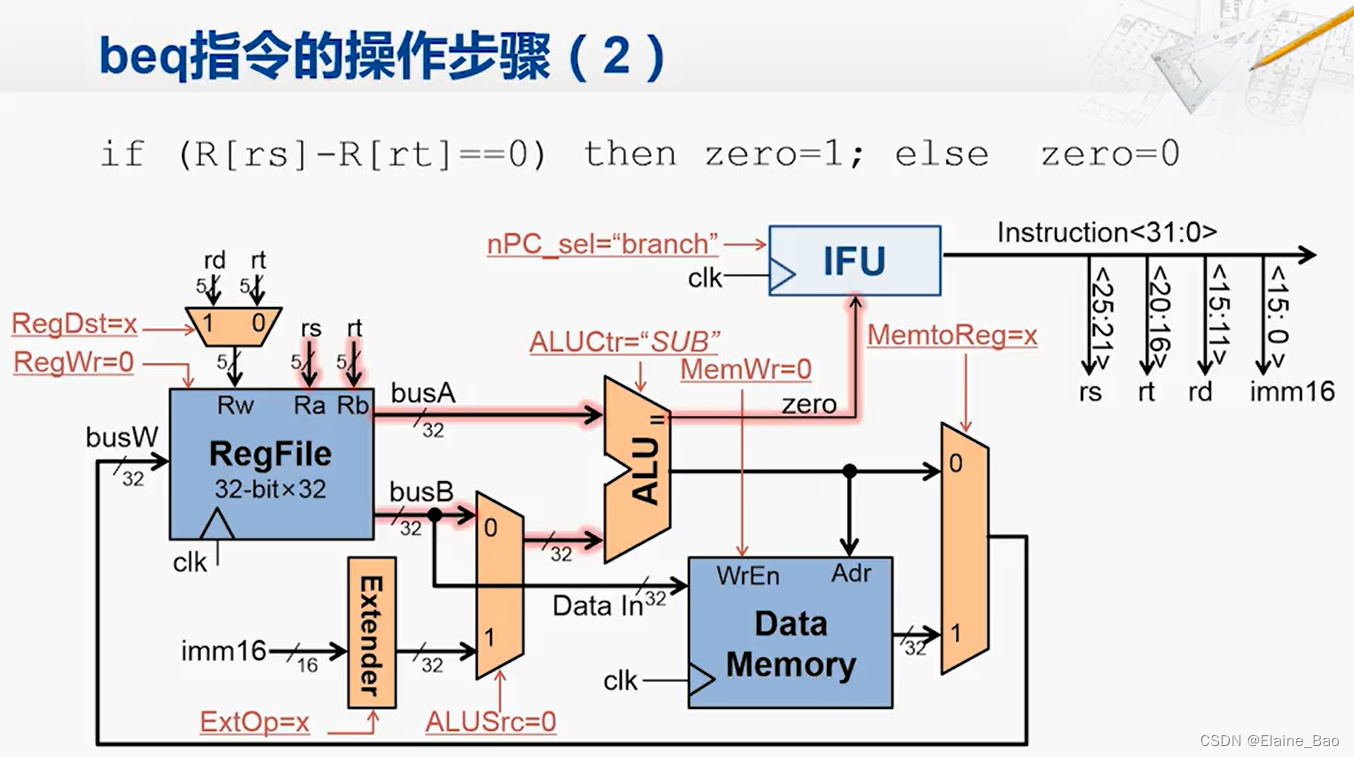

接下来我们看一下如何实现相应的控制信号。我们直接来看第二步。这一步包括从寄存器中取出两个操作数进行减法运算,这个部分和之前的减法指令是一样的,因此现有的结构不需要修改就可以完成减法的功能。但是对于==0的判断是之前没有的,判断一个数是否等于0对于ALU来说是很容易的,所以我们在ALU中增加一个输出,叫做zero,如果运算结果为0,zero信号会被置为1。

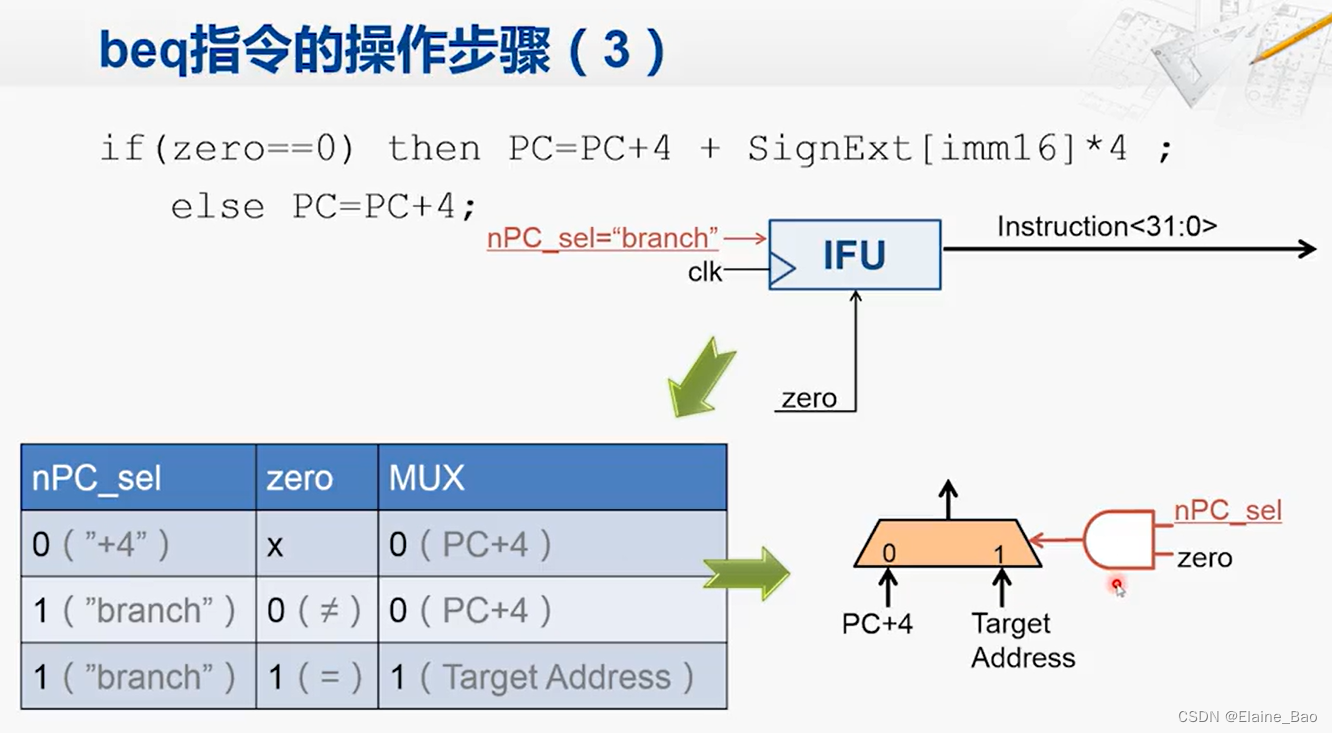

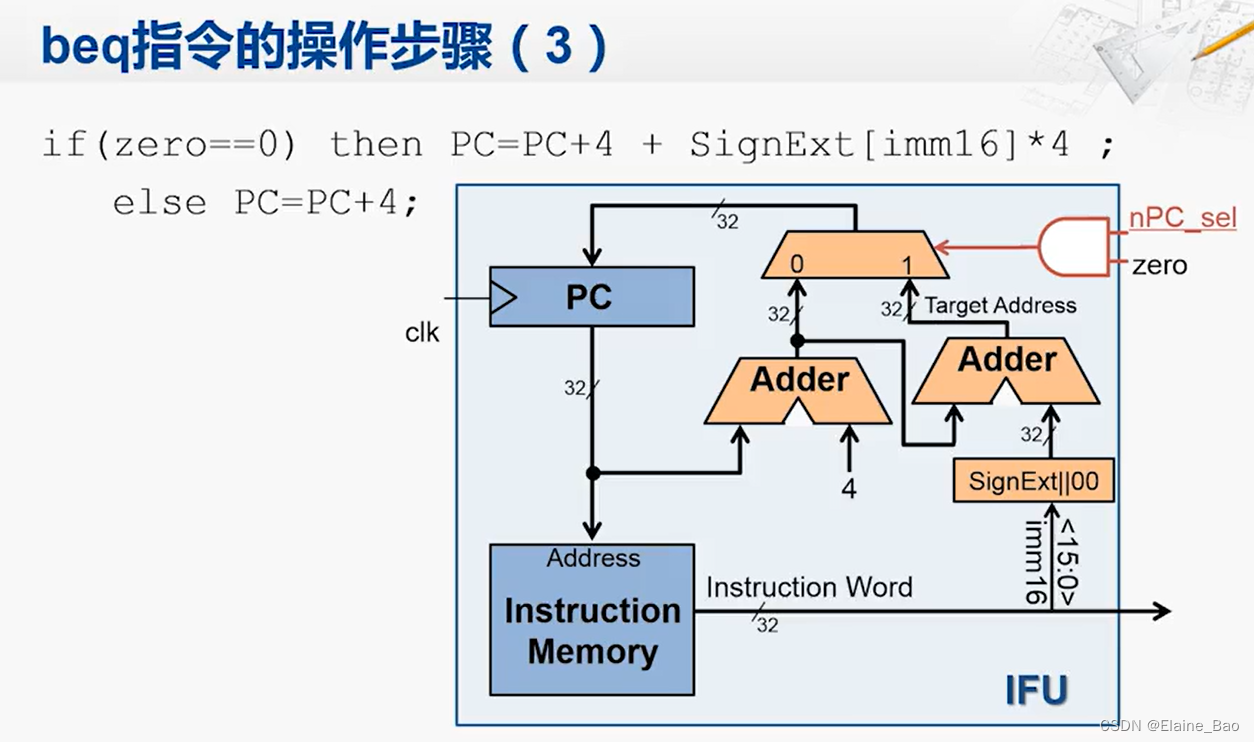

然后来看第三步。现在对于IFU来说,它有了两个输入的信号,一个是之前就有的nPC_sel,还有一个是刚增加的zero。对于nPC_sel信号来说,如何选择呢?不妨把输入列一个表,当nPC_sel=0时,PC=PC+4,当nPC_sel=1(branch)时,zero=0,则PC=PC+4,zero=1, 则PC=Target Address。所以可以看出这里可以用一个与门来实现。

那基于这样的分析,我们就可以对IFU进行改造,从而满足beq指令的需求。另外对于Target Address如何得到,也需要进行一定的扩展:首先需要进行符号扩展,其次将其左移两位,也就是完成*4的操作,最后再+PC+4,得到跳转的地址。

5. 集成控制信号

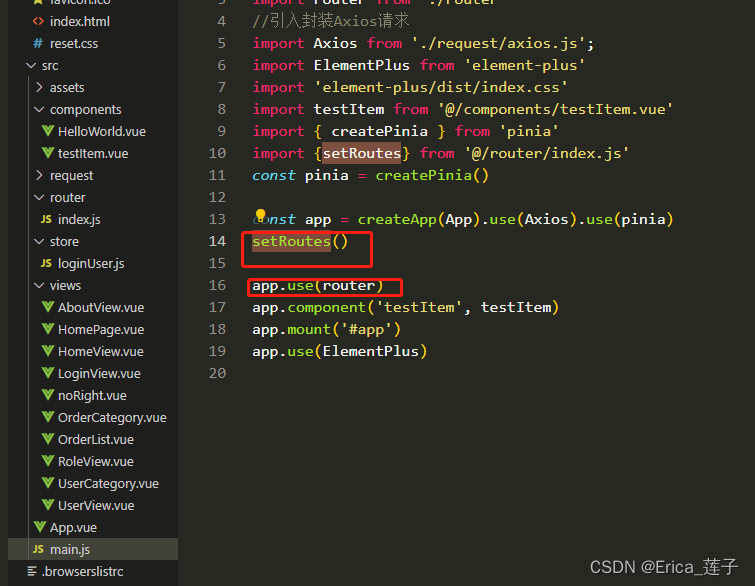

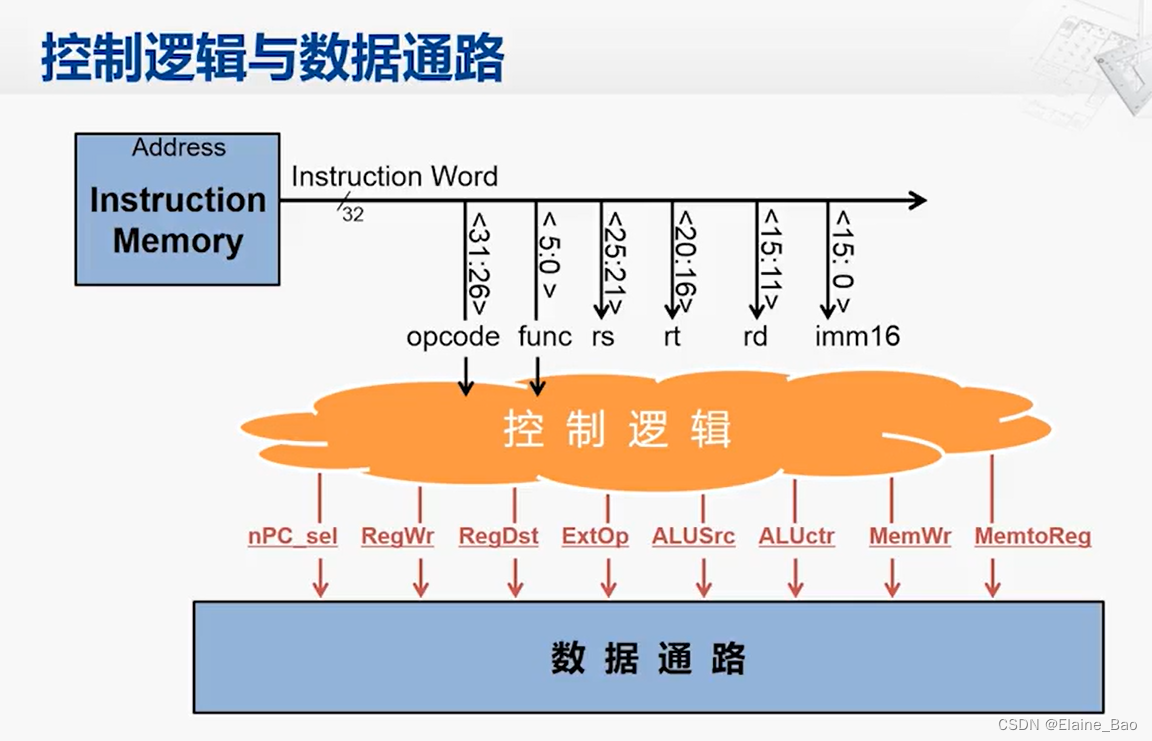

现在我们已经知道对于每一条指令,每一个控制信号应该赋予什么样的值,但这些信号的值是如何自动产生的呢?

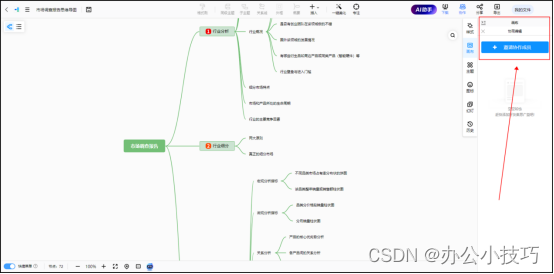

我们把之前的控制信号都集合在一起,可以知道控制整个数据通路运转的控制信号一共有8个。我们已知的指令编码中除了之前提到的数据位域以外,还有两个位域,opcode和func,之前未提及,但是它们和控制信号有着密切的关系。

具体是什么关系呢?我们列一个表,不同的func和opcode域和控制信号的值之间,存在着某种联系。

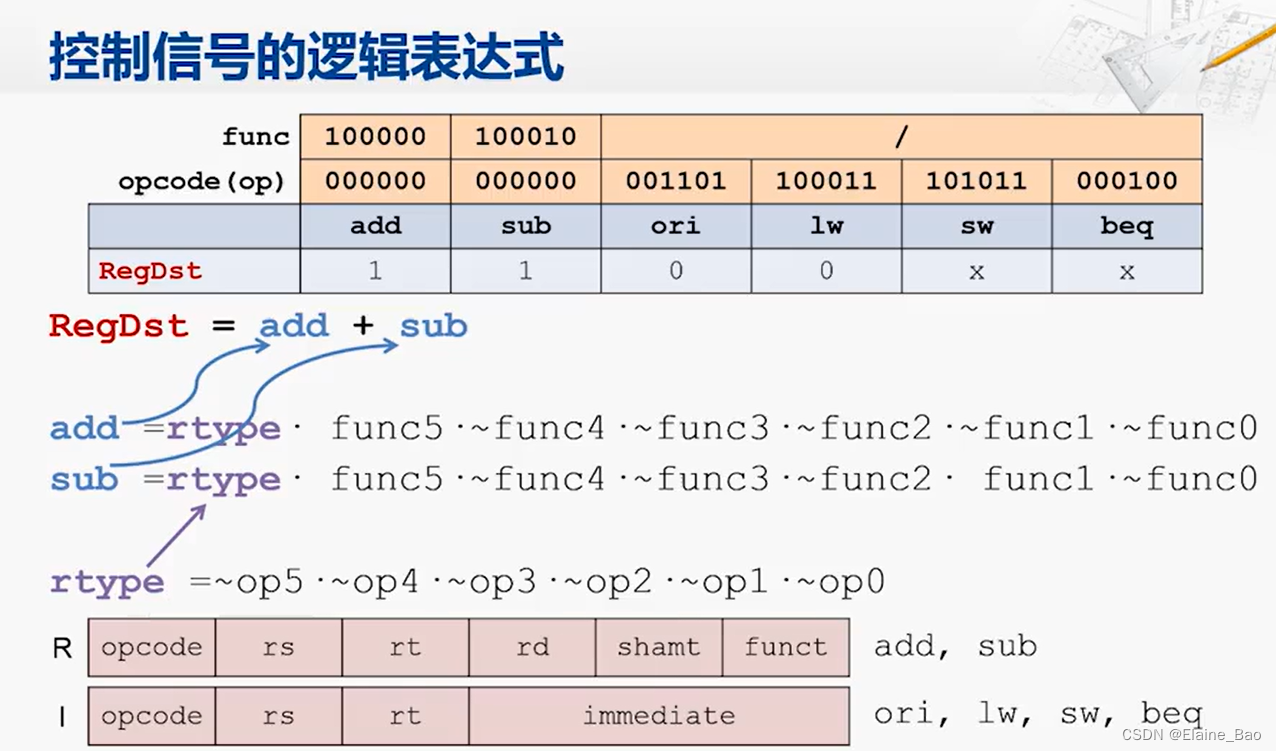

以RegDst信号为例,只有当前是加法或减法操作时,这个控制信号才需要为1,其他时候都为0就可以了。那加法和减法又是如何判断呢?对于加法来说,首先它是一条R型指令,同时它的func域的第5位为1,其他位都为0,因此我们可以把add信号表示成以下的公式。用类似的方法也可以得到sub信号。有了这个表达式,我们就可以用与门和非门画出产生这个控制信号的电路图来,这样对于这个控制信号来说,它的控制逻辑就能够自动产生了。

用同样的方法还可以得到其他控制信号的逻辑表达式。

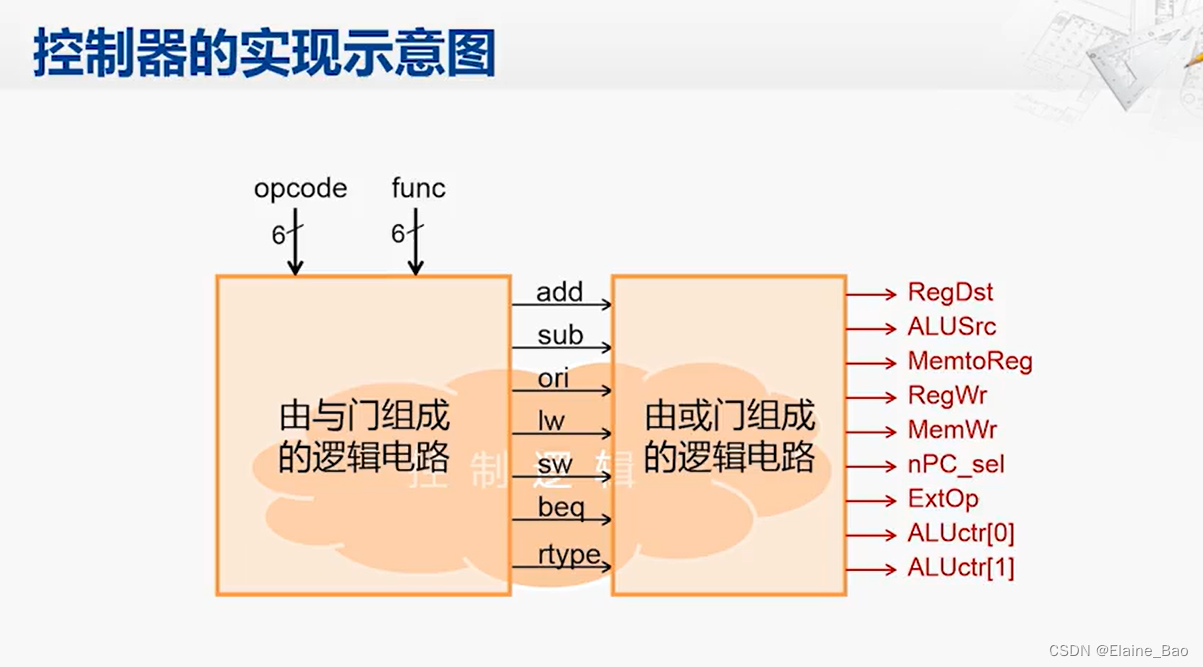

然后我们可以画出一个控制器的实现示意图来。我们把opcode域和func域接到一组由与门和非门构成的逻辑电路中,这个逻辑电路就实现了add,sub,rtype,ori,lw,sw,beq的计算,从而产生了一组中间信号,再将这组信号接入由或门组成的逻辑电路,最后就产生了我们想要的所有的控制信号,这样就有了控制器的实现。

有了这个控制器,处理器就能一条接一条地取回指令,并自动地执行下去。