目录

1.1 总线状态

1.2 ZQ校准

1.3 CE_n引脚缩减机制

1.4 差分信号

1.5 Warm up周期

1.6 从SDR到NV-LPDDR4的技术发展总结

1.1 总线状态

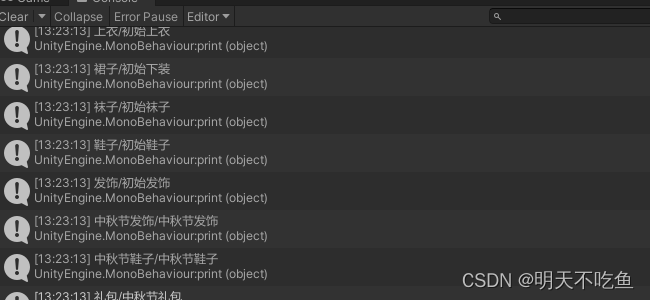

SDR 的总线状态:

NV-DDR总线状态:值为11b的ALE/CLE 用于数据传输。总线状态在CLK的上升沿开始,持续一个完整的CLK周期。因此,对于数据周期,每个总线状态会有两个数据输入周期或两个数据输出周期。 Idle总线状态用于在一个命令周期、地址周期或一个数据流(stream of data)之后中止 DQ 总线上的操作。CE_n 的值仅可在总线状态为 idle(例如, ALE 和 CLE 都被清为 0)且该时钟周期内没有数据传输时被改变。

NV-DDR2、NV-DDR3、NV-LPDDR4总线状态:

1.2 ZQ校准

ZQ 校准是可选的,但对超过 400MT/s 速度的 NV-DDR3 接口是推荐的。ZQ校准对 NV-DDR2 接口是可选的。对于ZQCL(ZQ long calibration),ZQ校准是通过发送F9h命令来执行的,而对于ZQCS(ZQ short calibration),ZQ 校准是通过发送 D9h 命令执行的。 ZQ 校准用来校正 NAND Ron&ODT 的值。在初始化阶段需要比较长的时间来校正输出驱动和on-die termination电路,相对地,执行定期校正的时间会较短。

1.3 CE_n引脚缩减机制

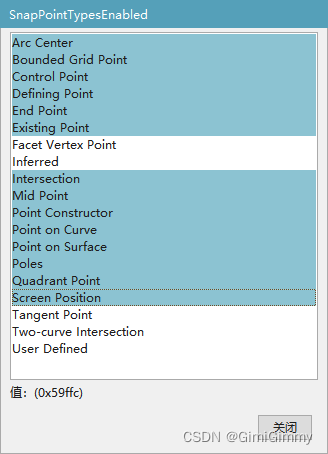

在高容量的设计中可能会有很多数量的 CE_n 引脚,这种设计会包含有很多 NAND 封装,每个封装有2到8个CE_n引脚。 CE_n引脚reduction机制可以让host的单个 CE_n引脚被多个NAND target复用,因此可以使Host需要的CE_n引脚数目大大减少。 CE_n引脚reduction机制可以使用在数据接口(SDR、NV-DDR、NV-DDR2、NV-DDR3、NV-LPDDR4)中。CE_n引脚reduction机制在初始化过程中,为每个 NAND target指定一个Volume地址。初始化完成后, host可以通过Volume选择命令来寻址特定的 Volume(例如,NAND target)。下图展示了一个使用CE_n引脚reduction机制的拓扑的例子。每个NAND封装都增加了ENi和ENo引脚(支持此机制的nand芯片要有这两个引脚),NAND 封装之间使用daisy chain连接。 Chain中第一个NAND封装的ENi没有被连接,而其它所有NAND封装的Eni引脚都连到前一个封装的ENo引脚。

下图展示了一个更复杂的拓扑。该拓扑中,多个 NAND target可以被连接到一个host CE_n信号上。

不是所有的拓扑都支持CE_n缩减机制。如果同一个nand封装内的两个nand target共享相同的数据总线,这时每个target应有一个独立的片选信号出到芯片封装外,host应使用不同的CE_n信号分别连接这两个nand target。

Eni的状态决定了此时的nand芯片能否接收指令。Eni在封装内是上拉的。如果Eni为高,且片选CE_n为低,这时就nand target可以接收指令。如果Eni为低,这时就nand target不可以接收指令。注意:芯片上电后的第一个指令是一个特殊场景,这时走的是初始化流程,详见3.5.2。

当CE_n为低并且NAND target没有被指定Volume地址时,ENo被device驱动为低。当与 NAND target关联的 CE_n为低并且该 NAND target被指定了一个Volume地址时, ENo被device驱动为三态(这样做相当于前一级的volume地址被指定后,下一级才能访问,这有点不合理)。当共享一个ENo信号的所有目标NAND 的 CE_n 信号为高时,ENo被device驱动为三态。注意,在Volume 地址被指定后,Eno会被下一个封装的Eni拉高。

当一个Volume地址被指定给一个NAND target后,该Volume地址会变为取消选择状态(deselected),并忽略 ENi引脚直到下一个电源周期。

为了被选定来处理命令,一个Volume选择命令应该被发送到host对象,该Volume 选择命令使用之前被指定的Volume地址。在CE_n信号被拉高tCEH时间后,Volume上所有LUNs 返回之前的状态(参见 3.2.4)。

1.4 差分信号

一种用于高速操作的方法,使用RE_n和DQS的差分信号。一个互补的RE_n和互补的DQS信号构建的差分信号对(RE_t/RE_c 和 DQS_t/DQS_c)。差分信号可用于通过增强抗扰度(enhanced noise immunity)来提高信号完整性,还可以补偿因环境变化造成的边沿变缓或变陡。只有NV-DDR2、NV-DDR3和NV-LPDDR4接口支持差分信号。

device是否支持差分RE_n或差分DQS信号报告在参数 page 中。默认情况下,差分信号是被NV-DDR2、NV-DDR3 disable的,而NV-LPDDR4差分信号是强制使能的。Host可以通过NV-DDR2/NV-DDR3的配置特性(Configuration feature)来配置devic以使用差分信号,参见 5.31.2。互补的 RE_n(如 RE_c)和互补的 DQS(如 DQS_c)信号是单独被配置/使能的。

当选定的接口是NV-DDR2或NV-DDR3时,在 NV-DDR2/NV-DDR3 的配置特征(Configuration feature)中使能差分信号,差分信号有效。在使能NV-DDR2接口前,推荐使用 SDR 接口来配置 NV-DDR2/NV-DDR3的配置特征(Configuration feature)。 NV-DDR2/NV-DDR3 Configuration feature 中的差分信号设置状态被改变后,host应在发送接下来的命令之前,将 CE_n 转为高,以避免任何信号完整性的问题。

如果执行了RESET(FFh)操作,则差分信号会被disable。同步Reset(FCh)和Reset LUN(FAh)不影响差分信号。

1.5 Warm up周期

为了支持高速操作,在数据输出和数据输入时引入了warmup周期。Warmup周期仅在N-DDR2、NV-DDR3、NV-LPDDR4 接口中支持。数据输出/输入的 warmup 周期在一个数据输出 burst 开始时提供了 RE_n 以及对应的 DQS 的额外(extra)跳变。这个额外的 RE_n/DQS 跳变期间不会有任何数据传输。 额外周期的数目通过 NV-DDR2/NV-DDR3/ NV-LPDDR4 的配置特征地址(Configuration feature address)来设置,参见 5.31.2。周期数的定义包含一个完整数据输出周期(RE_n 和 DQS的上升沿及下降沿)。对数据输入和数据输出来说,warmup周期都是可选的,如果使用了 warmup 周期,不需要配置为相同值。

warmup 周期适用于所有命令,包括SDR命令(参见4.4)。当某种数据传输类型使能了 warmup 周期,则 warmup 周期应该在该类型中每个数据突发开始时开始。如果 host 暂停了数据传输,之后有重新恢复了传输,在此期间没有退出并重新进入数据突发,在这种情况下,host 不能再次发送 warmup 周期。退出和重新进入数据突发的操作通过拉高 ALE、 CLE 或 CE_n 来执行(不使用 WE_n 来锁存)。如果暂停数据传输一段时间后又恢复传输时没有重新发送warmup 周期,则 host 要小心避免信号完整性问题。

warmup 周期在选中 NV-DDR2 或 NV-DDR3 接口后有效,并通过 NV-DDR2/NV-DDR3 的 Configuration feature 来使能。对于NV-DDR2,推荐使用SDR接口来设置NV-DDR2/NV-DDR3 Configuration feature。如果在NV-DDR2或NV-DDR3有效时使能了 warmup 周期,则在 Set Feature 命令完成后, warmup 周期可以用于接下来的所有命令。下图展示了一个数据输出时 warmup 周期的例子,该例中 warmup 周期数为 2。如图所示,数据的第一个 byte在 DQS 的第三个上升沿开始传向host。

1.6 从SDR到NV-LPDDR4的技术发展总结

为了满足nand flash容量越来越大、接口速率越来越快、传输可靠性要求越来越高,ONFI规范从1.0到5.1逐步引入了一些新技术,这些新技术的引入和DDR SDRAM的接口技术发展路线有点相似,在此将这些新技术一一列举,可能不全,欢迎补充。

1、由异步传输变为同步传输,单边沿采样变为双边沿。

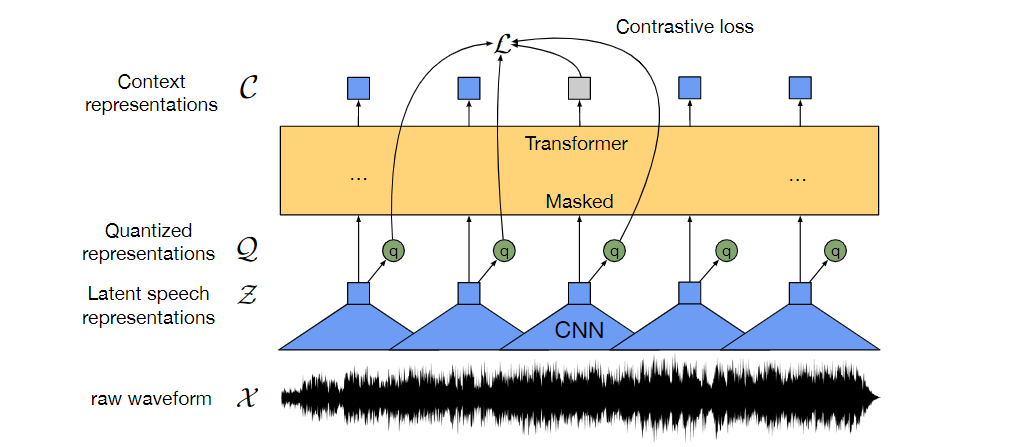

ONFI 1.0定义的就是异步的SDR接口,使用异步信号WE_n、RE_n控制命令、地址、数据的输入和输出。ONFI 2.0,为了提升采样率,使用了双边沿采样模式,如果仍使用WE_n、RE_n的双边沿进行采样,由于每个数据输出到每个IO延时是不一样的,尤其是读的时候,host发出的RE_n信号不清楚flash各个IO的输出时间,这就导致时序裕量很难满足,于是采用了同步时钟设计,引入了CLK,为了区分数据的传输周期,还引入的DQS,CLK和DQS对齐,读操作时,DQS由flash器件发出,与DQ边沿对齐,host端将DQS delay 1/4周期后进行数据采样,写操作时,DQS由host发出,与DQ中心对齐,flash直接使用此DQS信号进行采样。这个处理方式与SDRAM到DDR的升级是一样的,只是CLK和DQS还不是差分信号。

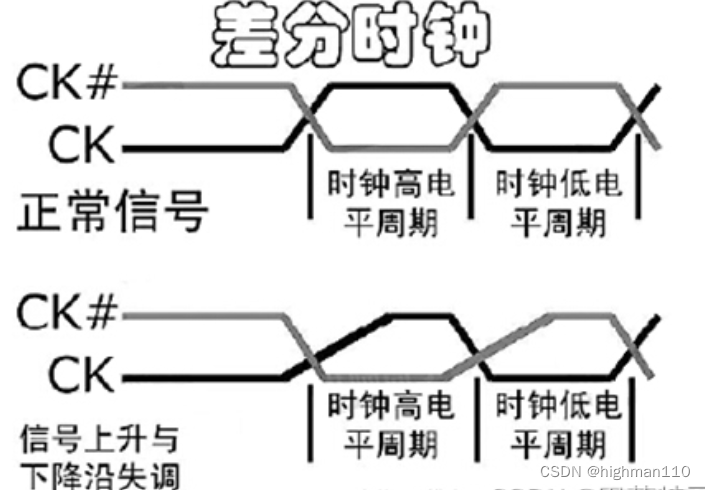

2、引入差分信号,在NV-DDR2之后,DQS和RE_n为差分信号。

差分信号由于数据是在时钟的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就对采样信号的上下沿间距有了精确的控制的要求。一般说来,由于运行环境的变化,DQS的上下沿间距可能发生变化,此时与其反相的DQS#就起到纠正的作用,因为,DQS上升沿快下降沿慢,DQS#则是上升沿慢下降沿快。也就是,与DQS反相的DQS#保证了触发时机的准确性。

3、在NV-DDR2之后引入片on die termination和ZQ校准,能够在高速传输时提升信号完整性。

4、在NV-DDR3之后增加读写训练、VREFQ训练和均衡,进一步提升信号完整性。

5、在NV-LPDDR4增加DBI,降低运行功耗。

6、供电从3.3、1.8到1.2,降低运行功耗。