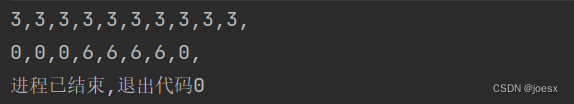

目录

一、概览

二、UltraScale架构

2.1 UltraScale/UltraScale+特点

2.2 与7系列CLB差异

三、 CLB结构

3.1 LUT

3.2 FF

3.3 多路选择器Multiplexers

3.4 进位链Carry Chain

四、应用

4.1 分布式RAM

4.2 移位寄存器

4.3 进位链Carry Chain

五、参考资料

一、概览

二、UltraScale架构

2.1 UltraScale/UltraScale+特点

UltraScale架构是赛灵思器件中一种变革性的架构,可以处理大规模的I/O和存储带宽,并且因为有许多复用的内部块单元,从而具有更强的扩展性,在降低功耗方面也优于7系列器件。UltraScale架构包含了Kintex,Virtex两个系列。

UltraScale+是在UltraScale架构的基础上进行了优化,相比Ultrascale,降低了BOM成本,在高性能与经济性间取得更好的平衡,同时拥有大量的功耗方面的配置。UltraScale+架构有Kintex,Virtex,Zynq 三个系列

2.2 与7系列CLB差异

与7系列类似,Ultrascale架构的CLB包含了6输入的查找表LUT,两个LUT5,分布式存储器和移位寄存器,高速进位逻辑,更宽的多路复用器,FF/Latch。

a) Slice:与7系列的一个CLB包含两个Slice不同的是Ultrascale中一个CLB只有一个Slice,

b)控制信号:每个CLB包含4个时钟使能信号,在置位/复位信号前有可取反的设置

c)分布式RAM:写使能信号WE和FF的时钟使能信号分开,在一个slice中,写使能信号可以直接和三个直接输入组成8个独立的写使能信号

d)LUT:LUT可直接输出,或和选择器组合输出,也可通过FF输出

e)FF:所有的FF都可配置成边沿触发的触发器或锁存器

f)Carry:单个CLB的进位逻辑扩展到了8bit,可实现更快的运算,每个CLB一条进位链

Ultrascale的CLB是单列结构,先比之前的双列结构

a) 可消除之前的I/O数量和逻辑布局大小的相互影响,

b) 解决了电源和接地模块布局位置的限制,电源和接地模块可放置到器件的任意位置

c) 可以将不同的IP块相互独立分布在资源的四周

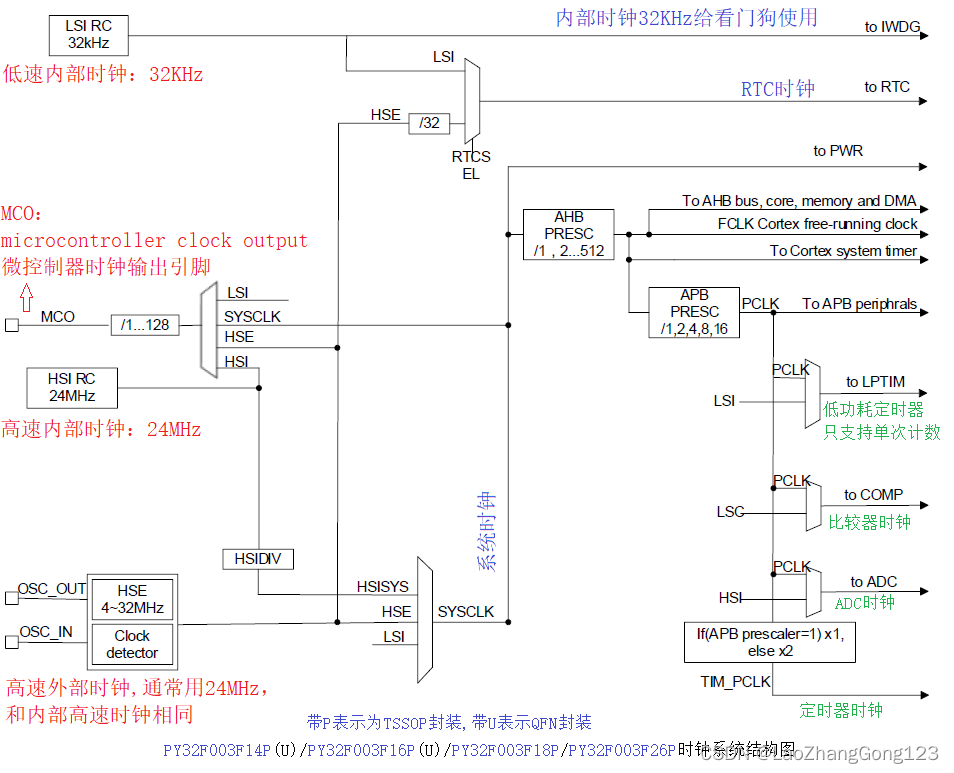

Ultrascale的时钟域CR(Clock Region)和7系列存在差异,CR是以tiles模块排列的。一个CR包含了60个CLB,24个DSP,12个块状RAM,在中间位置存在一个水平时钟脊HCS。HCS由水平布线资源和水平分布资源,叶子时钟缓冲器,时钟网络连接单元,和时钟根组成,关于详细的介绍可参考文章/Xilinx之Ultrascale系列时钟资源与驱动关系 - 哔哩哔哩

三、 CLB结构

3.1 LUT

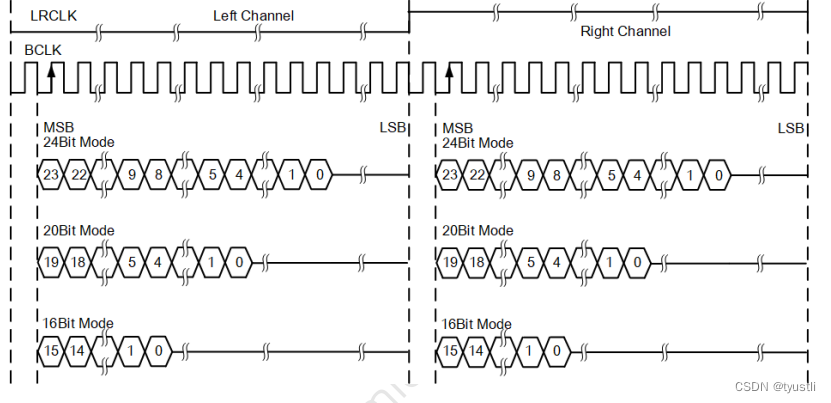

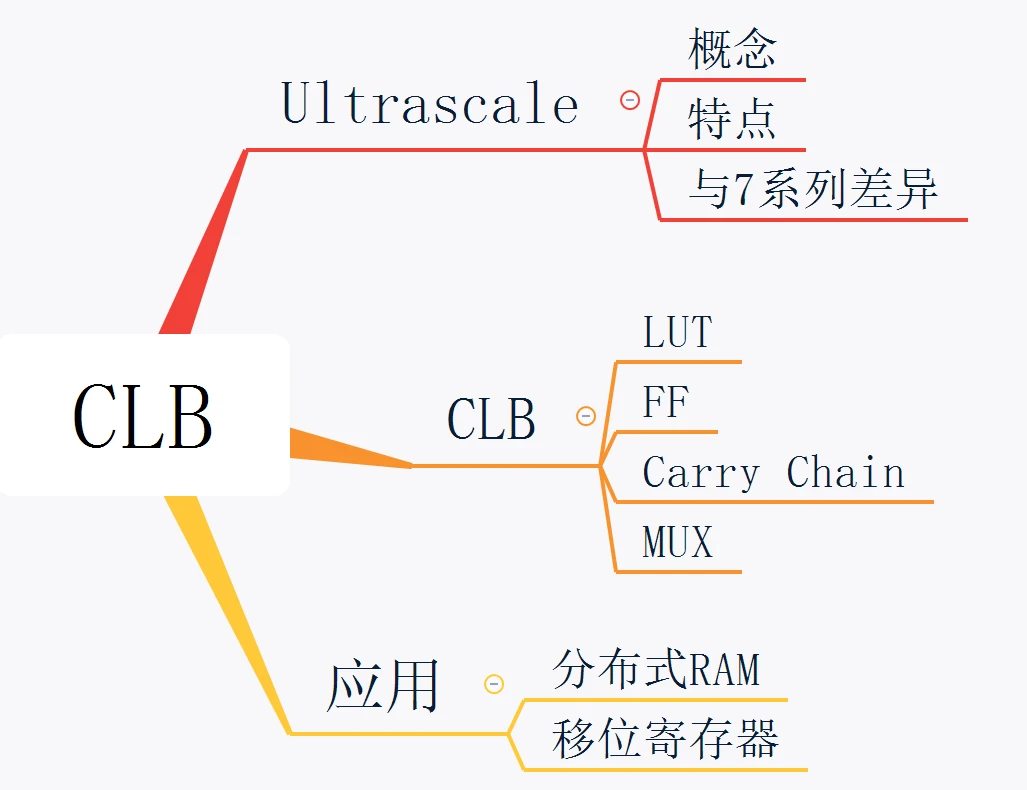

一个Slice包含8个6输入的LUT和16个FF,Slice按列分布,也可级联实现更多的功能,单个LUT6可配置成6输入单输出的LUT6,也可配置成2个五输入单输出的LUT5。

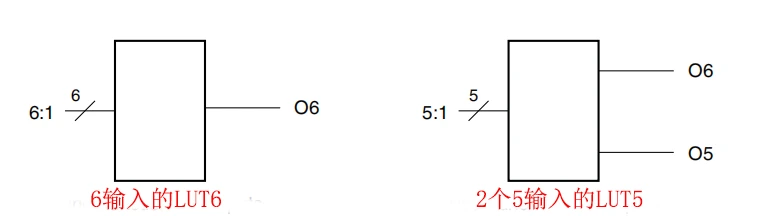

对于LUT的数据,可直接从O端口作为Slice的输出,或者经过选择器从MUX输出,也可输入到FF中再从Q1,Q2输出,Q1对应LUT的O6,Q2对应LUT的O5。

UltraScale架构包含两种类型的Slice, SliceL和SliceM。SliceM中LUT可配置为64bit的分布式RAM,多了写地址WA和写使能WE信号,时钟信号,其中,Slice中的X和I作为数据输入端口。

将单个SliceM内8个LUT组合使用可生成512bit的分布式RAM,将多个SliceM组合可生成大于512bit的分布式RAM。如果需要更大的RAM,可使用块状RAM

SliceM中的LUT也可配置为32bit的移位寄存器,将8个LUT组合使用可配置成256bit的移位寄存器。

3.2 FF

UltraScale架构的器件每个Slice包含16个FF,都可以被配置为D触发器或锁存器Latch。当被配置为锁存器时,必须以一半为单位进行配置。假设从下往上8个FF编号为A到H,如果其中一个为锁存器,其余7个也会被配置为锁存器,并且当时钟信号为高电平时,锁存器时透传的。

时钟信号:每个CLB有2个时钟输入clk1,clk2, 2个复位输入SR1,SR2用于控制FF,单个控制信号同时连接到8个FF,分为上下两部分。

使能信号:时钟使能信号有4个,CE1,CE2,CE3,CE4,每个使能信号控制4个FF,相互之间独立。

置位/复位信号 :每个CLB中的2个SR输入可被配置为与时钟信号同步或异步,可以被配置为置位set或复位reset信号,但不能同时为置位或复位信号。如果一个FF有SR信号,同一组的其余FF也是复用该信号,配置对应的原语如下。

a)不进行set/reset设置

b)同步置位原语FDSE

d)同步复位原语FDER

e)异步置位原语 FDPE

f)异步复位原语 FDCE

INIT:FF的初始化值通过INIT可设置为0或1,默认情况下,SR为set时INIT=1,为reset时INIT=0。

3.3 多路选择器Multiplexers

针对单个Slice中的LUT,可实现情况如下

a) 一个LUT配置为4:1选择器,一个CLB配置为8个4:1的选择器

b) 两个LUT配置为8:1选择器,一个CLB配置为4个8:1的选择器

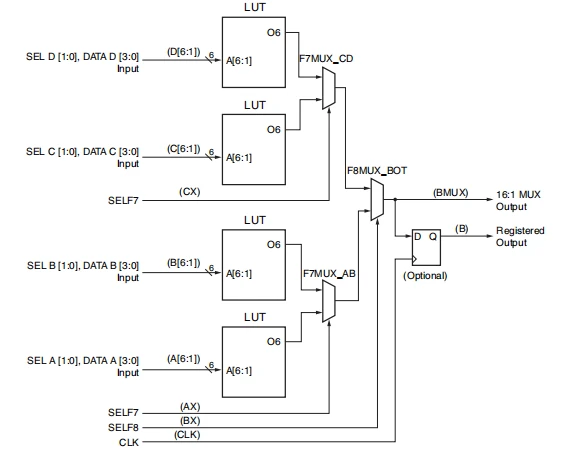

c) 四个LUT配置为16:1选择器,一个CLB配置为2个16:1的选择器

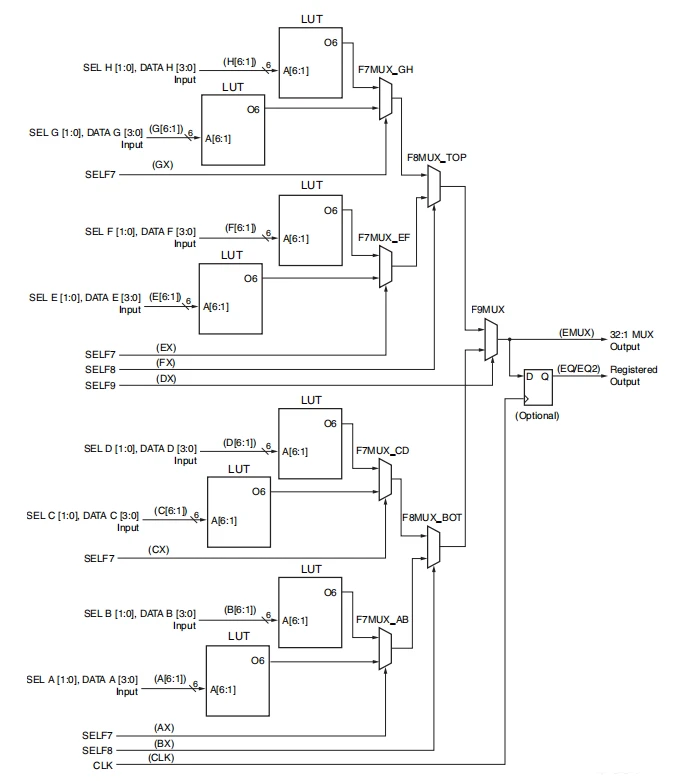

d) 8个LUT配置为32:1选择器,一个CLB配置为1个32:1的选择器

通过内部的F7MUX_AB,F7MUX_CD,F7_MUX_GH可将相邻的LUT进行扩展,两个F8MUX_BOT和F8MUX_TOP可以扩展两个F7_MUX的输出,F9MUX可扩展两个F8MUX的输出。

16:1多路选择器实现使用了4个LUT,每个LUT的6个输入中4个为数据输入DATA,2个输入为选择位SEL

32:1的多路选择器使用了Slice中所有的mux,将F7MUX,F8MUX,F9MUX的输入作为了选择位,加上LUT的中两个输入位,共5位作为选择位。

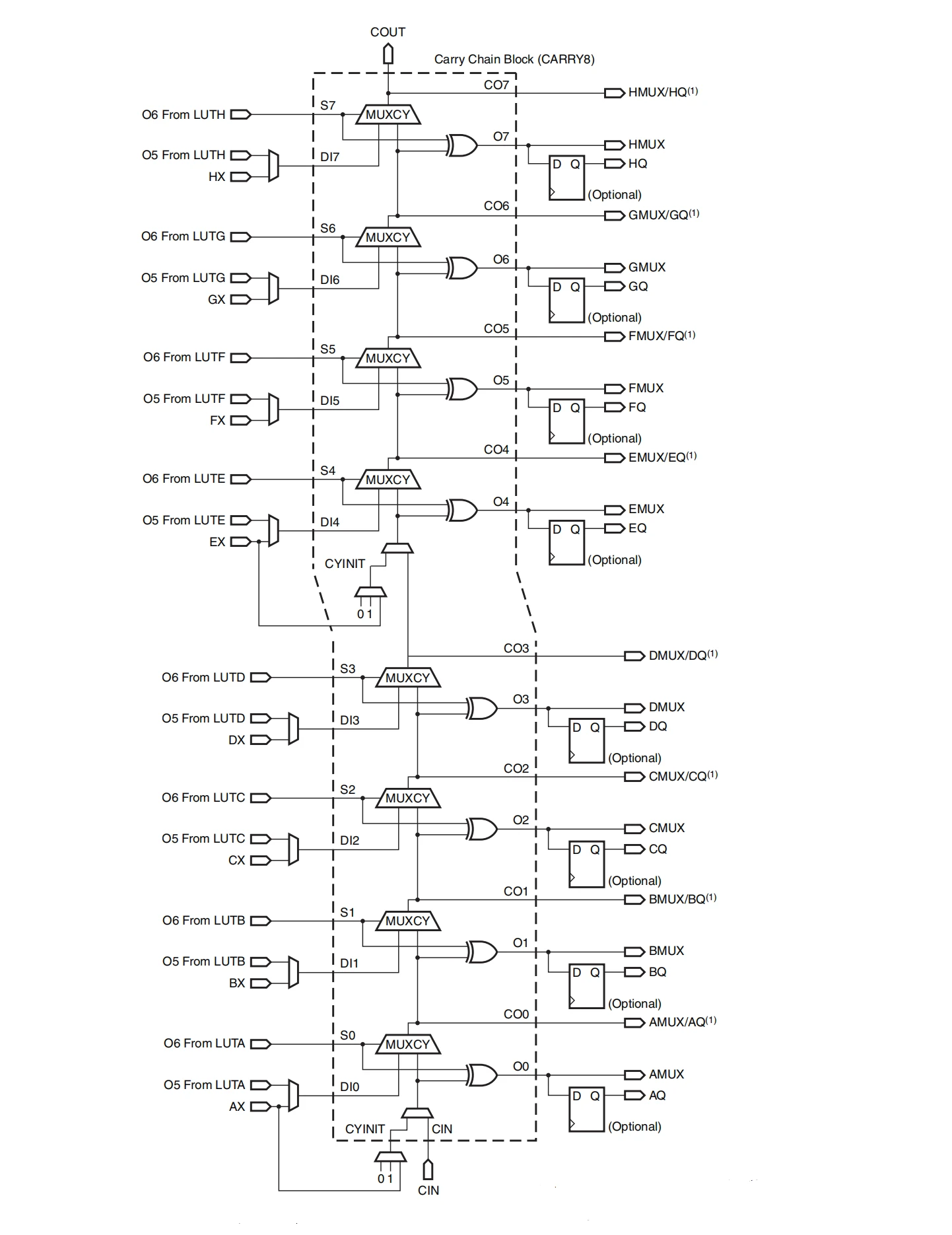

3.4 进位链Carry Chain

进位链的初始化值CYINIT用于选择进位链的第一个bit,为1表示加法,为0表示减法,AX用于动态的第一个进位输入。

四、应用

4.1 分布式RAM

分布式RAM在大容量的存储和小容量的存储间提供了一个择中的选择,通常大容量的存储使用块状RAM,小容量存储使用分布式RAM,分布式RAM可以通过例化或IP来使用。相比于块状RAM,分布式RAM从资源,性能和功耗方面更佳。

通常,对于存储的数据小于64bit时,除非没有多余的SliceM,否则都是使用分布式RAM。对于数据大于64bit小于等于128bit时,在选择分布式RAM和块状RAM的原则有以下几条

a)有块状RAM资源时优先使用块状RAM

b) 如果有异步读取时,需使用分布式RAM

c) 数据宽度大于16bit时,使用块状RAM

d)有一定的性能要求时,相比于块状RAM,寄存器的分布式RAM在时钟信号传输中时延更小,更少的布局限制。

4.2 移位寄存器

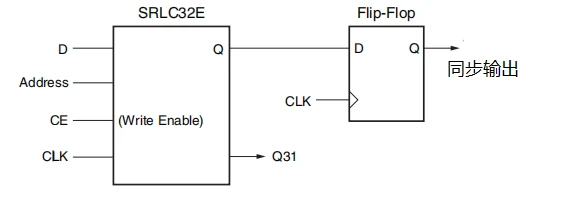

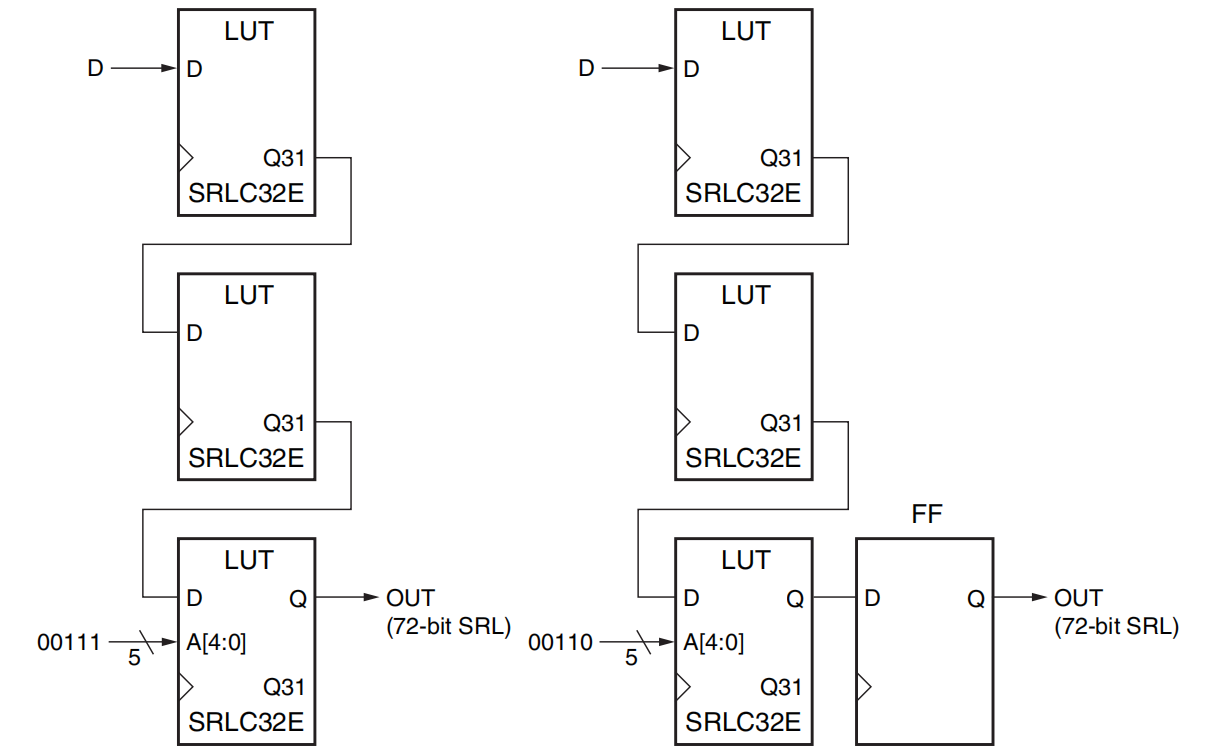

移位寄存器的原语不会使用同一个slice中的FF,如果要实现同步读写,需将输出Q连接到FF中,并且移位寄存器和FF的时钟来源是不同的。通过这种方式,将获取更好的时序,简化设计。

固定长度移位寄存器

可级联的32bit移位寄存器(使用原语SRLC32E)不需要使用多路选择器即可实现任何固定长度的移位寄存器。以72bit长度为例,级联后仅需将最后一个移位寄存器的输入固定到b00111。也可将移位寄存器的长度限定到71bit(地址截止到5'b00110),最后一个移位寄存器连接一个FF。使用SRLC32E原语时,移位寄存器的长度为地址输入+1。

4.3 进位链Carry Chain

使用进位逻辑可以改善算术运算(加法器,计数器,比较器)的性能,对于一些简单的计数器或加法器,减法器,工具会自动地综合出进位逻辑。对于复杂的计算可使用DSP实现,DSP和进位逻辑都可进行算术运算,但对于一些小计算量时,使用进位逻辑实现将更快,功耗更低。

五、参考资料

赛灵思官网手册《ug574-ultrascale-clb.pdf》

链接:https://pan.baidu.com/s/1hQA1Chjy41gQi6x8YJ8QFA

提取码:91v6