文章目录

- 1. 设计输入

- 2. 分析综合

- 3. 功能仿真

- 4. 板爷调试

- 继续熟悉基于vivado的FPGA开发流程。。

- 学习一些新语法

3-8 译码器的应用我们接下来还会用到~

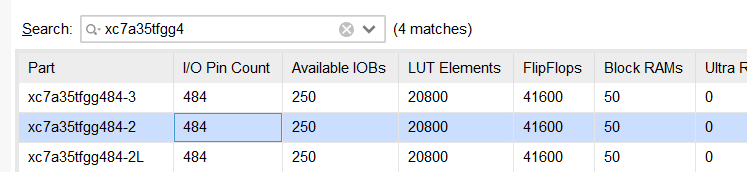

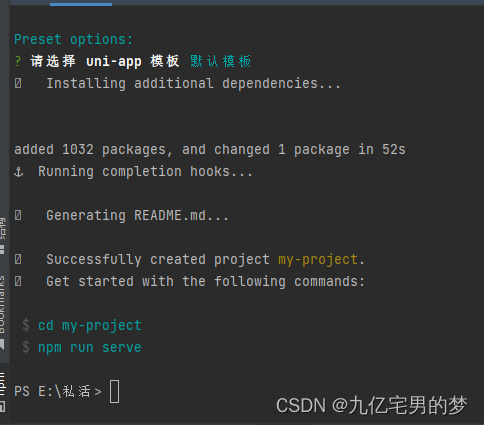

创建工程

观众老爷们别管了,咱板子也不一定一样~

1. 设计输入

- 编码

- 画框图,vivado支持较弱

- 使用IP,我们今天暂时不用哦~

添加Design Sources

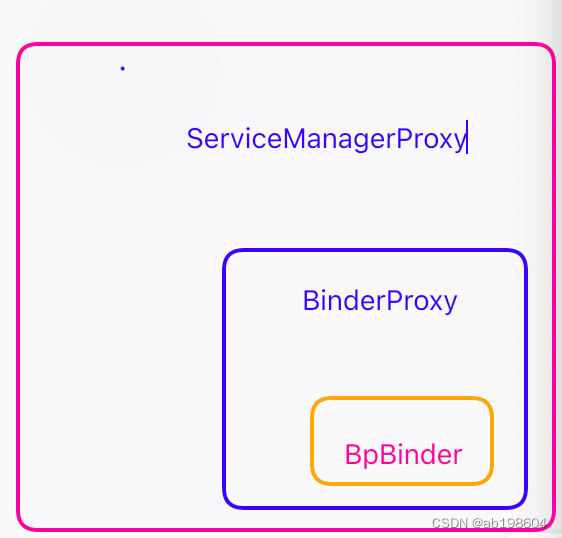

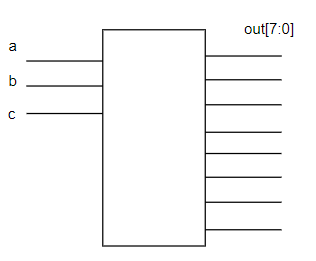

decoder_3_8

module decoder_3_8(

//端口列表

a,

b,

c,

out

);

//端口定义

input a;

input b;

input c;

output[7:0] out; //位宽描述符 - 表示多位

reg[7:0] out; //-以always块描述的信号赋值,被赋值的对象必须定义为reg类型

// output reg[7:0] out;//或者写成这样也可

//描述逻辑

always@(*) begin

case({a,b,c})

3'b000: out = 8'b0000_0001;

3'b001: out = 8'b0000_0010;

3'b010: out = 8'b0000_0100;

3'b011: out = 8'b0000_1000;

3'b100: out = 8'b0001_0000;

3'b101: out = 8'b0010_0000;

3'b110: out = 8'b0100_0000;

3'b111: out = 8'b1000_0000;

endcase

end

// always@(a,b,c)

endmodule

学习新语法,争做新青年 ——

- always块

always@(*)

always@(a,b,c)

- case - endcase块

case({a, b, c})

-

{}:位拼接,把三个独立信号看做一个三位信号我们还可 ——

wire[3:0] d; assign d = {a, 1'b0, b, c}; //设置为常量的值 -

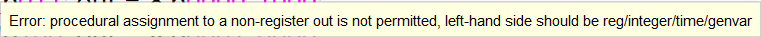

以

always块描述的信号赋值,被赋值的对象必须定义为reg类型,否则会爆红

当然也可以同时定义端口方向和端口类型。

-

8'b0000_1010:描述多位宽信号的格式限定符,当然你可以写成3'd10、8'o12、8'ha还有 ——

b二进制;d十进制;o八进制;h十六进制至于使用哪种方式,我们完全以便于理解为准。

2. 分析综合

Run synthesis 检查语法错误

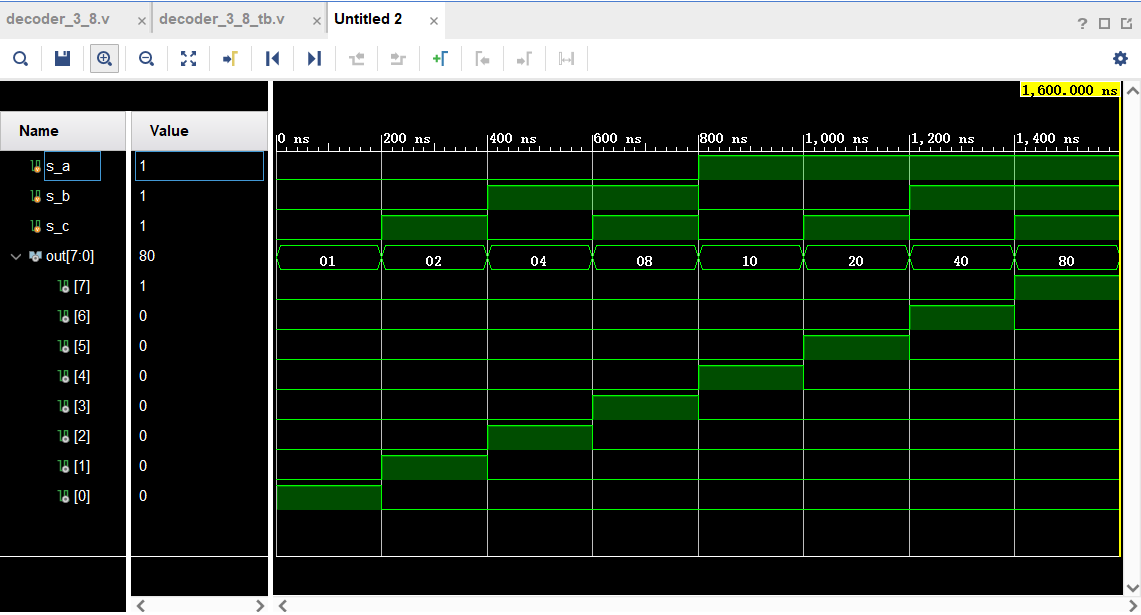

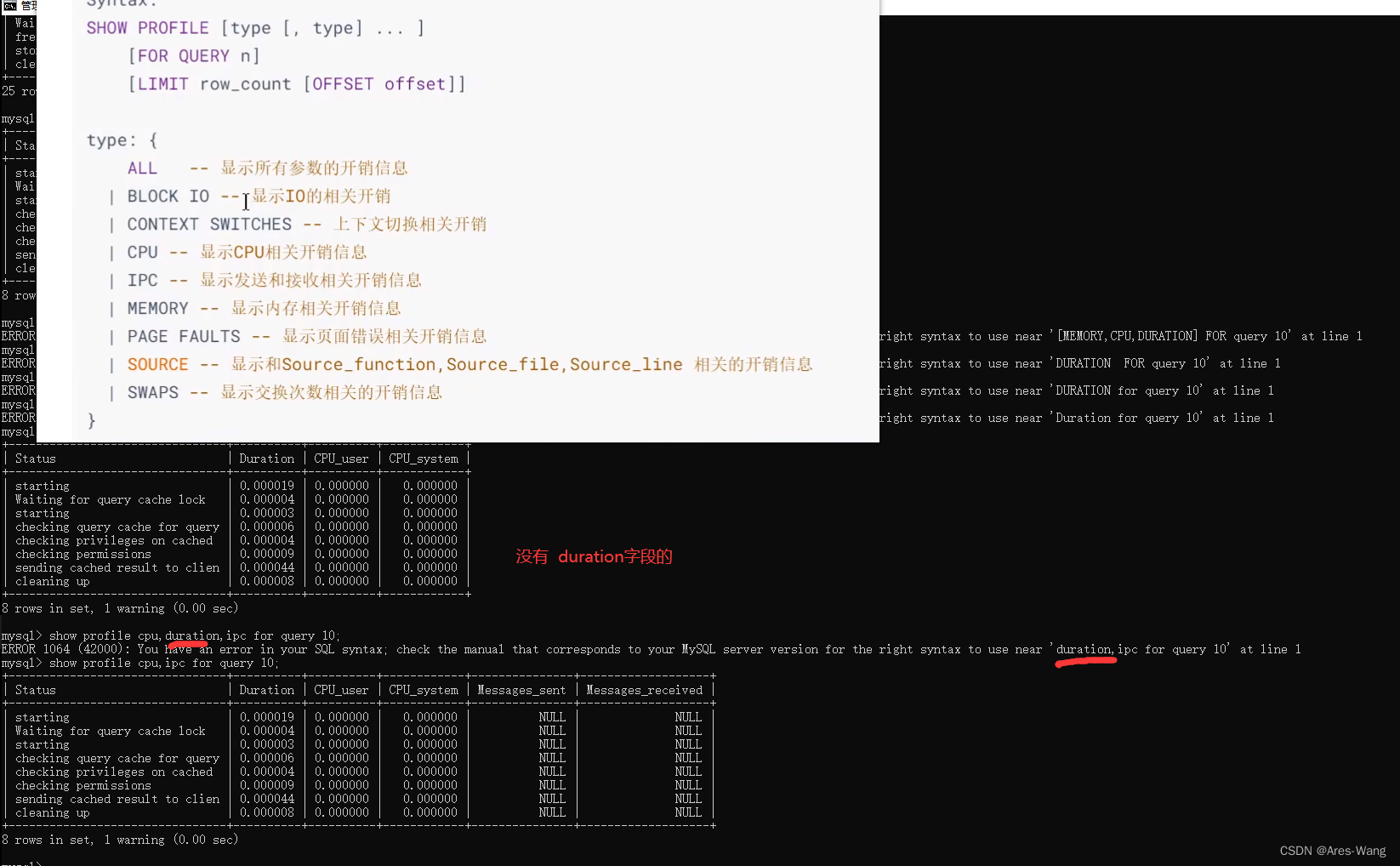

3. 功能仿真

添加Simulation Sources文件

decoder_3_8_tb

`timescale 1ns/1ns //步长/精度

module decoder_3_8_tb(); //测试模块不需要端口

//激励信号

reg s_a;

reg s_b;

reg s_c;

wire[7:0] out;

decoder_3_8 decoder_3_8( //贴标签

//连线

.a(s_a),

.b(s_b),

.c(s_c),

.out(out)

);

//产生激励

initial begin

s_a = 0; s_b = 0; s_c = 0;

#200;

s_a = 0; s_b = 0; s_c = 1;

#200;

s_a = 0; s_b = 1; s_c = 0;

#200;

s_a = 0; s_b = 1; s_c = 1;

#200;

s_a = 1; s_b = 0; s_c = 0;

#200;

s_a = 1; s_b = 0; s_c = 1;

#200;

s_a = 1; s_b = 1; s_c = 0;

#200;

s_a = 1; s_b = 1; s_c = 1;

#200;

end

endmodule

run synthesis 再分析综合哦吼吼,它给我分析过了

Run Simulation ——

时序仿真跳过因为这个太简单了

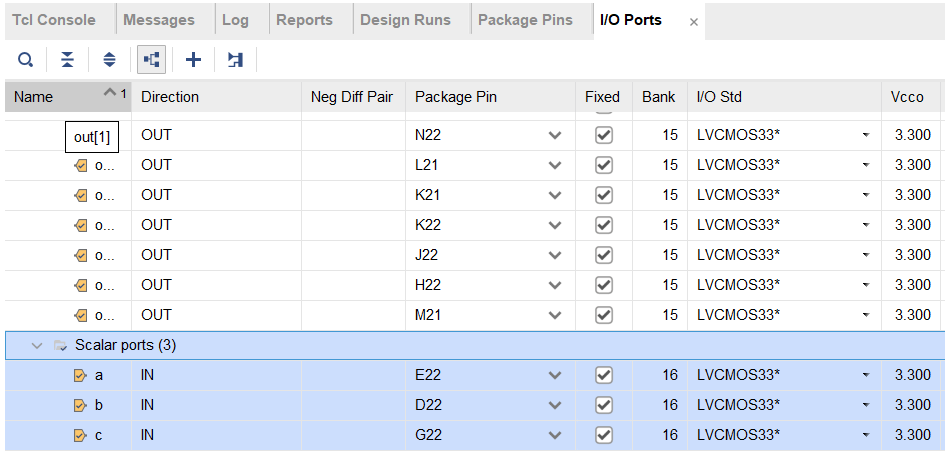

4. 板爷调试

板子就是爷,因为它太贵了。。

分配IO引脚: SYSTHESIS → open Synthesized Design → IO Planning

ctrl+s保存为XDC文件。

布局布线

IMPLEMENTATION → Run Implementation

或者你直接Generate Bitstream 那上一步自动帮你完成了,那我们以后都这么干。

连板子

Open Hardware Manager → open target → auto connect

Program device 就ok啦~

![java八股文面试[多线程]——sleep wait join yield](https://img-blog.csdnimg.cn/img_convert/7e288643040b63449dde9aa59802b8d6.webp?x-oss-process=image/format,png)