一、什么是CLB

1、CLB简介

可配置逻辑块CLB(Configurable Logic Block)是xilinx系类FPGA的基本逻辑单元(在各系列中CLB可能有所不同,以下我们主要讨论Xilinx 7系类),是实现时序逻辑电路和组合逻辑电路的主要逻辑资源。

2、CLB的组成

一般来说,EDA完成综合时会自动分配CLB资源,而不需要系统设计者的干预。对于设计者来说,理解某些CLB细节是有利的,包括查找表(LUTs)的不同功能、进位的物理方向、可用触发器的数量和分布,以及移位寄存器的可使用情况等。

每个CLB可以被划分成两个Slice,并引出逻辑连线至开关矩阵(Switch Matrix,作为布线资源),同时还包含着算术进位逻辑的功能(CIN,COUT,进位输入和输出)。如下图所示:

由于Slice有SliceL(Logic)和SliceM(Memory)之分,因此CLB可分为CLBLL和CLBLM两类。

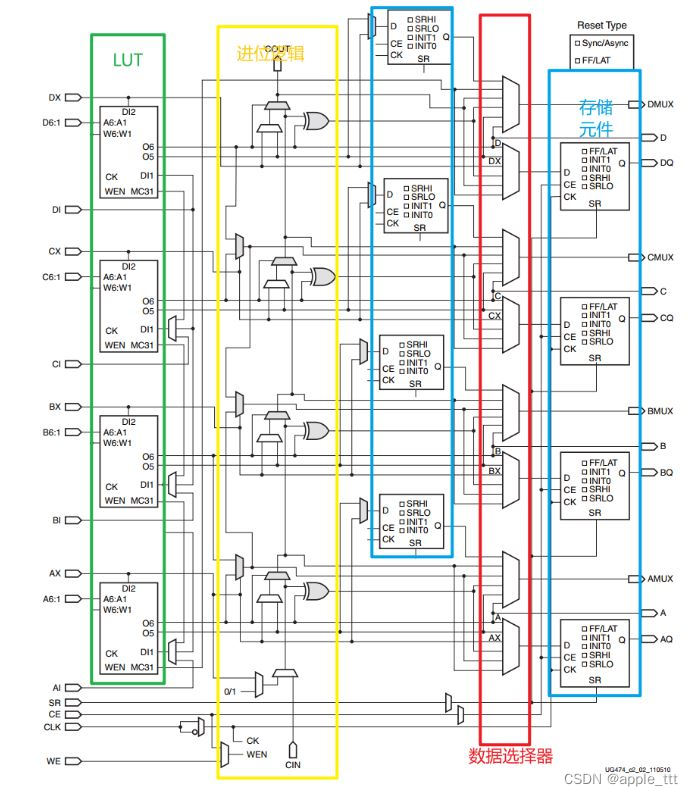

SliceL和SliceM内部都包含4个6输入查找表(LUT6)、3个数据选择器(MUX)、1个进位链(Carry Chain)和8个触发器(Flip-Flop)。

接下来我们打开vivado,选择一个7系类的device来直观的感受一下CLB的构成,以下为zynq7000系类的device视图:

我们逐渐放大途中光标坐在位置:

可以看到这就是我们的一个CLB,在xilinx 7系类中有若干个这样的CLB单元。进一步放大可以看到CLB的具体组成结构:

在这里我们可以清楚地看到,一个CLB由左右两个slice构成,每个slice中包含有4个6-input的LUT ,3个数据选择器(MUX),一个进位链(Carry Chain)和8个触发器(Flip-Flop)。

3、SLICEM与SLICEL的区别

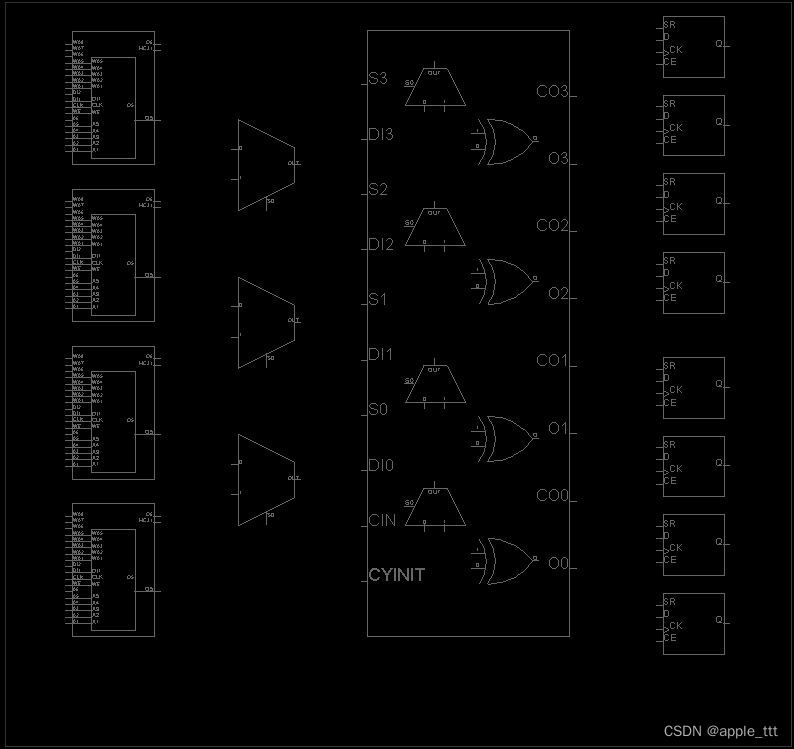

首先我们继续从device的角度直观观察两者的区别,下图为SLICEM的视图展示:

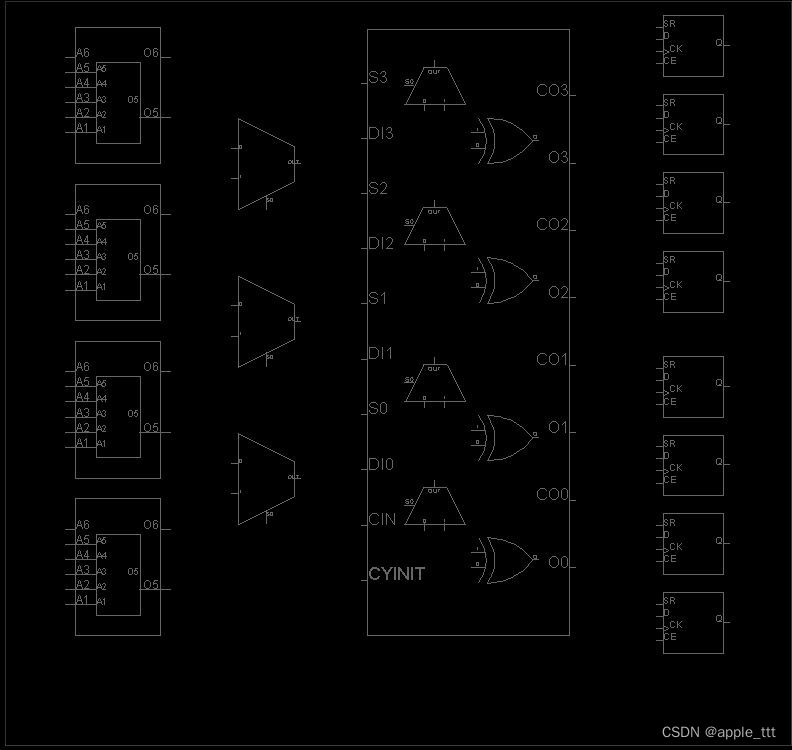

下图为SLICEL的视图展示:

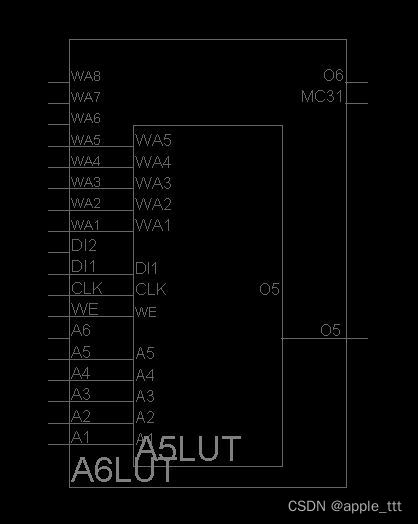

可以看到从视图上明显的区别就在于两者的LUT有所不同,我们对两者的LUT进一步放大进行观察:

左侧是SliceM对应的LUT视图,右侧为SliceL对应的LUT视图。

SLICEM(M:Memory):其内部的LUT可以读也可以写,可以实现移位寄存器和64bit的DRAM等存储功能,还可以实现基本的查找表逻辑。

SLICEL(L:Logic): 其内部的LUT只可以读,只能实现基本的查找表逻辑。

在上图中,CLB由一个SLICEM和一个SLICEL组成,在实际情况中,一个CLB也有可能是由2个SLICEL组成。但是不会由2个SLICEM组成。

大部分情况下,FPGA中SLICEL和SLICEM的数量比例为SLICEL:SLICEM = 2:1。

4、官方推荐的设计流程

我们学习硬件底层有时候最终还是为了优化我们的代码设计,基于此官方在手册中也给出了几条推荐的HDL设计:

(1)CLB中的触发器有一个置位(set)和一个复位(reset),设计者禁止同时使用这两者。

(2)硬件中有着大量的触发器,所以推荐使用流水线的方式来提高效率。

(3)控制类输入信号在一个slice或者CLB中是被共享的,所以设计中的唯一控制类输入信号的数量应该减少。控制类输入信号包括时钟信号,时钟使能信号,使能信号,置位/复位信号。

(4)6输入LUT可以被设计成32位移位寄存器来提高布线效率。

(5)6输入LUT 可以被设计成64*1的DRAM来完成小规模存储需求。

(6)专用进位逻辑有效地实现了算术函数。

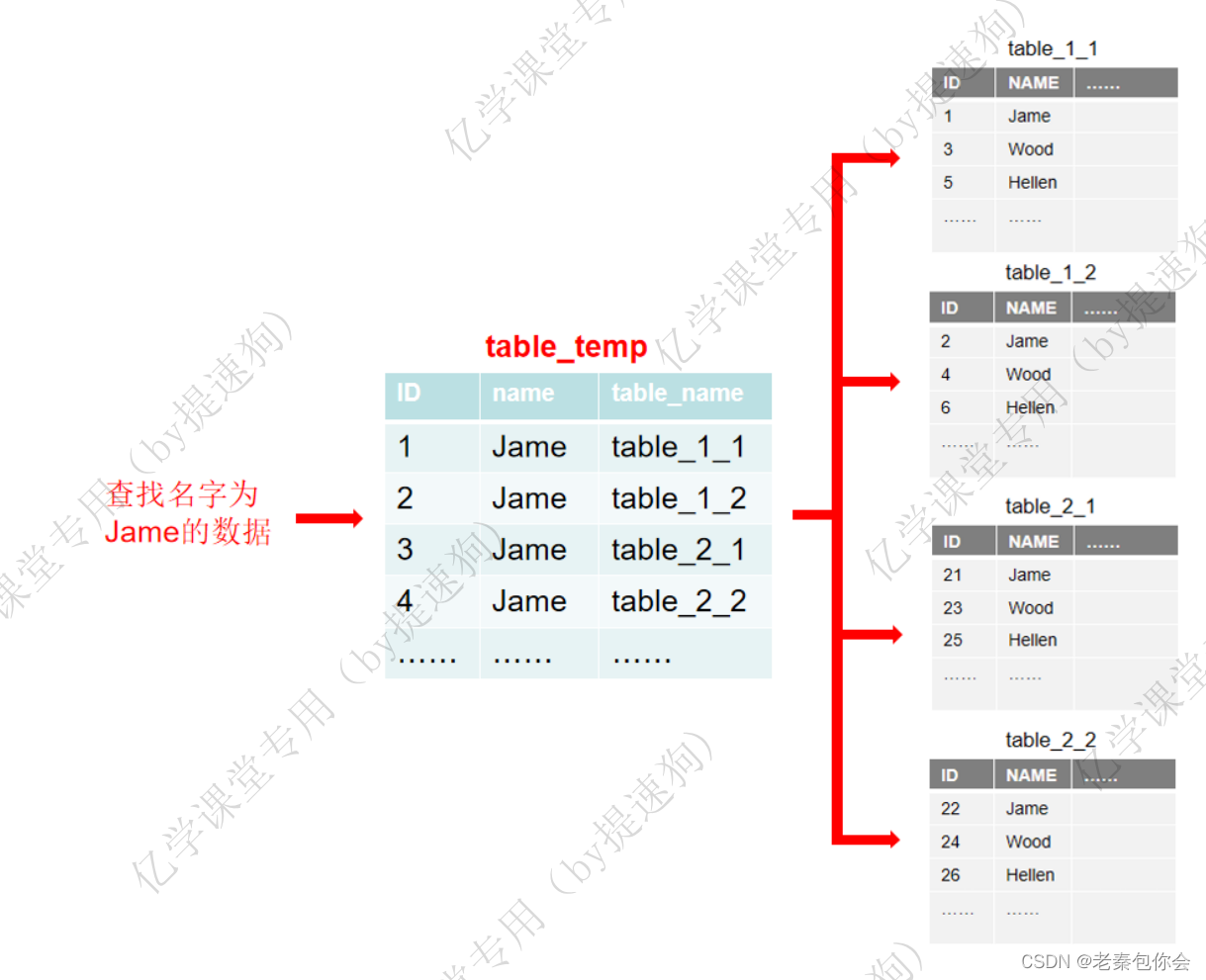

二、CLB在FPGA中的分布

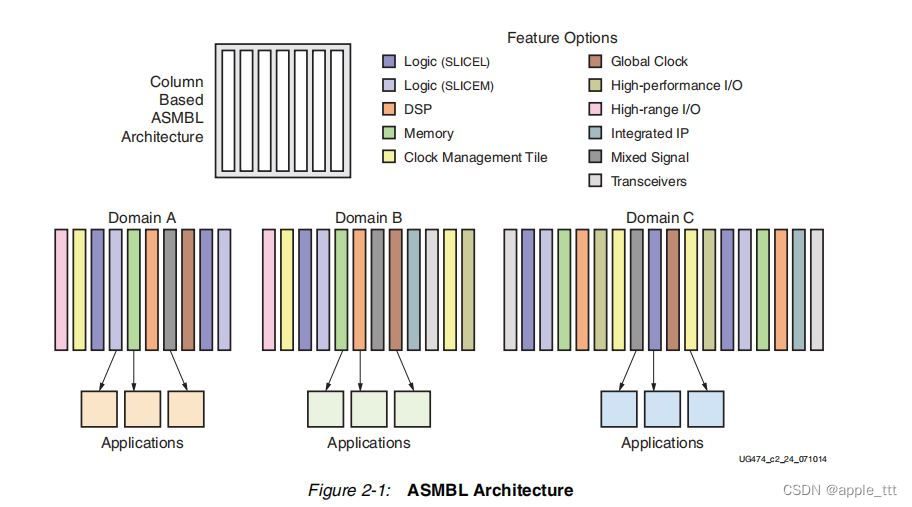

CLB在xilinx 7系类FPGA中按列分布,7系列是基于ASMBL体系结构提供的独特柱状方法的第四代。

ASMBL 架构:

Xilinx创建了高级硅模块(Advanced Silicon Modular Block,ASMBL)体系结构,使FPGA平台具有针对不同应用领域优化的不同功能组合。下图提供了基于列的不同类型的资源描述。

ASMBL通过使用独特的基于列的结构,实现了支持多专门领域应用平台的概念。每列代表一个专门功能的硅子系统,如逻辑资源,存储器,I/O,DSP处理,硬核IP和混合信号等。xilinx公司通过组合不同的功能列,组装成面向特定应用类别的专门FPGA(与专用不同,专门是指一项单一的应用)。典型的有逻辑密集型、存储密集型和处理器密集型等。例如,用与图像处理的处理器密集型芯片可能就包含有比较多的DSP功能列。

ASMBL架构具体优势不是本文的重点内容,这里不做详细的展开,简单说就是(1)解决基于应用领域的设计问题(2)解决在传统ASIC和FPGA设计中都存在的一些技术约束问题。

说了这么多,其实对于本文来说,只需要了解CLB在xilinx 7系类FPGA中根据ASMBL架构按列排布即可。

三、CLB Slices概述

1、Slice的分布排列

前文我们已经提到过一个CLB由两个Slice构成,一个Slice中有4个6输入的查找表LUT,8个触发器FF。在之前我们在vivado中通过device直接观察时感觉似乎Slice之间是一左一右对称的形式存在的,但是在实际的硬件中却有所不同(device里只是示意图):

Slice(0):CLB的左下角

Slice(1):CLB的右上角

这两个slice相互之间没有直接的连接,每个slice都在一个单独的列里(从ASMBL架构图中体现地很明显) ,并且每个slice具有独立的进位链。具体地排列可以参见下图:

2、Slice的内部结构

我们都知道了Slice根据其LUT的不同可以分为SliceM(memory)和SliceL(logic)。

(1)SliceM的结构组成:

(2)SliceL的结构组成:

具体的内部连接看不同没关系,但是在这个阶段我们应该能够分辨上图中的各个模块,包括哪些是LUT,MUX,carry chain和FF。至于关于这些模块的具体细节,我们接着往下看。

四、查找表Look-Up Table (LUT)

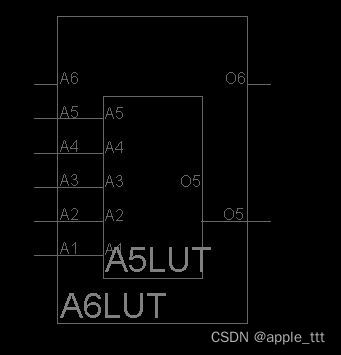

LUT是CLB的重要组成部分,其本质就是一个RAM,用来实现数字电路中逻辑门的功能,把输入映射成存储地址,再输出对应地址(输入)内存储的值作为输出来实现所需的逻辑功能。7系类的FPGA中使用6-LUT,它通过2个5-LUT组成,也可以通过其他逻辑器件实现7/8输入。

关于LUT的详细内容,请阅读:FPGA原理与结构——查找表LUT(Look_Up_Table)

我们知道slice有SLICEM和SLICEL两种,其区别就在于他们的LUT不同,SLICEM的LUT既可以读,又可以写;SLICEL的LUT只能读。由于SLICEM的LUT具有可以读写的特性,他还可以被配置成DRAM或者移位寄存器来使用。

关于DRAM的内容,请阅读:FPGA原理与结构——分布式RAM(Distributed RAM,DRAM)

关于移位寄存器的详细内容,请阅读:FPGA原理与结构——移位寄存器(Shift Registers)

五、存储单元Storage Elements

在CLB中主要有2种类型的存储单元,一种只能被配置成触发器(FF),另一种既可以被配置成触发器(FF),也可以被配置成锁存器(Latch),然后他们根据复位方式的不同,复位后输出结果的不同可以被配置成不同类型的触发器/锁存器。

关于存储单元的详细内容,请阅读:FPGA原理与结构——存储单元(Storage Elements)

六、数据选择器MUX(Multiplexers)

数据选择器是一个多输入,单输出的组合逻辑器件,在每个slice中有一个F7BMUX和一个F7AMUX,这两个MUX将两个lut的输出组合起来,形成一个多达13个输入(或一个8:1的MUX)的组合函数。在一个slice中最多最多可以部署两个MUX8。每个slice还就有一个F8MUX,它可以把F7AMUX和F7BMUX的输出作为自己的输入,形成一个多达27个输入(或一个16:1的MUX)的组合函数。一个slice中最多只能部署一个MUX16。

关于MUX的详细内容,请阅读:FPGA原理与结构——数据选择器MUX(Multiplexers)

七、进位链(CARRY4)

进位逻辑在FPGA中有着非常广泛的应用,其功能主要是实现二进制的加减法运算。在7系列的FPGA中,一个CLB中有两个Slice,一个Slice中包含4个LUT6、3个数据选择器MUX、1个独立进位链(Carry4,Ultrascale是Carry8)和8个触发器。这里我们谈论Carry4。在CLB中,除了函数发生器之外,还提供了专用的快速超前进位逻辑,以slice中执行快速算术加法和减法, 进位链还可级联以形成更宽的加/减逻辑。

关于进位链的详细内容,请阅读:FPGA原理与结构——进位链CARRY