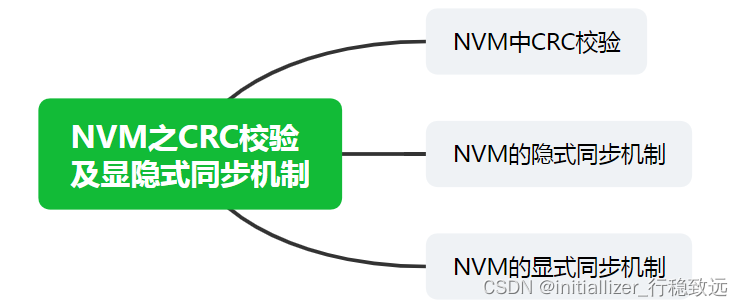

本文框架

- 0.前言

- 1. NVM中CRC校验

- 2. NVM的显隐式同步机制

- 2.1 隐式同步

- 2.2 显式同步

0.前言

本系列是Autosar存储入门系列,希望能从学习者的角度把存储相关的知识点梳理一遍,这个过程中如果大家觉得有讲得不对或者不够清晰的地方,还请一定指出来,一起探讨,加深学习。

另外根据本人多年的开发经验,做了一些AutosarMCAL配置,通信,诊断,模式管理等实战总结,如果您有需求可以参见AutoSar 实战进阶系列专栏,快速链接:AutoSar实战进阶系列导读

本篇介绍一下Autosar中NVM存储的CRC校验及同步机制,基本框架如下:

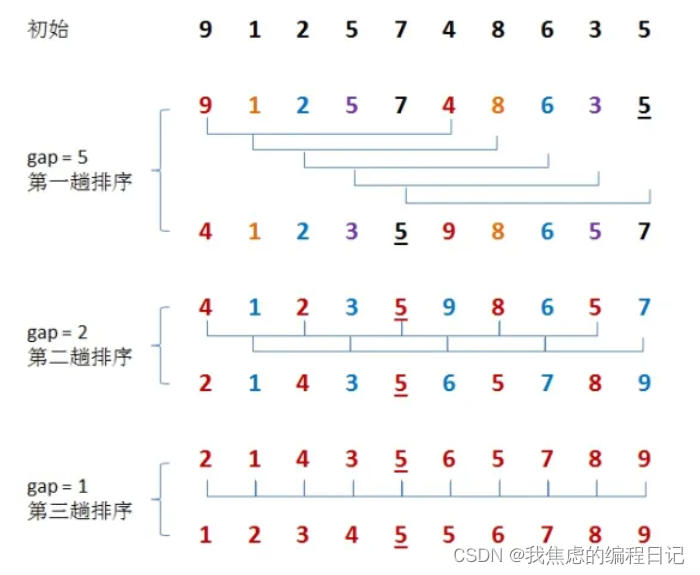

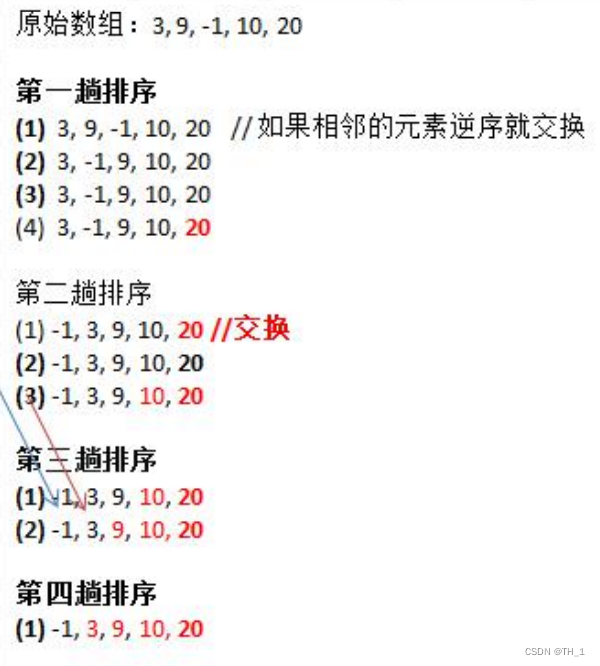

1. NVM中CRC校验

对于NVM中各Blcok存储的基本内容分为三部分:Block Header + Block Data + CRC Data,其中Block Header(Block ID,size等信息)及CRC校验信息为可配置内容。

在NVM读写时会对CRC进行校验:

在读取时如CRC校验不过,会采用默认值,如无特殊默认值将默认为0;

如在写入时CRC校验一致即认为需要存入NVM的数据没有发生改变,则跳过写操作请求,CRC校验不一致则将数据及CRC一起写入DFLASH中,该CRC值将参与下一轮比较。

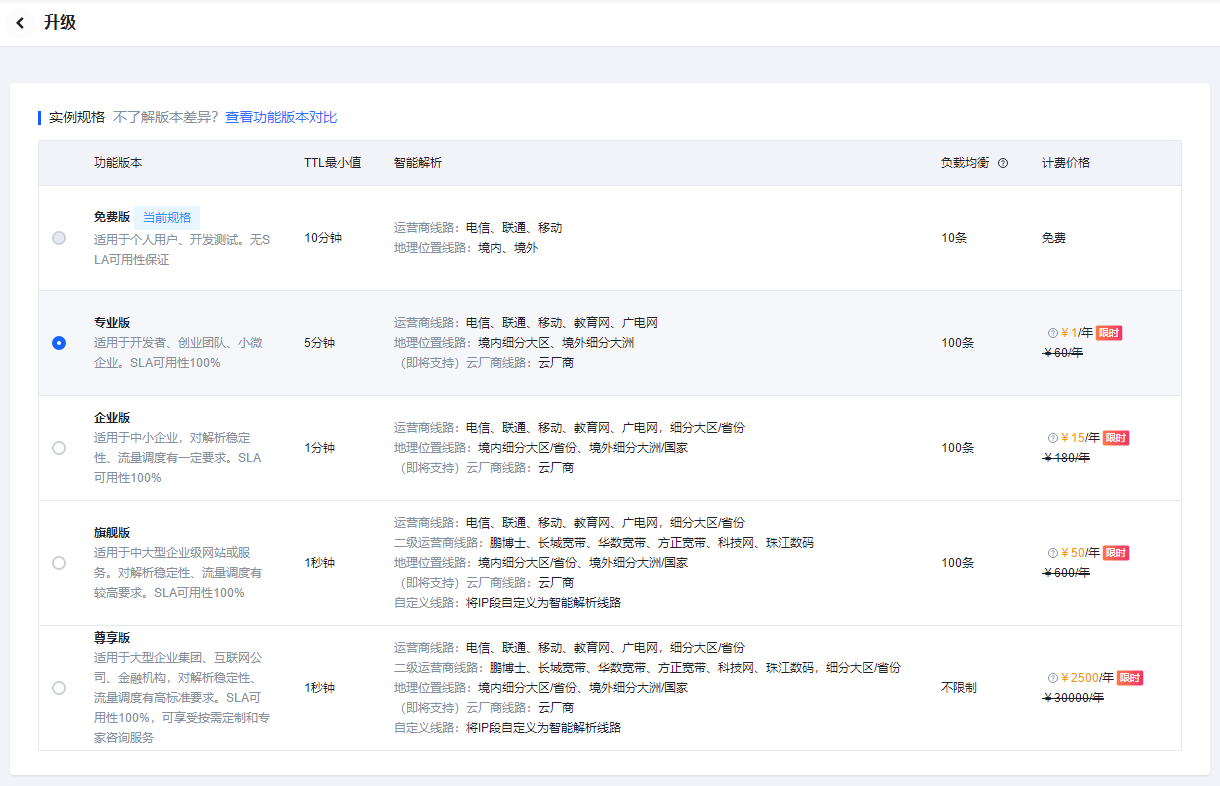

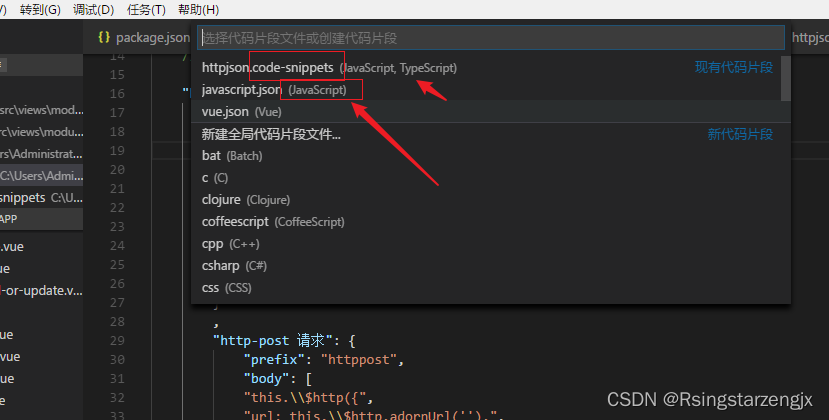

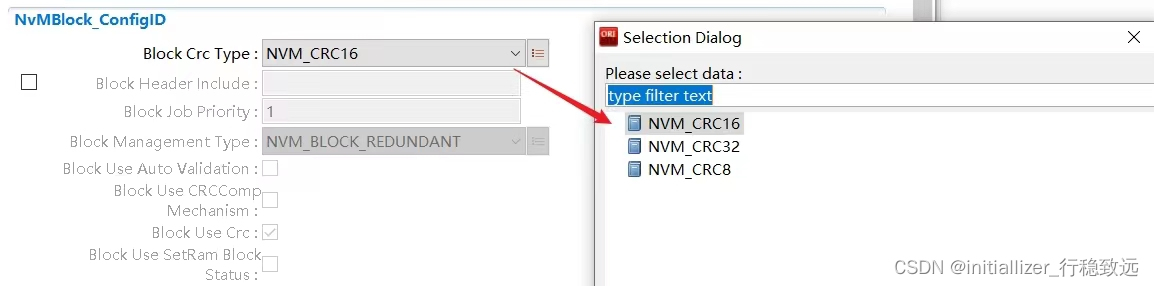

在NVM模块配置时,如选择CRC校验,则还需要选择校验的类型:

2. NVM的显隐式同步机制

在访问NvM Blcok对应的RAM数据时,根据访问方式的不同可支持两种类型的同步机制:

隐式同步(Implicit synchronization)

显示同步(Explicit synchronization)

2.1 隐式同步

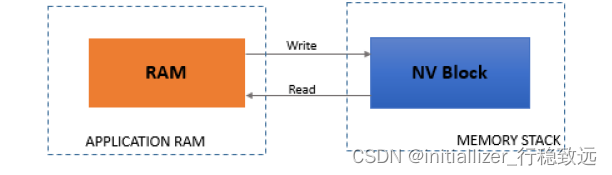

在隐式同步中,Application和NvM可以同时访问公共RAM块。应用程序通过调用NvM API将数据写入RAM或从RAM读取数据。

在这种情况下,一个NvM Block的 RAM 块被映射到一个SW-C,不推荐共享RAM。此外,为了保证数据的一致性,当SWC调用NVRAM接口进行读写操作时,SWC不能改变RAM中的值,直到NvM完成正在进行的操作,在此期间,应用程序可以使用轮询来获取请求NVM的状态,也可以通过回调函数异步通知。

适用场景:适用于下电写的Block,即在程序RUN的过程中不存,下电前将RAM中最后的值存进去。

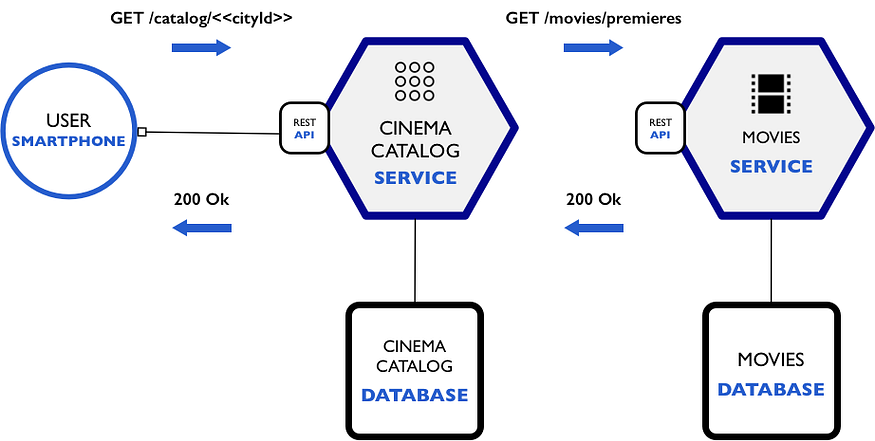

2.2 显式同步

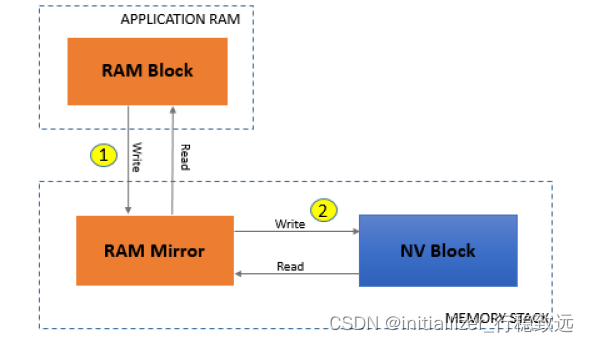

在显示同步中,NVM会再定义一个RAM Mirror与应用层进行数据交换,App在调用NVM实时写接口时将应用层RAM数据写到RAM Mirror中,应用层可以随意更改应用层RAM,仅需要在发起写入请求时,将应用层RAM拷贝到RAM Mirror中即可修改应用层RAM而无需等待NVM读写完成。

与隐式同步相比,在显式同步中,应用层RAM可以由多SWC共享,缺点同样由于增加了RAM Mirror会增加Ram资源的消耗量。

适用场景:适用于实时存储的Block,应用层可以更新RAM Block中的值,等上一轮写完再调用NVM接口进行写入。