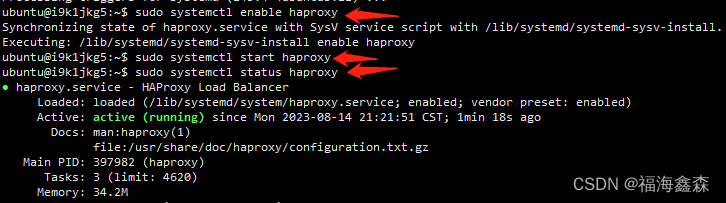

verilog 典型电路设计之加法器树乘法器

加法器树乘法器

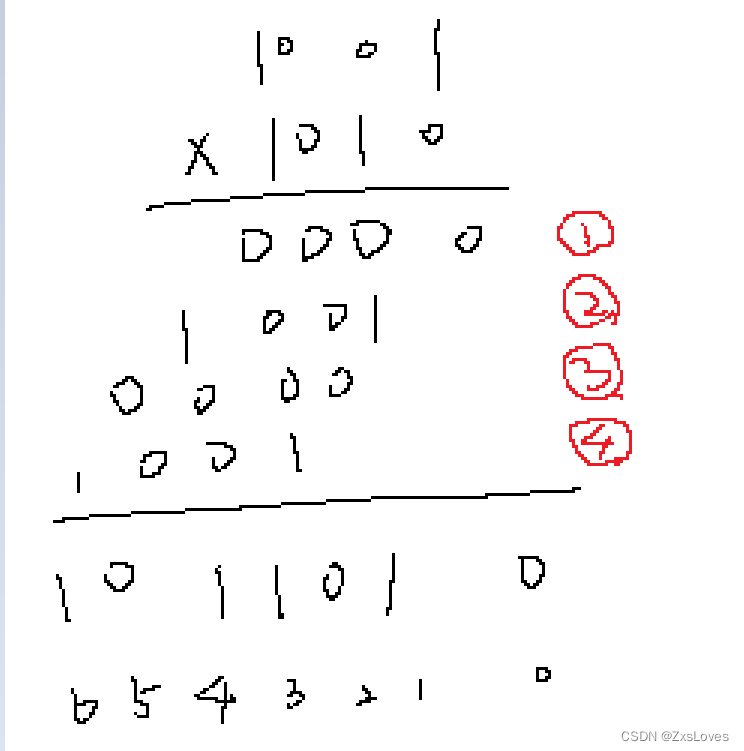

加法器树乘法器的设计思想是“移位后加”,并且加法运算采用加法器树的形式。乘法运算的过程是,被乘数与乘数的每一位相乘并且乘以相应的权值,最后将所得的结果相加,便得到了最终的乘法结果。

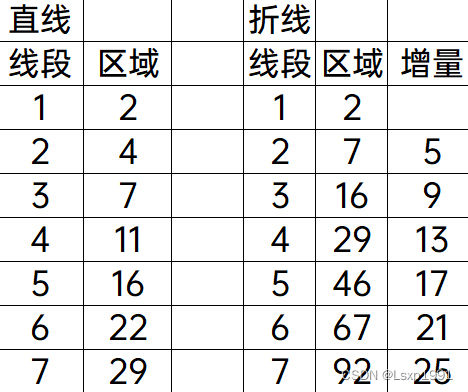

首先我们明确一个观点 进行4位数乘法应该来说是最多会得到 8 位

因为4位数最大是15 15乘15得到的是225 在可控制的 128 到 256 之间 所以我们基本确定 临时变量选取为【7:0】 即可

然后下一步我们通过实际例子来确定乘法器简单的逻辑

比如 两个数 1001 乘 1010

我们观察可知得到【6:0】 完全可以用[7:0]去覆盖 还有 得到的四位暂存下来就是0 乘1001 1乘1001 0 乘1001 1乘1001

每一个进行小移位之后相加 即可

四位暂存数,就好比 第一位确定的是[3:0] 第二位确定的是[4:1] 第三位是[5:2] 第四位是[6:3] 在面对是[7:0]中 我们可以采取在其他位补0 的做法 保证它的适用性

以下是verilog的代码

module mul_addtree(mul_a,mul b,mul_out);

input[3:0] mul_a,mul_b;

wire[7:0] mul_out;

wire[7:0] stored0,stored1,stored2,stored3;

wire[7:0] add01, add23;

assign

stored3=mul_b[3]?{1'b0,mul_a,3'b0}:8'b0;

assign

stored2=mul_b[2]?{2'b0,mul_a,2'b0}:8'bo;

assign

stored1=mul_b[1]?{3'b0,mul_a,1'b0}:8'b0;

assign

stored0=mul_b[0]?{4'b0,mul_a}:8'b0;

assign add01=stored1+stored0;

assign add23=stored3+stored2;

assign mul_out=add01+add23;

endmodule

接下来

写下testbench

module mult_addtree_tb;

reg [3:0]mult_a;

reg [3:0]mult_b;

wire [7:0]mult_out;

mul_addtreeU1(.mul_a(mult_a),.mul_b(mult_b),.mul_out(mult_out));

initial

begin

mult_a=0;

mult_b=0;

repeat(9)

begin

#20

mult_a=mult_a+1;

mult_b=mult_b+1;

end

end