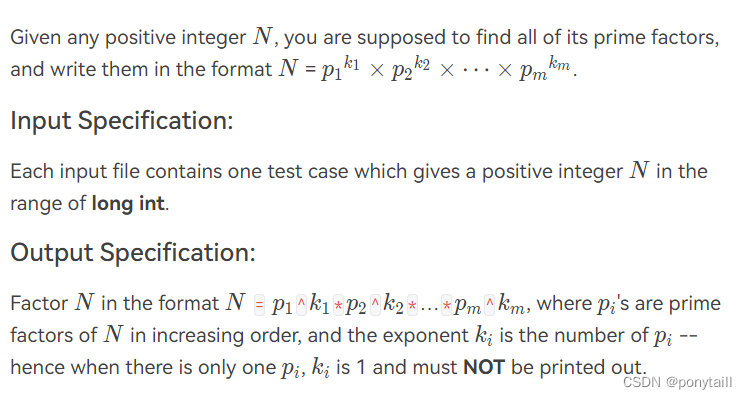

对于初学者,一般会遇到这种情况,明明写的时序逻辑,结果仿真结果却是组合逻辑,然后看遍设计代码,始终找不到原因,交流群、知乎这种问题随处可见。但不要怀疑软件问题,modelsim这些专用软件基本不会遇见软件自身问题,原因其实很简单,因为多数人只关注设计文件不会关注TestBentch的合理性,导致找不到问题原因,后文分析原因并给出避免这种问题的方法。

在仿真时经常会使用“#”和“@(posedge clk)”来实现延迟,“#”后面跟数字,表示延迟数字对应最小的时间单位,而“@(posedge clk)”则用来检测clk信号上升沿,如果CYCLE表示始终周期对应的时间长度,那么“#(CYCLE)”表示延迟一个时钟周期长度的时间。在时钟上升沿输出数据后,使用“@(posedge clk)”,会延迟到下个时钟上升沿,同样也可以表示延迟一个时钟周期,那有没有区别?

分析以下代码,输出dout就是两个输入dataa与datab相加,由于是时序逻辑,dout会延迟dataa或datab变化后的一个时钟周期。

module add(

input clk ,//系统时钟;

input rst_n ,//系统复位,低电平有效;

input [3 : 0] data_a ,//加数dataa;

input [3 : 0] data_b ,//加数datab;

output reg [4 : 0] dout

);

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin//初始值为0;

dout <= 4'd0;

end

else begin

dout <= data_a + data_b;

end

end

endmodule

Testbench如下所示:

`timescale 1 ns/1 ns

module test();

parameter CYCLE = 10 ;//系统时钟周期,单位ns,默认10ns;

parameter RST_TIME = 5 ;//系统复位持续时间;

parameter STOP_TIME = 100 ;//仿真运行时间,复位完成后运行100个系统时钟后停止;

reg clk ;//系统时钟,默认100MHz;

reg rst_n ;//系统复位,默认低电平有效;

reg [3 : 0] data_a;

reg [3 : 0] data_b;

wire [4 : 0] dout ;

add u_add (

.clk ( clk ),

.rst_n ( rst_n ),

.data_a ( data_a ),

.data_b ( data_b ),

.dout ( dout )

);

//生成周期为CYCLE数值的系统时钟;

initial begin

clk = 1;

forever #(CYCLE/2) clk=~clk;

end

//生成复位信号;

initial begin

rst_n = 1;

#2;

rst_n = 0;//开始时复位10个时钟;

#(RST_TIME*CYCLE);

rst_n = 1;

end

//生成输入信号din;

initial begin

data_a = 0;data_b=0;//输入数据初始化为0;

#(10*CYCLE);//延迟10个时钟周期;

repeat(STOP_TIME)begin//循环STOP_TIME次;

#(CYCLE);

data_a = {$random} % 16;

data_b = {$random} % 16;

end

$stop;//停止仿真;

end

endmodule

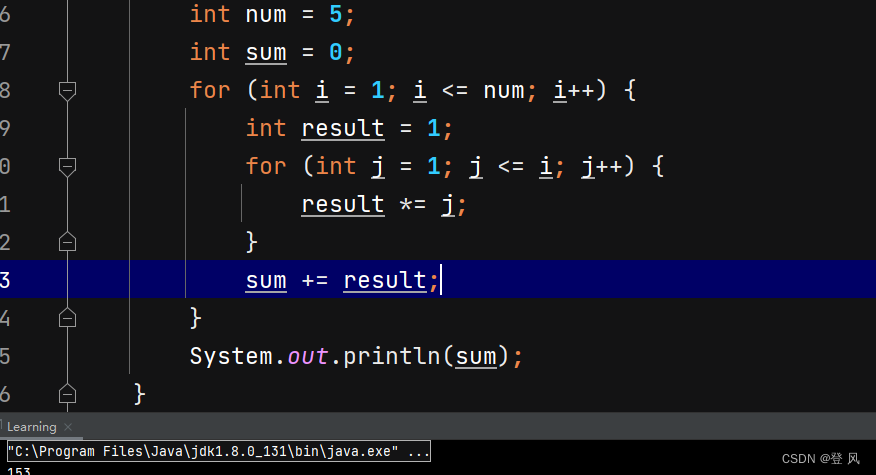

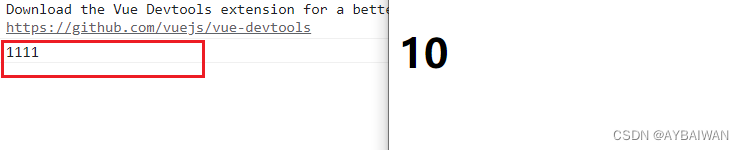

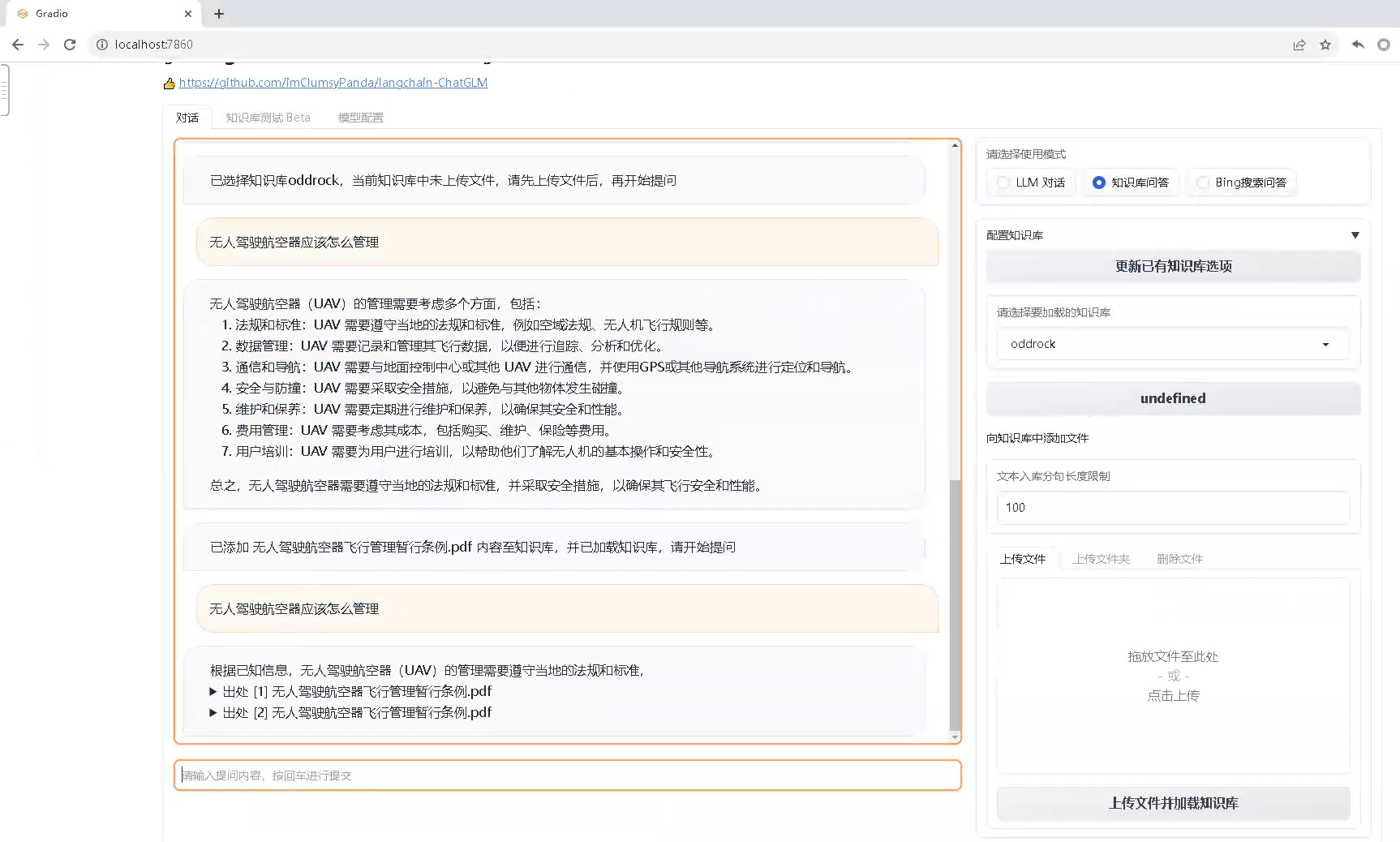

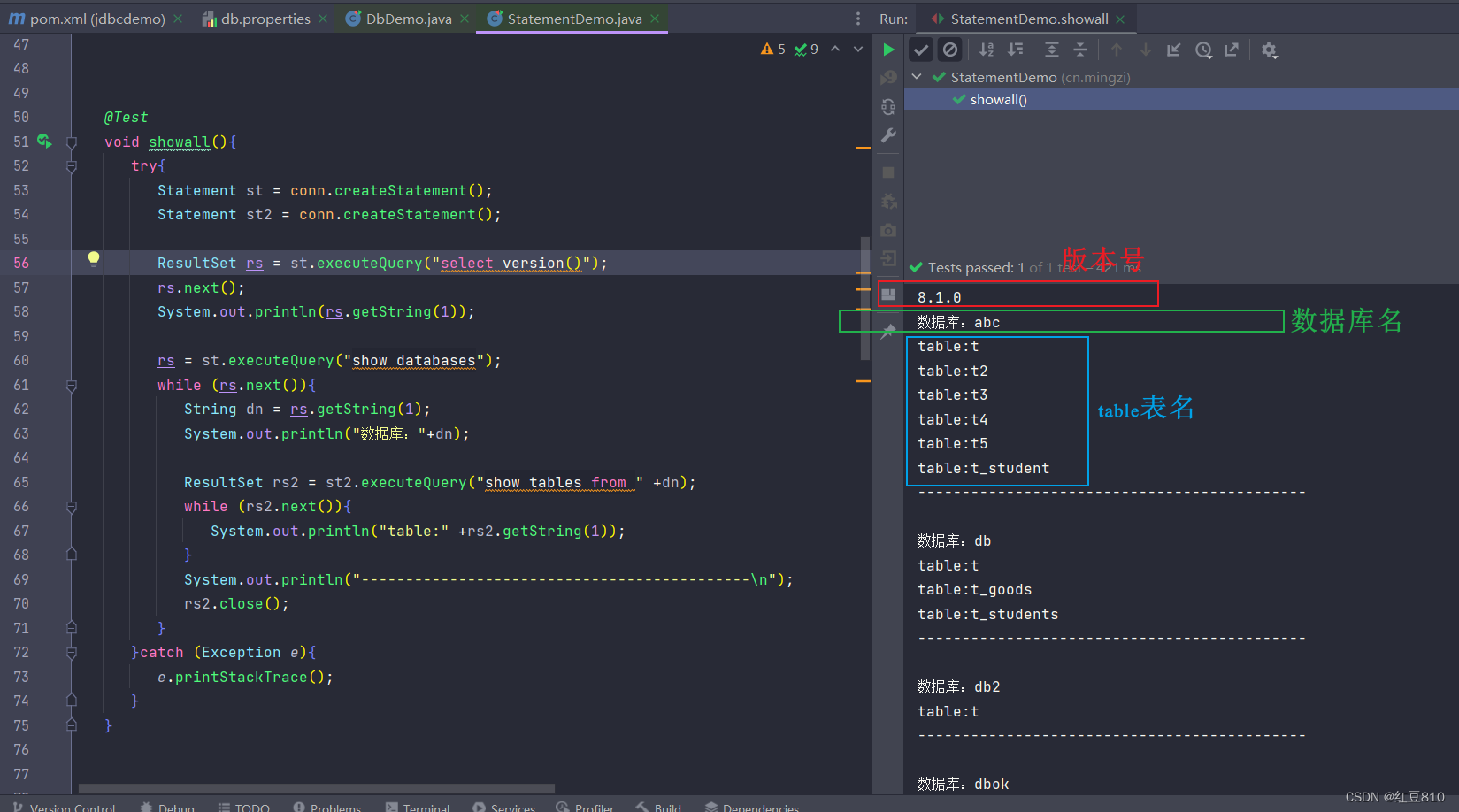

使用modelsim仿真如下图所示,奇怪的是为什么时序逻辑仿真成组合逻辑了?

分析:加法器代码肯定是没有问题的,modelsim软件也是经过fpga设计以及IC设计人员多年使用,是最常用的仿真工具,也不可能出现这样的低级bug。如果你把代码下载到开发板上,使用在线逻辑分析仪抓取数据,能够得到正确的运行结果,但是仿真就是错误的。这是为什么?那就只剩下写的testbench文件了,来看下testbench与输出相关的信号,首先时钟和复位信号是没有问题的,那就只剩下dataa与datab的产生模块了,如下所示:

//生成输入信号din;

initial begin

data_a = 0;data_b=0;//输入数据初始化为0;

#(10*CYCLE);//延迟10个时钟周期;

repeat(STOP_TIME)begin//循环STOP_TIME次;

#(CYCLE);

data_a = {$random} % 16;

data_b = {$random} % 16;

end

$stop;//停止仿真;

end

开始仿真时两个输入信号都被赋值为0,经10个时钟延迟之后进入forever循环内,每次循环之前都会把数据延迟一个时钟周期,然后在对两个输入信号赋一个0~15的随机值。逻辑上其实没有问题,但是注意一个问题,每次给dataa和datab赋值时间与时钟clk上升沿是对齐的,导致D触发器的输入信号在时钟上升沿时发生变化,由此导致D触发器数据采集错误,最终导致D触发器输出信号dout提前更新数据。这里实际上与保持时间违例有点类似,D触发器的下一个输入数据来得过快,影响了上一个数据的采集。

解决方法很简单,因为是数据刚好在时钟上升沿时发生更新导致D触发器数据采集错误,那么把两个输入数据全部延迟一点不就行了,修改如下,将两个输入数据的所有变化均延迟1ns,与时钟上升沿错开。

//生成输入信号din;

initial begin

#1;

data_a = 0;data_b=0;//输入数据初始化为0;

#(10*CYCLE);//延迟10个时钟周期;

repeat(STOP_TIME)begin//循环STOP_TIME次;

#(CYCLE);

data_a = {$random} % 16;

data_b = {$random} % 16;

end

$stop;//停止仿真;

end

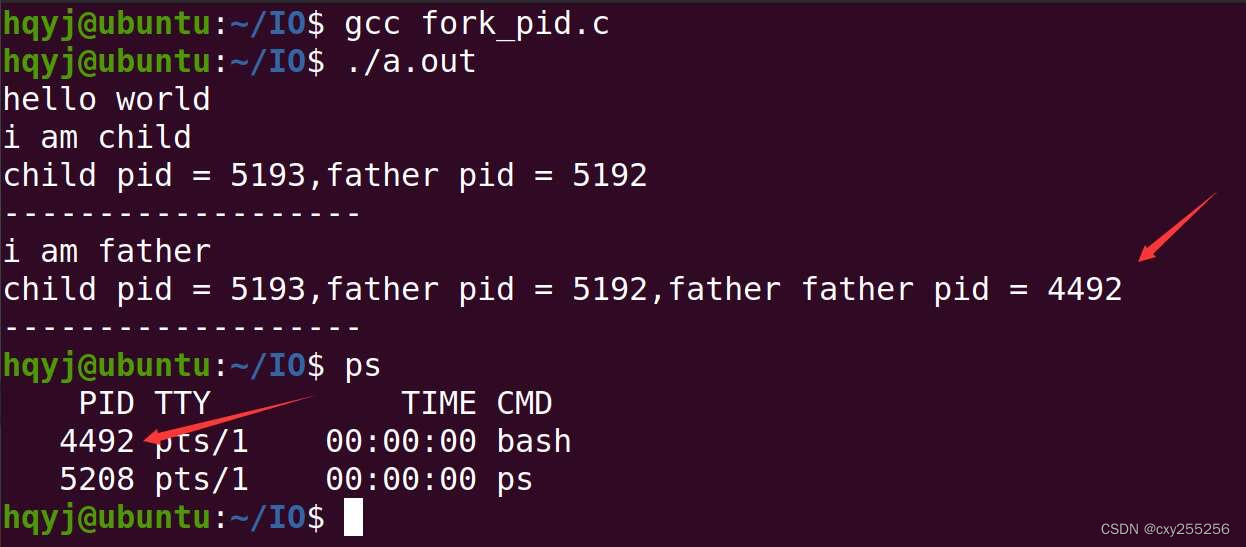

修改后仿真结果如下:

从上面仿真结果就可以看到,dataa与datab的变化都延迟时钟上升沿1ns之后,就没有在影响仿真结果了。这也是为什么很多代码在对信号赋值之前会延迟1ns的原因,就是为了数据变化与时钟上升沿错开,避免发生上面这种由于testbench书写问题所引发的离奇结果。

使用“#”会引发上面问题,那如果过使用“@(posedge clk)”这种写法还会出现那样的仿真结果?

先给答案,不会出现类似问题,因为“@(posedge clk)”表示已经检测到时钟上升沿了,那么在这之后更新的数据自然与时钟上升沿就是错开的了。

同样的案例,只是把dataa和datab赋值的部分改成如下代码。

//生成输入信号din;

initial begin

data_a = 0;data_b=0;//输入数据初始化为0;

#(10*CYCLE);//延迟10个时钟周期;

repeat(STOP_TIME) @(posedge clk)begin//循环STOP_TIME次;

data_a = {$random} % 16;

data_b = {$random} % 16;

end

$stop;//停止仿真;

end

上面代码表达结果与下面代码一致。

//生成输入信号din;

initial begin

data_a = 0;data_b=0;//输入数据初始化为0;

#(10*CYCLE);//延迟10个时钟周期;

repeat(STOP_TIME)begin//循环STOP_TIME次;

@(posedge clk);

data_a = {$random} % 16;

data_b = {$random} % 16;

end

$stop;//停止仿真;

end

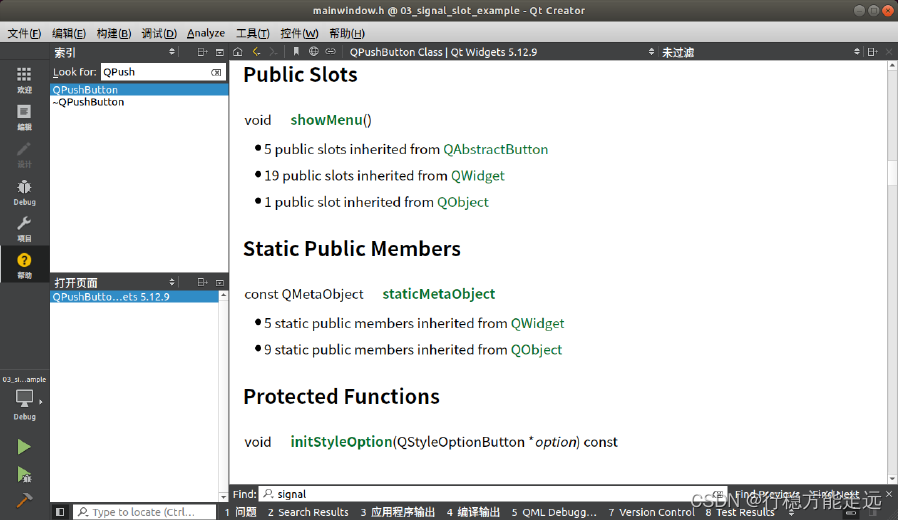

仿真结果如下,没有出现任何问题,数据变化近似与时钟上升沿对齐,但是输出数据dout没有受到影响,这就是“@(posedge clk)”的效果。

“#”和“@(posedge clk)”虽然都可以写成延时几个时钟周期的形式,但是他们是有区别的,区别在与“#”延迟与时钟其实没有关系,就有可能和时钟上升沿重合,这是使用是需要注意的,建议在仿真开始时就对数据延迟1ns然后在赋值,与时钟信号变化错位。而“@(posedge clk)”本质是检测时钟上升沿,在时钟上升沿之后才会去执行后面的语句,所以数据变化与时钟上升沿变化是错位的,不会出现“#”那种问题。

上述从效果看肯定是使用“@(posedge clk)”,作为延迟更好,使用“#(CYCLE)”延迟一个时钟更号理解,但是要注意可能遇到的问题,一般使用模板时,赋值语句开头会带有“#1;”,或者在每次赋值前用“@(posedge clk)”作为延迟,如下我常用赋值模板。

//生成输入信号din;

initial begin

#1;din = 0;//输入数据初始化为0;

#(10*CYCLE);//延迟10个时钟周期;

end