多核异构处理器是指集成了不同类型或架构的CPU的系统级芯片(SoC)。

例如,有些处理器同时包含了高性能的A核(如Cortex-A)和低功耗的M核(如Cortex-M)。

这样的设计可以让不同的CPU负责不同的任务,提高系统的效率和灵活性。

例如,A核可以用于人机交互、网络通信等复杂的应用,而M核可以用于实时控制、数据采集等对实时性要求高的应用。

然而,多核异构处理器也带来了一个挑战,那就是如何让不同的CPU之间进行有效和可靠的通信。一般来说,多核异构处理器A核与M核通信过程可以分为以下几个层次:

- 硬件层:这一层主要涉及到物理内存、寄存器、中断等硬件资源的分配和使用。不同的CPU可以通过共享一块物理内存空间来传输数据,也可以通过寄存器和中断来传递消息和信号。这一层的通信方式需要考虑数据的完整性、一致性、安全性和隔离性等问题。

- 驱动层:这一层主要涉及到虚拟化技术和消息框架的实现和使用。虚拟化技术(如Virtio)可以在设备之上提供一个抽象层,负责前后端之间的通知机制和控制流程。消息框架(如RPMsg)可以在虚拟化技术的基础上实现主处理核和协处理核之间进行消息通信的功能,支持不同的通信协议和格式。

- 应用层:这一层主要涉及到具体的应用程序和接口的开发和调用。应用程序可以根据自己的需求和场景,选择合适的通信方式和数据格式,通过设备文件或函数库等方式来实现与另一个CPU的通信。

在实际应用中,嵌入式处理器和单片机之间需要进行大量且频繁的数据交换,如果采用低速串行接口,则数据传输效率低,这将严重影响产品的性能;而如果采用高速并口,则占用管脚多,硬件成本将会增加。

CPU异构核间的通信方式是指不同类型或架构的CPU之间如何进行数据和信号的交换和协调。CPU异构核间的通信方式有多种,具体取决于CPU的设计、功能和应用场景。一般来说,CPU异构核间的通信方式可以分为以下几类:

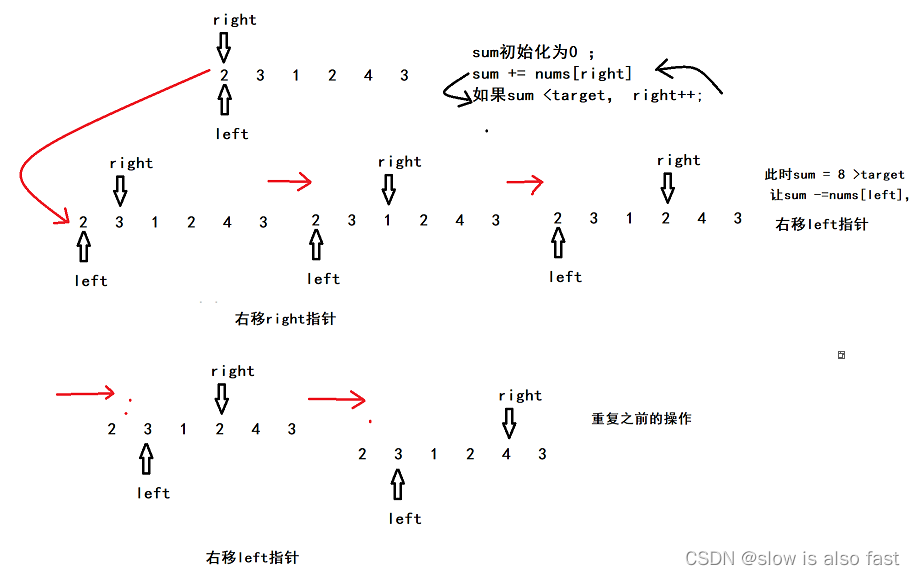

基于共享内存的通信方式:这种方式是指不同的CPU可以访问同一块物理内存空间,通过在内存中读写数据来实现通信。

这种方式的优点是速度快、开销小

缺点是需要解决内存访问冲突和一致性问题,以及保护内存安全性和隔离性。例如,ARM的big.LITTLE架构就采用了基于共享内存的通信方式,让高性能的big核和低功耗的LITTLE核可以共享同一块DDR内存,并通过缓存一致性协议来保证数据的正确性。

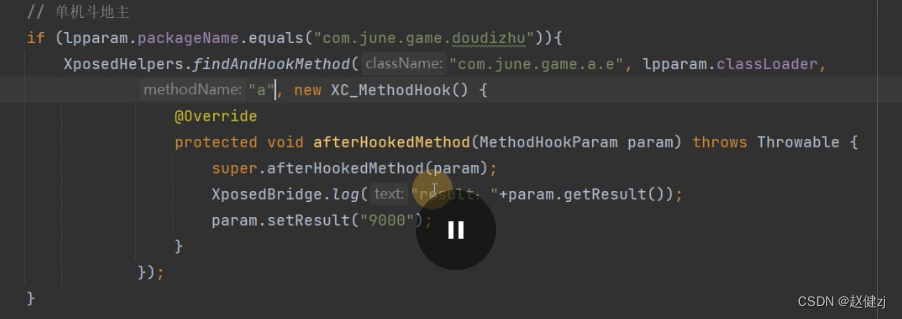

基于消息传递的通信方式:这种方式是指不同的CPU通过发送和接收消息来实现通信,消息可以包含数据、命令、状态等信息。

这种方式的优点是可以支持更复杂和灵活的通信协议,

缺点是需要额外的硬件或软件支持,以及增加了通信延迟和开销。

例如,Linux系统中的RPMsg框架就是一种基于消息传递的通信方式,它允许本地处理器与系统上可用的远程处理器通信,基于virtio框架实现了基于不同通道的通信。

基于中断或信号量的通信方式:这种方式是指不同的CPU通过触发或响应中断或信号量来实现通信,中断或信号量可以表示事件、请求、响应等信息。这种方式的

优点是可以实现实时性强、简单有效的通信,

缺点是需要协调好中断或信号量的分配和处理,以及避免过多或过频的中断或信号量影响系统性能。

例如,STM32MP1系列芯片中的IPCC外设就是一种基于中断或信号量的通信方式,它提供了六个双向通道信号,用于处理器间的数据交换的通知。

如果您想了解更多关于CPU异构核间的通信方式的具体情况和应用案例,您可以点击以下链接查看相关的文章:

- 多核异构处理器A核与M核通信过程解析 - 知乎

https://zhuanlan.zhihu.com/p/584710899 这篇文章介绍了基于NXP i.MX8系列芯片的A核与M核之间如何通过共享内存、寄存器中断和RPMsg框架来实现数据和消息的传递。

https://zhuanlan.zhihu.com/p/584710899 这篇文章介绍了基于NXP i.MX8系列芯片的A核与M核之间如何通过共享内存、寄存器中断和RPMsg框架来实现数据和消息的传递。 - 多核异构核间通信-mailbox/RPMsg 介绍及实验_liuxd3000的博客-CSDN博客

https://blog.csdn.net/liuxd3000/article/details/125858123 这篇文章介绍了基于STM32MP1系列芯片的A7核与M4核之间如何通过邮箱框架、远程处理器框架和RPMsg框架来实现数据和消息的传递。

https://blog.csdn.net/liuxd3000/article/details/125858123 这篇文章介绍了基于STM32MP1系列芯片的A7核与M4核之间如何通过邮箱框架、远程处理器框架和RPMsg框架来实现数据和消息的传递。 - 多核处理器 - 知乎

https://www.zhihu.com/topic/20307744/intro 这篇文章介绍了多核处理器的概念、分类、特点和发展趋势,以及多核处理器之间如何进行并行计算和负载均衡。

https://www.zhihu.com/topic/20307744/intro 这篇文章介绍了多核处理器的概念、分类、特点和发展趋势,以及多核处理器之间如何进行并行计算和负载均衡。