各位同学大家好,欢迎继续做客电子工程学习圈,今天我们继续来讲这本书,硬件系统工程师宝典。

上篇我们了解了SDRAM的存储技术以及SDRAM的发展历程,技术的进步推动着产品的升级,也加速了整个电子行业的发展。今天我们来讲一讲一些常用的总线及逻辑电平。

常用总线

I2C总线是由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备,只要求两条总线:一条串行数据线SDA、一条串行时钟线SCL。

SPI总线是一种同步串行外设接口,一般使用4条线:串行时钟线(SCLK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)和低电平有效的从机选择线(NSS)。

I2S(Inter-IC Sound)总线是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,广泛用于各种多媒体系统。

I2S有3个主要信号,分别是串行时钟SCLK、帧时钟LRCK和串行数据SDATA。

1.SCLK也叫位时钟,即对应数字音频的每一位数据,SCLK都有一个脉冲。SCLK的频率=2*采样频率*采样位数。

2.LRCK用于切换左右声道的数据。“1”表示正在传输的是右声道的数据,“0”表示正在传输的是左声道的数据。LRCK的频率等于采样频率。

3.串行数据SDATA即用二进制补码表示的音频数据。

CAN是控制器局域网络(Controller Area Network, CAN)的简称,是由研发和生产汽车电子产品著称的德国BOSCH公司开发的,并最终成为国际标准(IOS 11898),是国际上应用最广泛的现场总线之一。CAN总线结构简单,只有2根线与外部相连,内部集成错误勘探和管理模块。CAN总线的特点:

1.数据通信没有主从之分,任意节点可以向其他任何一个或多个节点发起数据通信。

2.多个节点同时通信时,通过节点信息优先级的先后顺序决定通信次序。

3.通讯距离最远可达10km(速率低于5Kbps),速率可达1Mbps(距离小于40m)。

4.CAN总线传输介质可以是双绞线和同轴电缆。CAN总线适用于大数据量短距离通信或长距离小数据量通信,实时性要求比较高,在多主多从或各个节点通信优先级对等的现场中使用。

常见的逻辑电平

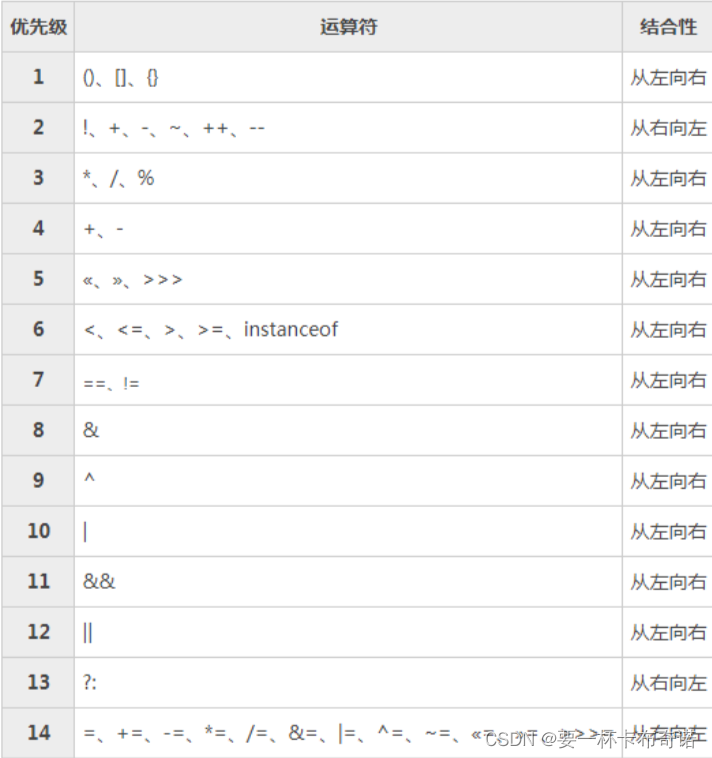

在电路互连时需要满足电平门限逻辑关系,常见的有TTL和CMOS逻辑电平。TTL器件和CMOS器件的逻辑电平的基本概念如下:

1.输入高电平(VIH):当输入电平高于VIH,则认为输入电平为高电平。

2.输入低电平(VIL):当输入电平低于VIL,则认为输入电平为低电平。

3.输出高电平(VOH):逻辑门的输出为高电平时,电压必须大于此值。

4.输出低电平(VOL):逻辑门的输出为低电平时,电压必须小于此值。

5.阈值电平(VT):相当于电路刚刚能“翻转”动作的临界值,介于VIL和VIH之间,若输入电压在阈值电平上下就会造成电路输出的不稳定。

6.IOH:逻辑门输出高电平时的负载电流(拉电流)。

7.IOL:逻辑门输出低电平时的负载电流(灌电流)。

8.IIH:逻辑门输入为高电平时的电流(灌电流)。

9.IIL:逻辑门输入为低电平时的电流(拉电流)。

一般情况下,以上参数有如下关系:

VOH>VIH>VT>VIL>VOL

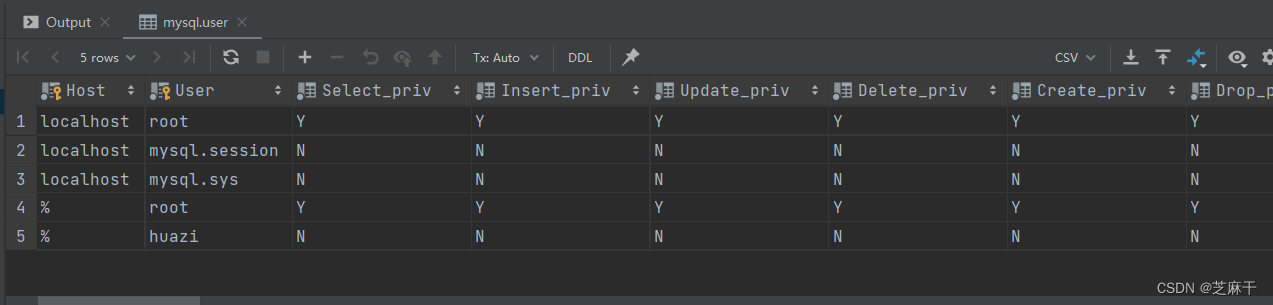

5V TTL、5V CMOS的逻辑电平、LVTTL逻辑电平和LVCMOS逻辑电平关系如下所示:

TTL和CMOS的逻辑电平关系

可以看到5V CMOS和5V TTL逻辑电平的输入/输出电平差别较大,互连时要特别注意。其中LVTTL和LVCMOS电平是TTL和CMOS对应的低压版本,它们的输入/输出电平与5V TTL逻辑电平很接近,便于互连。为保证电路的正确互连,需要确认互联部分的逻辑电平满足以下条件:

1.高电平逻辑:发送IC的VOH大于接收IC的VIH,且具备一定的噪声容限。

2.低电平逻辑:发送IC的VOL小于接收IC的VIL,且具备一定的噪声容限。若需要互连的IC满足以上条件即可互连,当互连的IC之间不满足互连条件时,需要有中间转换电路,一般有:

1.使用BJT或MOSFET实现逻辑电平转换。

2.使用电平转换芯片,如TI的74系列IC。

3.对于高电平驱动低电平可以串接电阻,阻值由驱动的电流和电阻的压降共同决定。

另外,整理了一些电子工程类的资料,分享给大家,目前有模拟电路、单片机、C语言、PCB设计、电源相关、FPGA、EMC、物联网、Linux相关学习资料,还有针对大学生的资料包,后续还会有更多资料分享给大家,助力大家学习,成就梦想~

关注同名公众号领取资料~

链接也可在往期文章中找(在文章的最后有链接)~

模拟电路设计的九个级别,你是模电几段?

![[信号与系统系列] 正弦振幅调制之差拍信号](https://img-blog.csdnimg.cn/cbf5c716ca1c44c180143e276928d1a6.png)