Timeplate Examples

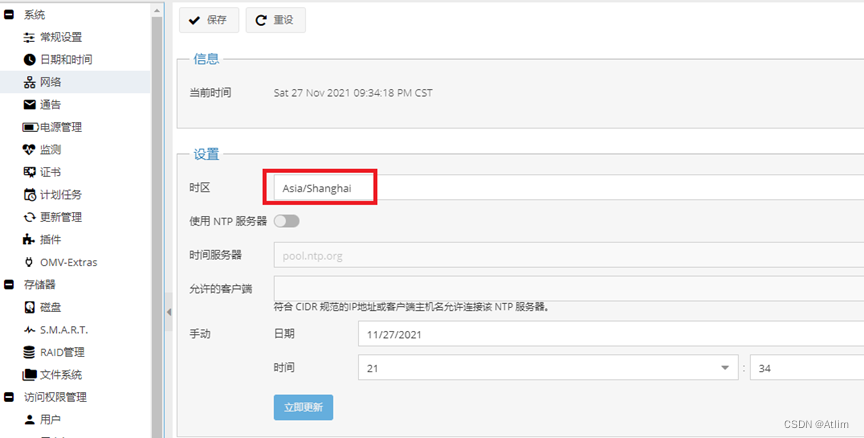

例如,移位周期40ns,占空比为50%,timeplate所示:

timeplate tp_shift =

force_pi 0;

measure_po 5;

pulse_clock 10 20;

period 40;

end;

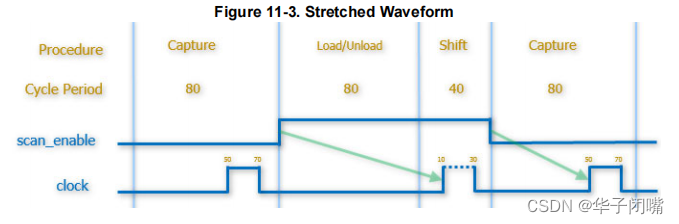

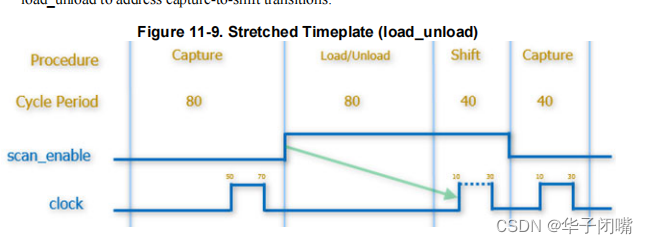

拉伸的timeplate可用于将时钟脉冲延迟40ns,同时保持相同的20ns占空比:

timeplate tp_load_and_capture =

force_pi 0;

measure_po 5;

pulse_clock 50 20;

period 80;

end;

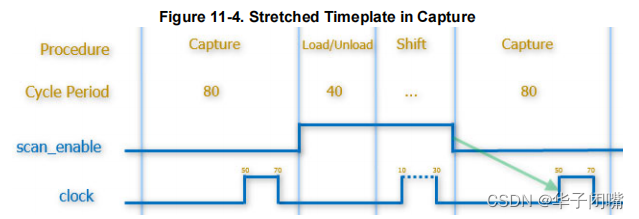

11-3,拉伸波形增加了从捕获到移位以及从移位到捕获的地址转换的延迟。

Default Timeplate

可以显式指定工具使用timeplate,也可以使用过程文件中的“set default_timeplate”语句更改默认时timeplate。建议不要更改默认计时器,因为该工具可能会自动创建不同的程序,并将使用换档程序的计时器来执行此操作。定义默认计时器可能会导致工具使用拉伸的计时器,这并不总是理想的。

Transitions From Shift to Capture

许多设计都有测试硬件,使用SE在换档期间禁用异步控制信号(如设置和重置)。Tessent工具中DFT信号插入的逻辑也使用SE来实现此目的。不能使用将post-shift cycle

添加到load_unload procedure

中,因为这会迫使SE在加载卸载结束之前转换到0。除非在移位和捕获期间关闭设置/复位信号,否则扫描单元数据将受到干扰,工具将报告D1 DRC违规。

有四种方法允许捕获中的第一个时钟脉冲被延迟,而不需要在加载-卸载过程中添加 post-shift dead cycles。

Stretched Timeplate in Capture (Recommended)

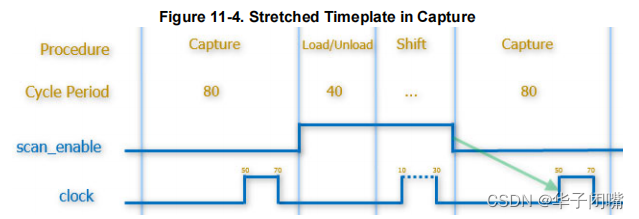

在SE转换为0后延迟捕获脉冲的推荐方法是在所有扫描启用转换后延迟时钟(推荐)中所述的延长timeplate。图11-4中的波形显示了相同的解决方案,如果仅适用于捕获到地址的shift-to-capture transitions.。

Extended Clock Sequential and Capture Procedures

如果限制无法改变移位和捕获之间的时钟周期,则时钟顺序和捕获过程可以延长到一个以上的周期,以实现与捕获中的拉伸时间板(推荐)部分中所述的拉伸时间盘方法类似的效果。

通过明确定义clock_sequential和捕获过程,可以扩展捕获过程。以下clock_sequential和捕获过程具有一个没有时钟脉冲的周期,之后是另一个包含时钟脉冲的循环。

timeplate tp1 =

force_pi 0;

measure_po 5;

pulse_clock 10 20;

period 40;

end;

procedure clock_sequential =

timeplate tp1;

cycle =

force_pi;

measure_po;

end ;

cycle =

pulse_capture_clock;

end;

end;

procedure capture =

timeplate tp1;

cycle =

force_pi;

measure_po;

end ;

cycle =

pulse_capture_clock;

end;

end;

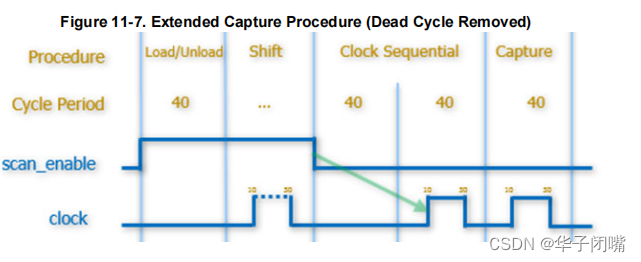

图11-5和图11-6中的波形说明,如果需要在最后一个时钟脉冲之后立即出现捕获时钟,则在捕获过程开始时具有死循环可能不适合于全速测试。如果这是精确的全速测试所需的,并且测试仪可以支持创建这样的波形,则可能需要删除捕获过程中的死循环,如本代码和图11-7所示:

procedure capture =

timeplate tp1;

cycle =

force_pi;

measure_po;

pulse_capture_clock;

end;

end;

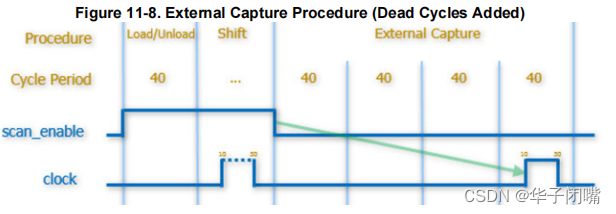

External Capture Procedures

对于at-speed测试,也可以在外部捕获过程中定义额外的死周期,以延迟捕获中的第一个时钟脉冲。使用set_external_capture_options命令在dofile中引用外部捕获过程。

An example is shown in this code and in

Figure 11-8

procedure external_capture ext_fast_cap_proc =

timeplate tp1 ;

cycle =

force_pi ;

end;

cycle =

end;

cycle =

end;

cycle =

pulse clock;

end;

end;

Named Capture Procedures

如果使用命名捕获程序(NCP),则可以使用所描述的技术、通过延长周期或通过显式增加死周期来延迟时钟脉冲

Post-shift Cycles

正如前面在“从移位到捕获的转换”的介绍中所解释的,只有不使用SE来禁用异步控制(例如设置和重置)的设计才能添加移位后死区以延迟时钟脉冲。这允许SE在捕获时钟脉冲之前有足够的时间从1过渡到0。但是,由于此解决方案不适用于许多设计,因此不建议使用。

Transition from Capture to Shift

扫描启用(SE)转换为1后,有两种方法可以处理慢速扫描启用转换。

Stretched Timeplate in load_unload (Recommended)

The在SE转换为1后延迟捕获脉冲的推荐方法是在所有扫描启用转换后延迟时钟中描述的拉伸timeplate

Dead Cycles Before Shift

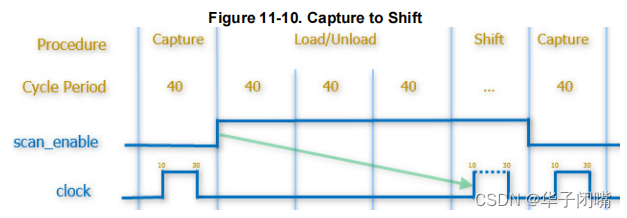

为了让SE有足够的时间在移位的第一个时钟脉冲之前从0转换到1,请在“apply shift”语句之前向load_unload过程添加任何数量的无时钟脉冲的死循环。该代码和图11-10中显示了一个示例:

timeplate tp1 =

force_pi 0;

measure_po 5;

pulse_clock 10 20;

period 40;

end;

procedure load_unload =

timeplate tp1;

cycle =

force clk 0;

force scan_en 1;

end;

cycle =

end;

cycle =

end;

apply shift 100;

end;

Delaying Other Signals in load_unload That Require Additional Delay

从捕获到转换中讨论的示例是无压缩设计的简单过程。类似的方法可用于EDT的设计,其中EDT_update信号也可能具有高扇出。此示例在edt_update的每个转换之后以及edt和移位时钟的脉冲之前添加一个死循环。

procedure load_unload =

timeplate tp1;

cycle =

force RST 0;

force CLK 0;

force scan_en 1;

force edt_update 1;

end;

cycle =

end;

cycle =

pulse edt_clock;

end;

cycle =

force edt_update 0;

end;

cycle =

end;

apply shift 100;

end;

Saving Timing Patterns

可以编写ATPG过程中生成的pattern,用于时序模拟和ATE上使用。

在测试过程文件中创建正确的计时信息后,该工具使用内部测试模式数据格式化程序以以下格式生成pattern:

•

Text format (ASCII)

•

Binary format

•

Wave Generation Language (WGL)

•

Standard Test Interface Language (STIL)

•

Verilog

•

Texas Instruments Test Description Language (TDL 91)

•

Fujitsu Test data Description Language (FTDL-E)

•

Mitsubishi Test Description Language (MITDL)

•

Toshiba Standard Tester interface Language 2 (TSTL2)

Features of the Formatter

以下是测试pattern数据格式化程序的主要特性。

•生成基本测试pattern数据格式。文本、Verilog和WGL(ASCII和binary)。

•生成ASIC供应商测试数据格式:TDL 91、FTDL-E、MITDL和TSTL2。

•支持并行加载扫描单元(Verilog格式)。

•读取外部输入pattern和输出响应,并直接转换为其中一种格式。

•读取外部输入pattern,执行良好或错误的机器模拟以生成输出响应,然后转换为任何格式。

•以任何测试数据格式仅写出pattern的子集。

•通过使测试数据文件在测试仪循环编号和模式编号之间交叉引用信息,促进故障分析。

•支持每种模拟数据格式的差分扫描输入引脚

Serial Versus Parallel Scan Chain Loading

当模拟测试pattern时,大多数时间都用于加载和卸载扫描链,而不是实际模拟电路对测试模式的响应。可以使用串行或并行加载,每个加载都会不同地影响总模拟时间。

模拟串行加载的主要优点是它模拟模式在测试仪上的加载方式。因此,可以获得电路操作的非常现实的指示。缺点是,对于每个模式,必须为扫描链寄存器计时至少与您所拥有的次数相同

扫描最长链中的cell。对于大型设计,模拟串行加载需要非常长的时间来处理一整套模式。

模拟扫描链的并行加载的主要优点是与串行加载相比,它大大减少了模拟时间。可以直接(并行)使用必要的测试模式值加载仿真模型,因为您可以在模拟器中访问设计中的内部节点。并行加载使您能够在合理的时间内使用ModelSim等使用Verilog格式的流行模拟器对整个pattern集执行时序模拟。

Parallel Scan Chain Loading

Y

可以通过扫描子链(一个或多个扫描单元的链,建模为单个库模型)的扫描输入和扫描输出引脚来完成并行加载,因为这些引脚对于时序模拟器模型和Tessent Shell内部模型都是唯一的。例如,您可以通过使用Verilog force语句更改每个子链的扫描输入引脚的值来并行加载扫描链。

在并行加载之后,您应用几次移位过程(取决于最长子链中扫描单元的数量,但通常仅一次),以将扫描值加载到子链中。仅几次模拟换档过程可以显著提高定时模拟性能。然后,可以观察每个子链的扫描输出引脚处的扫描输出值。并行加载确保扫描子链中的所有存储器元件实现与串行加载时相同的状态。此外,该技术与扫描设计风格或设计使用的扫描单元类型无关。此外,当使用并行加载编写模式时,不必指定时序模拟器和Tessent Shell之间的子链中内存元素的映射。该方法不限制扫描单元的库模型开发。

例如,测试pattern timing检查器在读取以下换档程序及其相应的timeplate时会发出错误消息:

timeplate gen_tp1 =

force_pi 0;

measure_po 100;

pulse CLK 200 100;

period 300; // Period same as shift clock off time

end;

procedure shift =

scan_group grp1;

timeplate gen_tp1;

cycle =

force_sci;

measure_sco;

pulse CLK; // Force shift clock on and off

end;

end;

The error message would state:

// Error: There is at least one stable high scan cell in the design. The

shift procedure period must be greater than the shift clock off time to

avoid simulation timing violations.

The following modified timeplate would pass timing rules checks:

timeplate gen_tp1 =

force_pi 0;

measure_po 100;

pulse CLK 200 100;

period 400; // Period greater than shift clock off time

end;

![[附源码]Nodejs计算机毕业设计基于Java网络游戏后台管理系统Express(程序+LW)](https://img-blog.csdnimg.cn/3783fec833164acab3362eceabd80242.png)

![[附源码]计算机毕业设计个人博客系统Springboot程序](https://img-blog.csdnimg.cn/aff2a18045b04eecbade889e6ad99f56.png)