本文主要记录了【沁恒蓝牙mesh】CH58x系统时钟配置与计算

- 💖 作者简介:大家好,我是喜欢记录零碎知识点的小菜鸟。😎

- 📝 个人主页:欢迎访问我的 Ethernet_Comm 博客主页🔥

- 🎉 支持我:点赞👍+收藏⭐️+留言📝

- 📣 系列专栏:沁恒蓝牙mesh二次开发

🍁 - 💬格言:写文档啊不是写文章,重要的还是直白!🔥

———————————————————————————————

【沁恒蓝牙mesh】CH58x系统时钟配置与计算

- 1.时钟配置

- 1.1 时钟树分析

- 1.2 检查寄存器的值

1.时钟配置

SDK中,时钟初始化一般都配置为60KHz,这个时钟值咋算出来的呢?打破砂锅问到底

SetSysClock(CLK_SOURCE_PLL_60MHz);

/**

* @brief 系统主频定义

*/

typedef enum

{

CLK_SOURCE_LSI = 0x00,

CLK_SOURCE_LSE,

CLK_SOURCE_HSE_16MHz = 0x22,

CLK_SOURCE_HSE_8MHz = 0x24,

CLK_SOURCE_HSE_6_4MHz = 0x25,

CLK_SOURCE_HSE_4MHz = 0x28,

CLK_SOURCE_HSE_2MHz = (0x20 | 16),

CLK_SOURCE_HSE_1MHz = (0x20 | 0),

CLK_SOURCE_PLL_80MHz = 0x46,

CLK_SOURCE_PLL_60MHz = 0x48,

CLK_SOURCE_PLL_48MHz = (0x40 | 10),

CLK_SOURCE_PLL_40MHz = (0x40 | 12),

CLK_SOURCE_PLL_36_9MHz = (0x40 | 13),

CLK_SOURCE_PLL_32MHz = (0x40 | 15),

CLK_SOURCE_PLL_30MHz = (0x40 | 16),

CLK_SOURCE_PLL_24MHz = (0x40 | 20),

CLK_SOURCE_PLL_20MHz = (0x40 | 24),

CLK_SOURCE_PLL_15MHz = (0x40 | 0),

} SYS_CLKTypeDef;

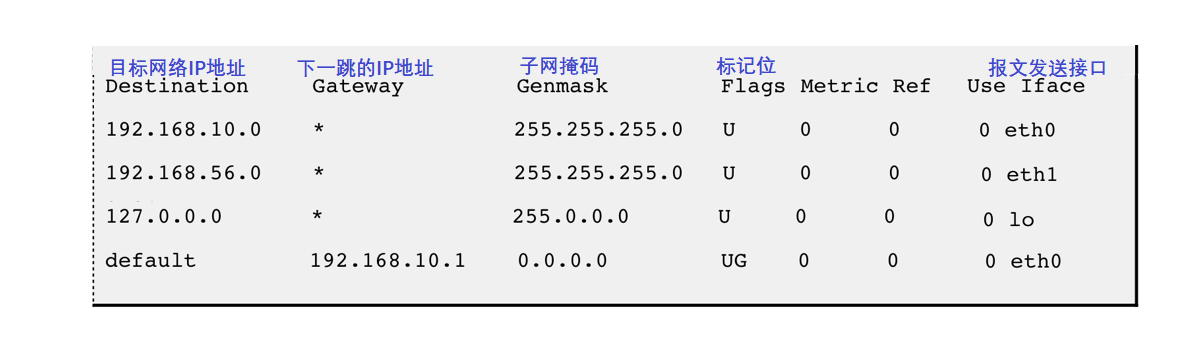

1.1 时钟树分析

首先,参考系统的时钟树图

外接,32MHz晶振经过PLL的15倍频后,再经过一个分频器,输出最终的 HCLK,作为其他一些外设的时钟源。

通过以上代码配置,我们可以得知,HCLK = 60MHz

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Os9bAngO-1691053307584)(pic/image-20230803165158697.png)]](https://img-blog.csdnimg.cn/d06a4145350749ec8c7cb9a0dffc636a.png)

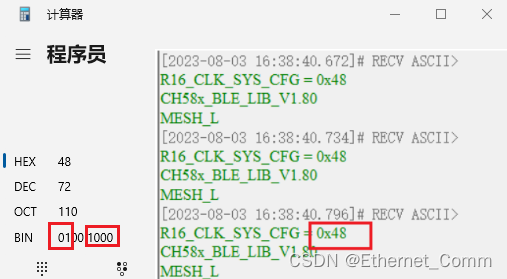

1.2 检查寄存器的值

在CH58X的芯片手册中,RTC是中部分,R16_CLK_SYS_CFG 寄存器是用于时钟配置

| 名称 | 访问地址 | 描述 | 复位值 |

|---|---|---|---|

| R16_CLK_SYS_CFG | 0x40001008 | 系统时钟配置寄存器 | 0x0005 |

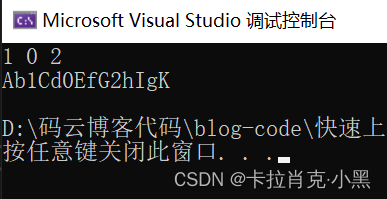

通过串口打印寄存器的值,看看计算过程

int main(void)

{

SetSysClock(CLK_SOURCE_PLL_60MHz);

/*串口配置*/

GPIOA_SetBits(bTXD1);

GPIOA_ModeCfg(GPIO_Pin_8, GPIO_ModeIN_PU); // PB8 RXD-配置上拉输入

GPIOA_ModeCfg(bTXD1, GPIO_ModeOut_PP_5mA);

UART1_DefInit();

PRINT("R16_CLK_SYS_CFG = 0x%02x \n", R16_CLK_SYS_CFG); /*打印寄存器的值*/

}

系统时钟配置寄存器(R16_CLK_SYS_CFG)

| 位 | 名称 | 访问 | 描述 | 复位值 |

|---|---|---|---|---|

| [15:8] | Reserved | RO | 保留。 | 00h |

| [7:6] | RB_CLK_SYS_MOD | RWA | HCLK 系统时钟源模式选择: 00/10:CK32M(默认 32MHz)进行分频; 01:PLL(默认 480MHz)进行分频; 11:CK32K(默认 32KHz)作为 HCLK。 | 00b |

| 5 | Reserved | RO | 保留。 | 0 |

| [4:0] | RB_CLK_PLL_DIV | RWA | HCLK 输出时钟分频系数,最小值为 2,0 代表最大值 32,写 1 将关闭 HCLK。 | 00101b |

寄存器的 bit[7:6] = 01 表示 PLL分频,480MHz bit[4:0] = 1000 表示分频系数是 8,所以时钟周期是 480MHz / 8 =60MHz ,和代码配置一致