文章目录

- 1.怎么使用quartus2编译工程生成sof文件?

- 2.怎么使用quartus2下载程序到fpga芯片?

- 3.为什么sof文件烧录后,fpga断电重启,程序会丢失?

- 4.怎么使用quartus2把sof文件转换成jic文件?

- 5.quartus2分配引脚的三种方式。

- 6.什么时候需要做时序约束?

- 7.什么是时序约束?

- 8.哪个是quartus2的工程文件?

- 9.如何建立时序约束?

- 10.硬件调试

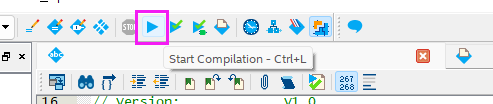

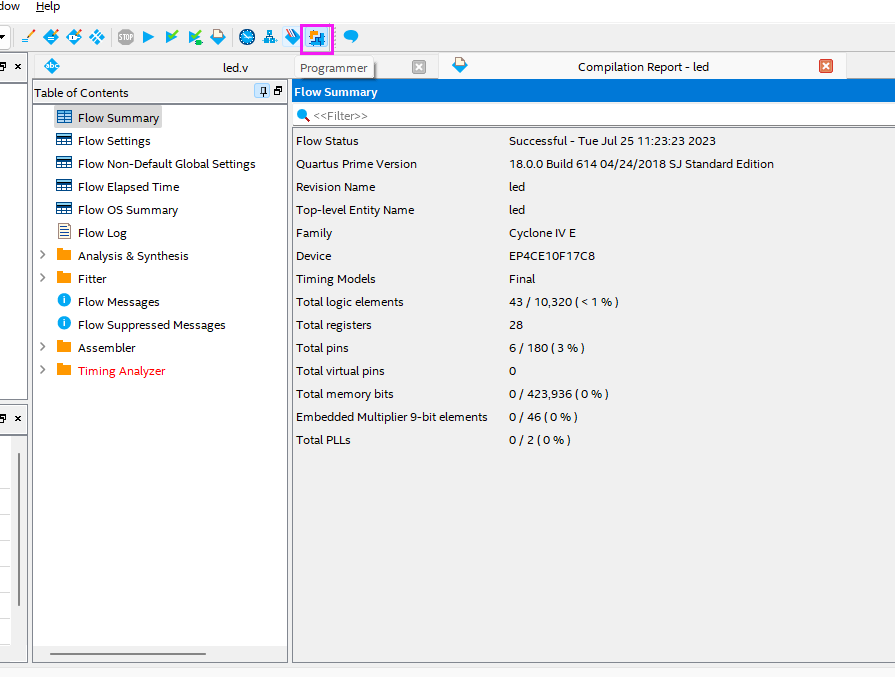

1.怎么使用quartus2编译工程生成sof文件?

答:在写完代码,进行“分析与综合”,并且分配好引脚之后,就可以编译工程。

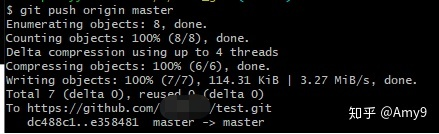

2.怎么使用quartus2下载程序到fpga芯片?

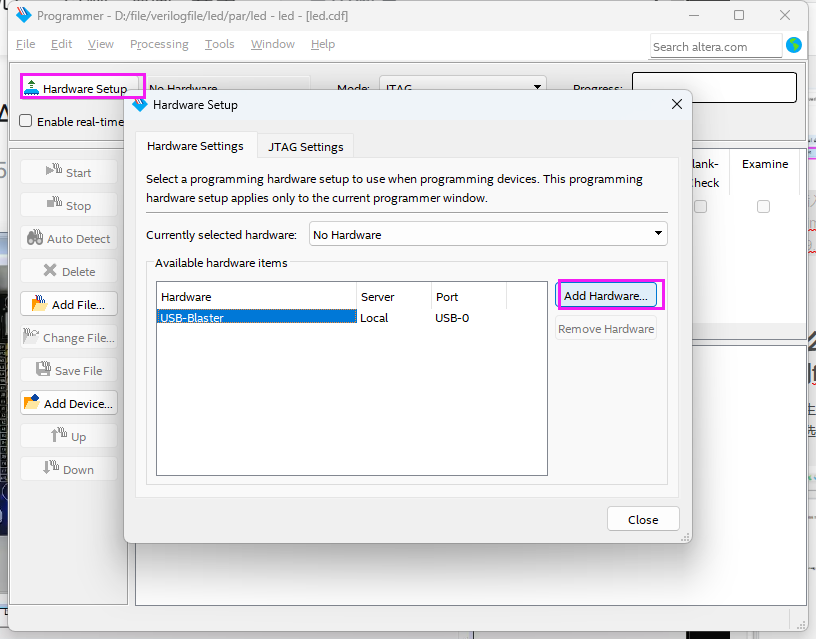

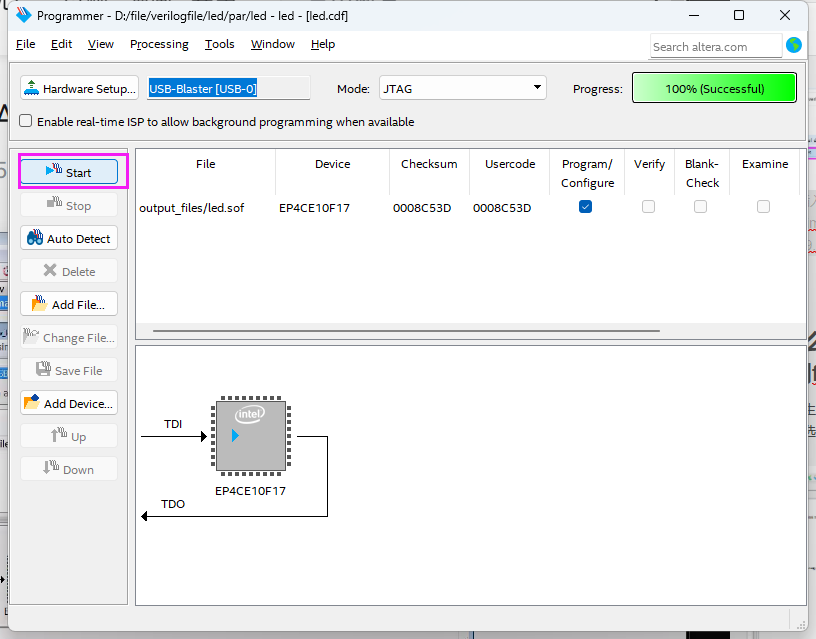

答:编译生成sof文件后,点击programmer按键,默认选择当前项目的sof文件。

在这不要点add hardware,双击usb-blaster即可。

3.为什么sof文件烧录后,fpga断电重启,程序会丢失?

答:因为sof文件时烧录到fpga中的,如果想让程序不丢失,需要使用jic文件进行烧录。

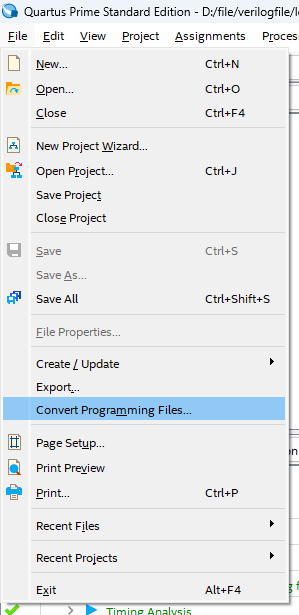

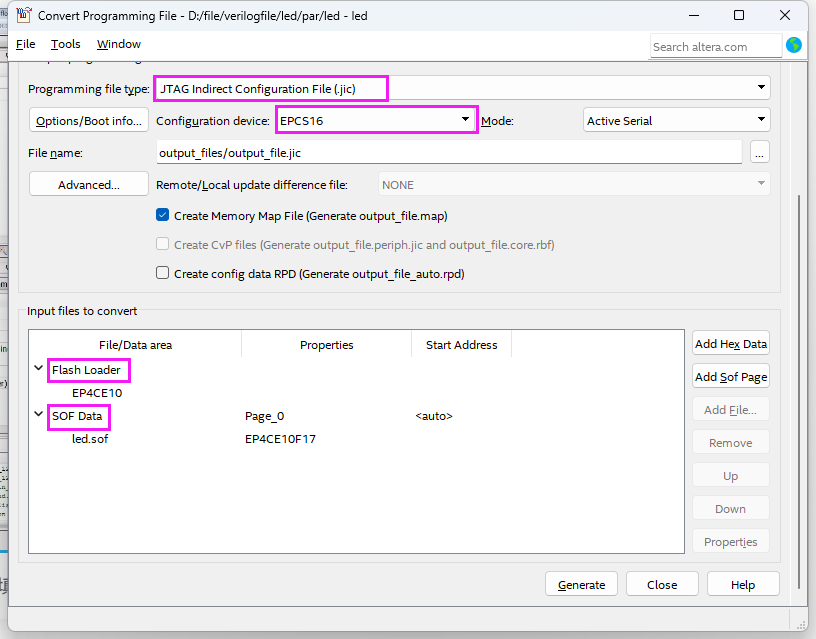

4.怎么使用quartus2把sof文件转换成jic文件?

答:

5.quartus2分配引脚的三种方式。

答:

正点原子视频,在后面

https://www.bilibili.com/video/BV1QF41137Kf?p=7&vd_source=449ef7868b4c0d5be60285446c653a0e

博客

https://blog.csdn.net/qq_22168673/article/details/89670829

6.什么时候需要做时序约束?

答:

1.clk工作频率比较大,比如网口通信实验(千兆)。

2.占用芯片的逻辑资源比较多的时候,比如80%以上,有可能会导致功能不正确。

3.代码没问题,但是突然加了一个逻辑之后,导致代码出错,就要考虑时序约束的问题。

7.什么是时序约束?

答:时序约束(Timing Constraints)是在数字电路设计中,用于定义和规定各个时钟信号、数据路径和时序要求之间的关系和限制。时序约束对于确保设计在特定时钟频率下的正确功能和可靠性非常重要。

在数字电路中,时序约束描述了信号的到达时间、时钟的边沿和时钟周期等关键时刻。它确保信号在正确的时间点到达目标电路,以满足设计规范和时序要求。时序约束通常包含以下信息:

-

时钟约束:包括时钟的频率、相位关系、占空比等参数。时钟约束定义了时钟信号的时序特性,确保数据在正确的时钟边沿进行捕获和处理。

-

数据路径约束:定义了数据在不同逻辑元素(比如寄存器、组合逻辑、时钟域之间的接口)之间传输的时序要求。它包括数据传输延迟、数据保持时间、数据建立时间等参数,以确保数据在正确的时刻到达目标寄存器或逻辑元素。

-

约束路径:定义了信号在电路中的传播路径和时序要求。对于复杂的数据路径,约束路径可以指定数据从源到目标的具体路径,以确保在时序要求下的正确传输和操作。

时序约束在设计过程中扮演了重要的角色。它们用于静态时序分析、时钟分析、时序验证和时序优化。通过遵循正确的时序约束,设计人员可以确保电路在指定的时序要求下正常工作,并提高系统的性能和可靠性。

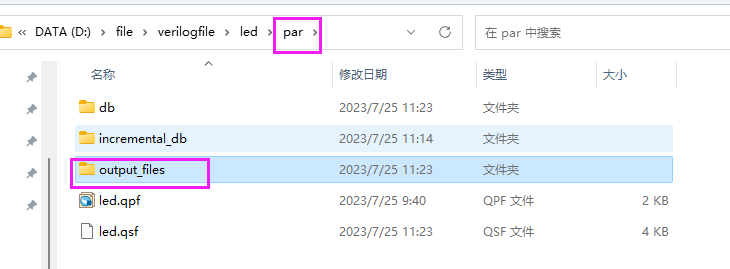

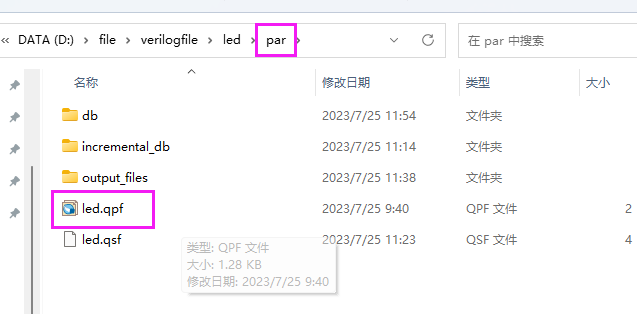

8.哪个是quartus2的工程文件?

答:

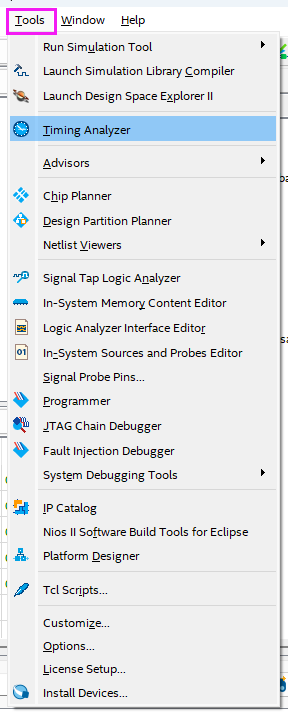

9.如何建立时序约束?

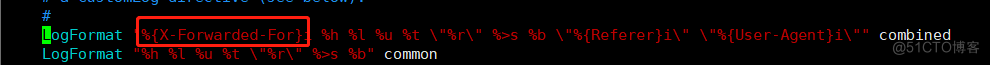

答:在老版本quartus Ⅱ 13.0里的assignments里有时序约束向导,但是新版本不知道放哪去了,先空着吧。但是可以通过这种方式添加sdc文件。

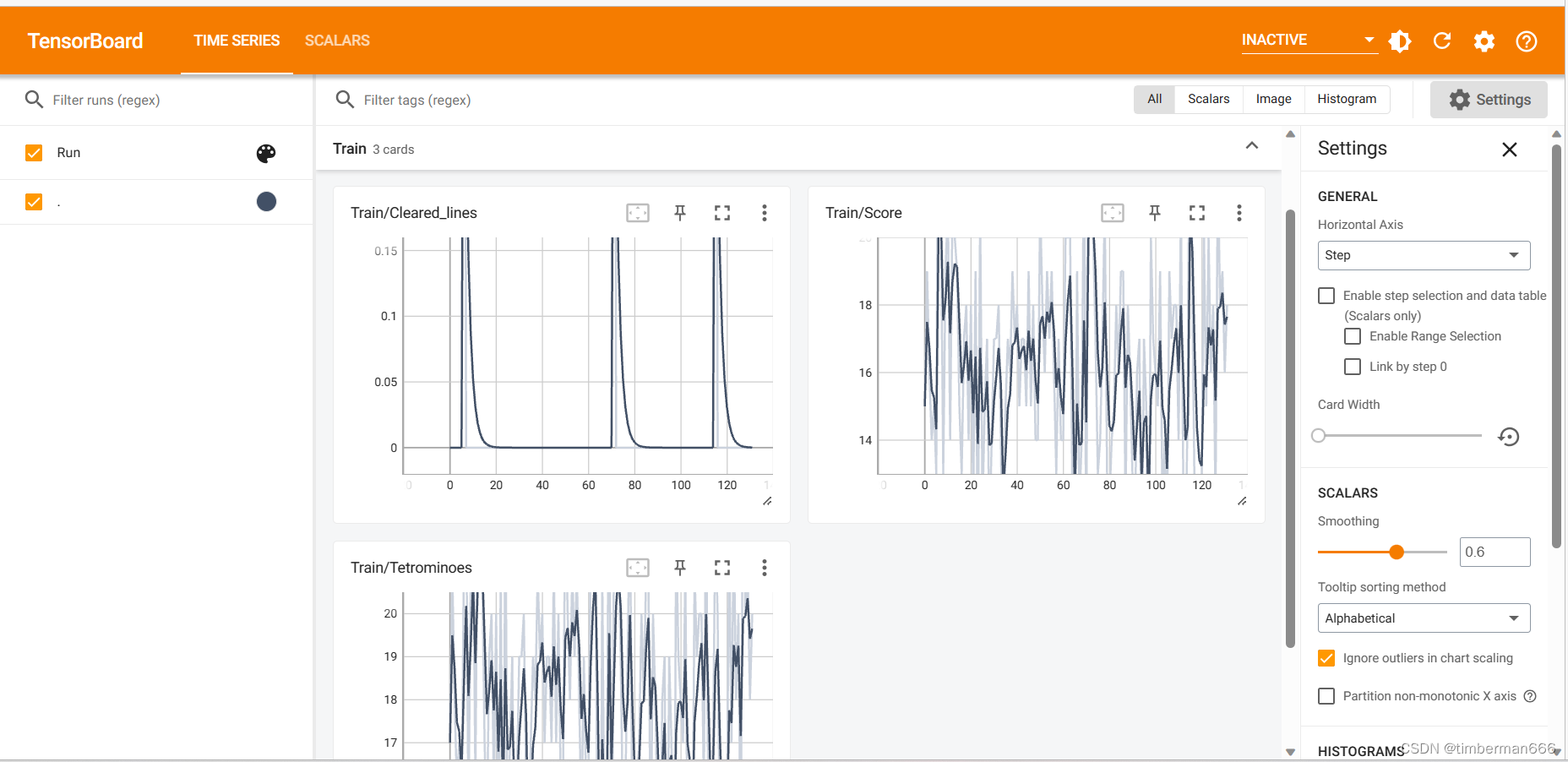

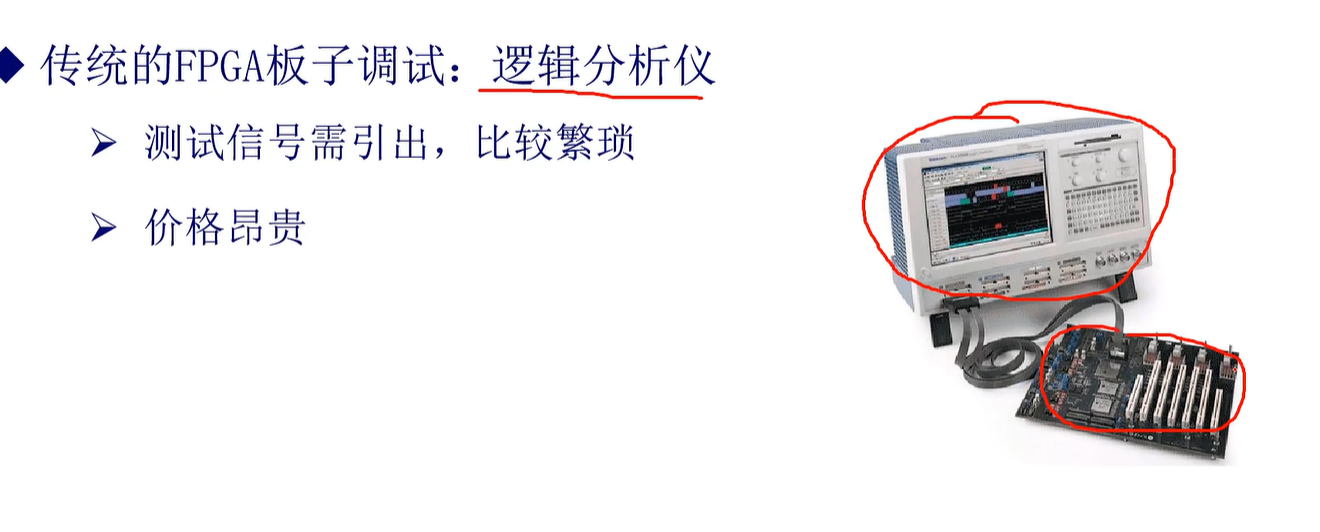

10.硬件调试

答:

signal tap Ⅱ软件