🔥点击查看精选 CXL 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/131842121】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

- 💬 直达博主:loveic_lovelife 。(搜索或点击扫码)

文章目录

- 1. Bias Mode 背景与分类

- 1.1 Bias 背景

- 1.2 Bias 分类

- 1.2.1 Host Bias

- 1.2.2 Device Bias

- 2. 实现 Bias Mode 的要求

- 3. Bias Mode 管理与示例

- 4. Q&A

- 5. 参考

CXL Bias Topic 分以下 3 部分,本篇是第 1 篇。

- CXL Bias Mode (1) - Bias Mode 背景与分类👈

- CXL Bias Mode (2) - 实现 Bias Mode 的要求

- CXL Bias Mode (3) - Bias Mode 管理与示例

为便于描述,Host Bias Coherency Model 在下文中简写为 Host Bias,Device Bias 同理。当我们提到 Accelerator 时,是指 Device 中的 Accelerator;当我们提到 Device Memory 时,是指 Accelerator-attached Memory;当我们提到 HDM-DB 时,单指 Type 2 Device 中的 HDM-DB Memory。

1. Bias Mode 背景与分类

1.1 Bias 背景

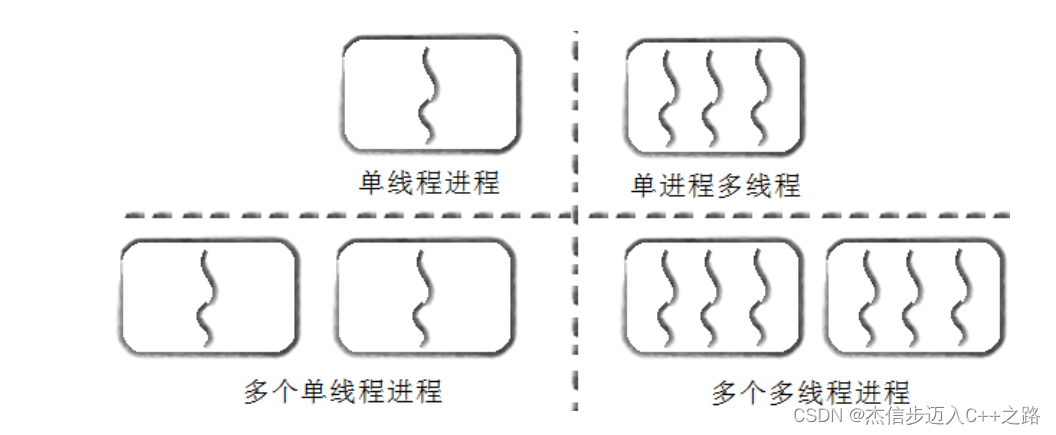

我们知道,对于 Type 1 Device,Device 可以访问到 Host Memory,由 Host LLC 中的 Local Snoop Filter 来管理其在 Host CPU Cache Hierarchy 及 Device Cache 中的缓存一致性。对于 Type 2 Device,Host 同样可以访问到 Device Memory。按照 Type 1 的逻辑,理应由 Device 中的 DCOH 来维护缓存一致性。但显然 CXL 没有这么干,而是提出了一种 Bias Based Coherency Model,基于偏向性的一致性模型。

为什么这么干?我们回忆下 CXL 三大主打特性:一致性接口、低延时、非对称复杂度。显然,CXL 是要通过这种带有偏向性的模型来降低 Device 端的设计复杂度。

1.2 Bias 分类

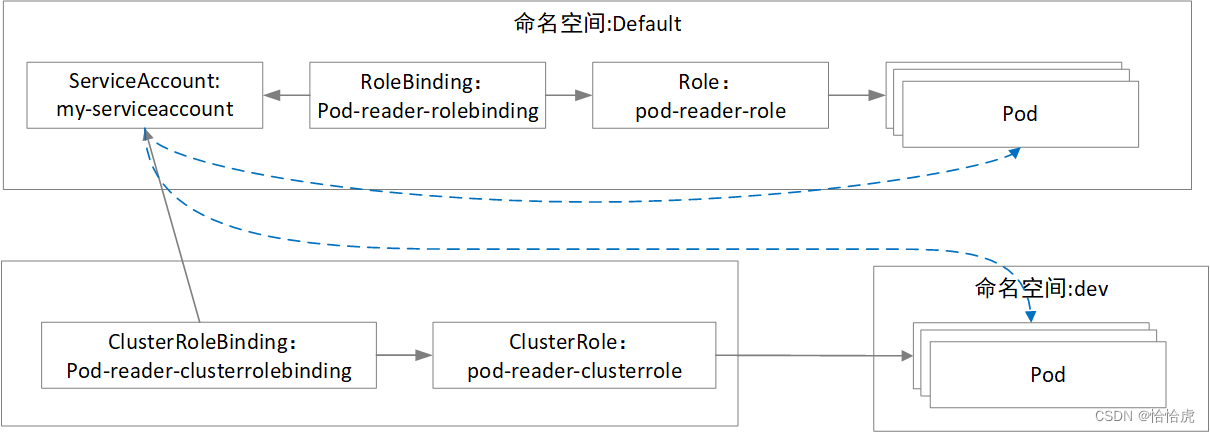

Type 2 Device 中的 HDM-D 及 HDM-DB 区域的 Coherency Model 支持两种 Bias Mode:Host Bias 及 Device Bias,偏向谁就由谁来管理缓存一致性。Host Bias 即偏向 Host,该 Memory 区域跟 Host Memory 无异,由 Host Coherent Bridge 管理一致性;Device Bias 即偏向 Device,Device 来保证外部没有该区域的 Cacheline 副本,由 Device DCOH 管理缓存一致性。

注意:这两种 Bias Mode 都是 HDM-D 或 HDM-DB 的,切勿认为 HDM-H 是 Host Bias、HDM-D 是 Device Bias 。Type 2 Device 中的 HDM-DB 也支持 Bias Mode。

1.2.1 Host Bias

Host Bias Coherent 是一种 Host 管理下的缓存一致性模型。若 HDM-D/DB Region 为 Host Bias,其地位跟 Host Memory 相同,既可以缓存在 Host Cache 供 Host CPU 直接取用, 也可以缓存在 Device Cache 内供 Device 内的 Accelerator 用,由 Host 中的 LLC Local SF 管理缓存一致性。

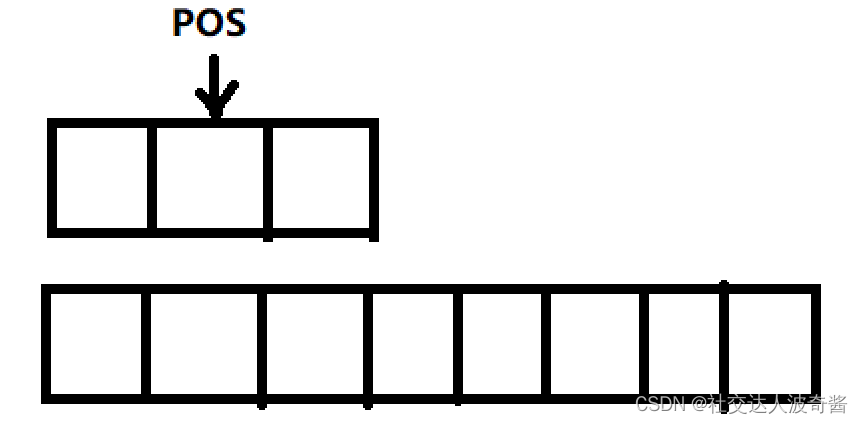

Host、Device 访问 HDM-D/DB Host Bias 区域时的数据流向图。如环路①,对于 Host,其可以直接访问到 Device Memory 中的 Host Bias 区域;如环路②,对于 Device,其访问 Device Memory 中的 Host Bias 区域时需要向 Host 发起 D2H Cache 请求,Host 通过 CXL.mem 将该请求转发回 Device DCOH,Device 内部完成数据访问,无需反馈 Rsp 或 Data 给 Host。

显然,Host Bias Mode 下的 Device Memory 更有利于 Host 访问,对 Device 访问较为不利。因此,Host Bias 常用于 Host 直接 Load/Store 访问 Device Memory 的场景。

1.2.2 Device Bias

Device Bias Coherent 是一种 Device 管理下的缓存一致性模型。若 HDM-D/DB Region 为 Device Bias,该 Region 只能缓存在 Device Cache,不能缓存在 Host Cache,也不能缓存在 Remote CPU Cache 内。

说白了,Device Bias 区域只对 Device 开放 Cacheable 权限,是一种 Device Cache 独享的 Cacheline。因为独享,所以 Device Cache 对该 Cacheline 做任何操作都不需要跟 Host 及 Remote CPU Clusters 交互,不需要跟该 Device 之外的 Cache 做 Snoop 等一致性管理。这样一来能够 降低设计复杂度,二来能够降低 Device 访问 HDM 流程上的复杂度从而 降低时延、提升吞吐量(Throughput)。

下图是 Device、Host 访问 HDM-D/DB Device Bias 区域时的数据流向图。如环路①,Device 可以对 Device Memory 内的 Device Bias 区域进行访问,无需绕道 Host,没有任何 CXL 链路上的.cachemem 操作;如环路②,Host 仍然可以访问到 Device Bias 区域并根据请求类型将该 Data Line 缓存在 Host Cache 中,但是 Device 可以通过环路③将其在 Host Cache 内的 Cacheline Invalidate 掉,使 Host 丧失该 Cacheline 的相关权限。

显然,Device Bias Mode 下的 Device Memory 更有利于 Device 访问。因此,Device Bias 常用于 Device 直接 Load/Store 访问 Device Memory 的场景。

不是说 Device Bias 区域只能缓存在 Device Cache 中、不能缓存在 Host Cache 中么?上图环路②访问后将相关 Data Line 缓存在 Host Cache 该作何解释?以下是笔者的理解:

Host 在发起访问 Device Memory 访问请求时,其并不知道该区域的 Bias Mode 也无需知道。如果访问的区域为 Device Bias 且请求获得该 Data Line 的 Shared 或 Exclusive 权限,Device DCOH 会处理一致性并 姑且同意 该请求。在同意请求后,Device Cache 内该 Data Line 已经变为了 Shared 或 Invalid,该区域 实际已经变为了 Host Bias 。如果 DCOH 觉得维持在 Host Bias 没问题,那就继续保持该状态,心甘情愿将 Bias Mode 切换为 Host Bias,Host 内的 Local SF 会监测该 Data Line 在 Host Cache 内的副本并维护缓存一致性;如果 DCOH 觉得有问题,Device 仍要继续独享该 Data Line,其不打算让出该 Data Line 的 Cache 权限,其可以通过 CXL.cache 发送 RdOwnNoData 或者通过 CXL.mem 发送 S2M BISnp*给 Host 要求其放弃 Cache 中的该 Cacheline,仍然由 Device Cache 独享该 Cacheline,重新切回到 Device Bias。这个 Device 发起的 Bias Flip 的操作,即 Spec 中所言的 “The host may be forced to give up ownership by the accelerator“。

2. 实现 Bias Mode 的要求

CXL Bias Mode (2) - 实现 Bias Mode 的要求

3. Bias Mode 管理与示例

CXL Bias Mode (3) - Bias Mode 管理与示例

4. Q&A

- Bias Mode 是什么?

Type 2 Device Memory 中 Page 的偏向性,决定了谁来直接管理其一致性。 - Bias Mode 存放在哪?谁来管理?

直接放在 Device 中的 Bias Table,由 DCOH 来直接管理。Host 可以通过 SF 或访问 Meta 来推测或间接更新 Bias Mode。 - Host 能看到 Bias Mode 吗?

Host 无法直接看到确切的 Bias Mode,其可以通过 SF 或访问 Meta 来推测或间接更新 Bias Mode。 - HDM-DB 也有不同的 Bias Mode 吗?

Bias Mode 是 Type 2 Memory 的属性,Type 2 类型的 HDM-D 及 HDM-DB 均支持 Bias Mode。 - 两者不同的 Bias 切换方式中,由谁发起 Bias 切换?

软件和硬件都可以发起 Bias Mode 切换请求。 - 不同的 Bias Mode 应用场景是什么?

Host Bias 常用于 Host 分配任务或回收出运算结果,Device Bias 常用于 Accelerator 运算。

5. 参考

- CXL Base Spec, r3.0

- CXL 简介_maxwell2ic 的博客-CSDN 博客

- CXL 协议(1.1 版本)学习笔记(一) - 知乎 (zhihu.com)

- CXL Meta Data 介绍

|

|

🔥 精选往期 CXL 协议系列文章,请查看【 CXL 专栏】🔥

⬆️ 返回顶部 ⬆️