移位寄存器

1 4 位移位寄存器

module top_module(

input clk,

input areset, // async active-high reset to zero

input load,

input ena,

input [3:0] data,

output reg [3:0] q);

always @(posedge clk or posedge areset) begin

if (areset)

q<=4'h0;

else if(load)

q<=data;

else if(ena)

q[3:0]={1'b0,q[3:1]};

end

endmodule

2 100bit的可左移或右移的移位寄存器

设计一个100bit的可左移或右移的移位寄存器,附带同步置位和左移或右移的使能信号。本题中,移位寄存器在左移或右移时,不同于Problem106的补0和直接舍弃某一bit位,本题是要求在100bit内循环移动,不舍弃某一bit位同时也不补0。

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always @(posedge clk) begin

if(load)

q<=data;

else if(ena==2'b01)

q<={q[0],q[99:1]};

else if(ena==2'b10)

q<={q[98:0],q[99]};//对本身移位,是q不是datd

else if(ena==2'b00||ena==2'b11)

q<=q;

end

endmodule

3 一个64-bit带同步置位的算术移位寄存器

设计一个64-bit带同步置位的算术移位寄存器。该寄存器可以由amount控制来移动方向和每次移动的次数。

算术右移移位寄存器中的符号位(q [63])移位,不像是逻辑右移中进行补零的操作。而是保留符号位后再进行移位。

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always @(posedge clk) begin

if (load)

q<=data;

else if (ena==1'b1 && amount==2'b00)

q<={q[62:0],1'b0};

else if (ena==1'b1 && amount==2'b01)

q<={q[55:0],8'b0};

else if (ena==1'b1 && amount==2'b10)

q<={q[63],q[63:1]};

else if (ena==1'b1 && amount==2'b11)

q<={{8{q[63]}},q[63:8]};

else if (ena==1'b0)

q<=q;

end

endmodule

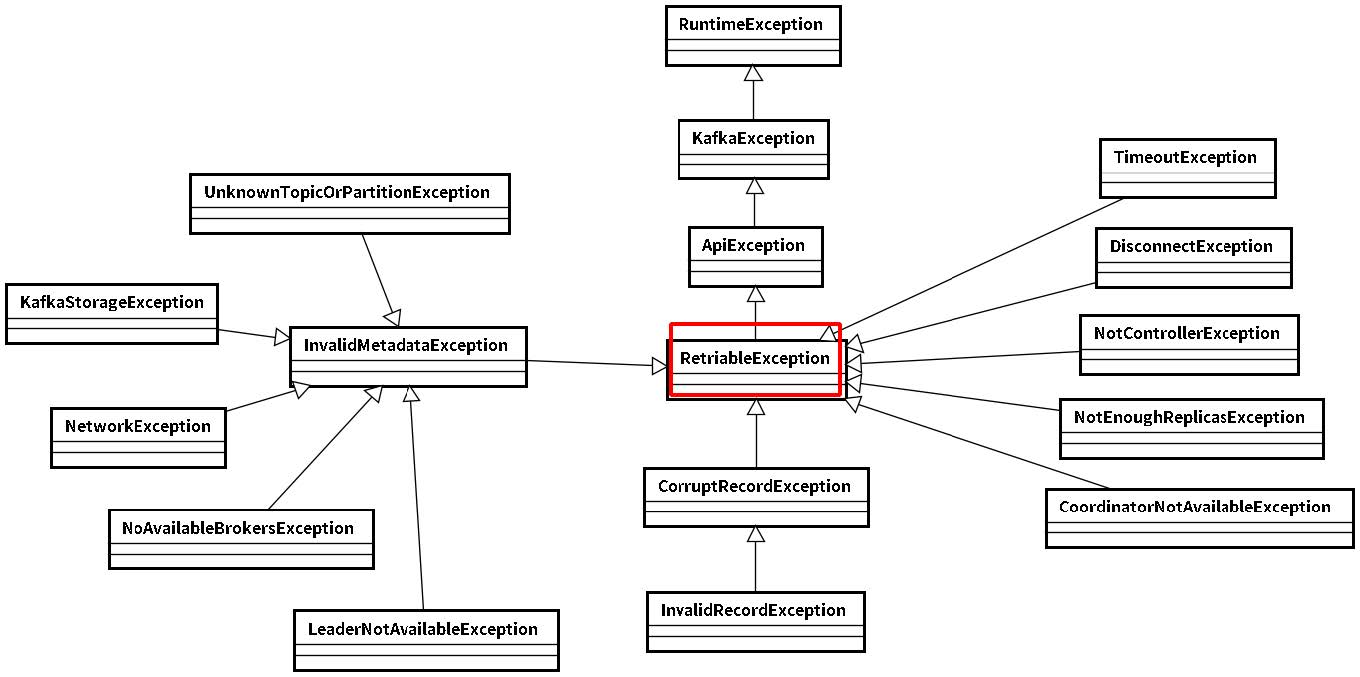

4 Lfsr5

线性反馈移位寄存器(LFSR)是通常带有几个XOR门来产生下一状态的移位寄存器。Galois LFSR是一个特殊的移位寄存器。其中带有"tap"位的位置与输出位XOR产生下一个值没有"tap"位标志的正常移位。如果"tap"位置经过仔细选择后,LFSR将设置为最大长度。再重复之前LFSR的最大长度为2^n-1

module top_module(

input clk,

input reset, // Active-high synchronous reset to 5'h1

output [4:0] q

);

always @(posedge clk) begin

if(reset)

q<=5'h1;

else begin

q[4]<=0^q[0];

q[3]<=q[4];

q[2]<=q[3]^q[0];

q[1]<=q[2];

q[0]<=q[1];

end

end

endmodule

5 Mt2015 lfsr

module top_module (

input [2:0] SW, // R

input [1:0] KEY, // L and clk

output [2:0] LEDR); // Q

move move_1[2:0](.r(SW),

.q({LEDR[1]^LEDR[2],LEDR[0],LEDR[2]}),

.L({3{KEY[1]}}),.clk({3{KEY[0]}}),.Q(LEDR));

endmodule

module move(input r,input q,input L,input clk,output Q);

always @(posedge clk) begin

Q<=L?r:q;

end

endmodule

6 Lfsr32

抽头点为32,22,2,1。Build a 32-bit Galois LFSR with taps at bit positions 32, 22, 2, and 1.

module top_module(

input clk,

input reset, // Active-high synchronous reset to 32'h1

output reg [31:0] q

);

always@(posedge clk)begin

if(reset)

q <= 32'h1;

else begin

q <= {q[0],q[31-:9],q[22]^q[0],q[21:3],q[2]^q[0],q[1]^q[0]};

end

end

endmodule

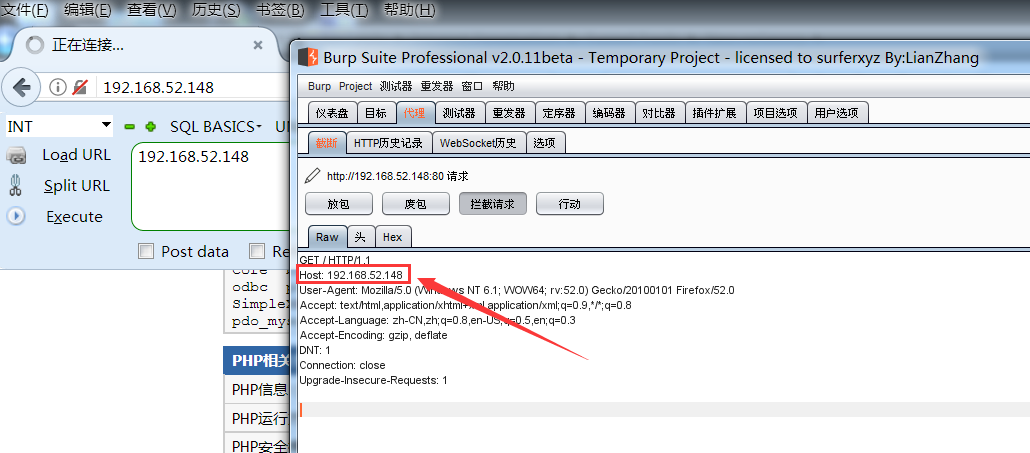

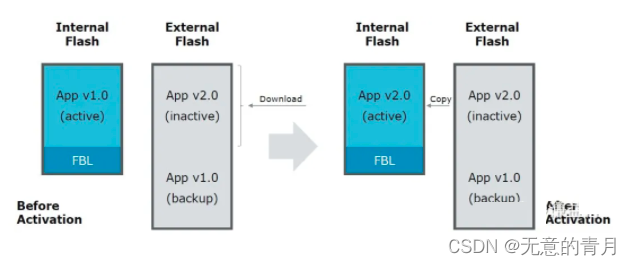

7 shift register

实现下图中的电路

module top_module (

input clk,

input resetn, // synchronous reset

input in,

output out);

always @(posedge clk) begin

reg q1,q2,q3;

if (~resetn) begin

out<=1'b0;

q1<=1'b0;

q2<=1'b0;

q3<=1'b0;//注意reset后需要全部置0

end

else begin

q1<=in;

q2<=q1;

q3<=q2;

out<=q3;

end

end

endmodule

8 shift register

module top_module (

input [3:0] SW,

input [3:0] KEY,

output [3:0] LEDR

); //

MUXDFF MUXDFF1[3:0](.w({KEY[3],LEDR[3:1]}),.e({4{KEY[1]}}),.l({4{KEY[2]}}),.r(SW),.clk({4{KEY[0]}}),.Q(LEDR));

endmodule

module MUXDFF (input w,input e,input l,input r,input clk,output Q);

always@(posedge clk) begin

Q<=l?r:(e?w:Q);

end

endmodule

9 3-INPUT LTU

没写出来

module top_module (

input clk,

input enable,

input S,

input A, B, C,

output Z );

reg [7:0] q;

always @(posedge clk) begin

if (enable)

q<={q[6:0],S};

end

always @(*) begin

case ({A,B,C})

3'd0: Z=q[0];

3'd1: Z=q[1];

3'd2: Z=q[2];

3'd3: Z=q[3];

3'd4: Z=q[4];

3'd5: Z=q[5];

3'd6: Z=q[6];

3'd7: Z=q[7];

endcase

end

endmodule

![Leetcode 1691. 堆叠长方体的最大高度 [Java/C++] 排序+动态规划(附详细证明过程)](https://img-blog.csdnimg.cn/db9cab8b3df74b89951f3aad8e551a6e.png)