系列文章之 上章

FPGA-DFPGL22学习5-VERILOG

文章目录

- 系列文章之 上章

- 前言

- 一、原理图

- 端口对应

- 二、程序设计

- 三、程序编写

- 四、仿真

- 五、工程下载

前言

@和原子哥一起学习FPGA

开发环境:正点原子 ATK-DFPGL22G 开发板

参考书籍:

《ATK-DFPGL22G之FPGA开发指南_V1.1.pdf》

个人学习笔记,欢迎讨论

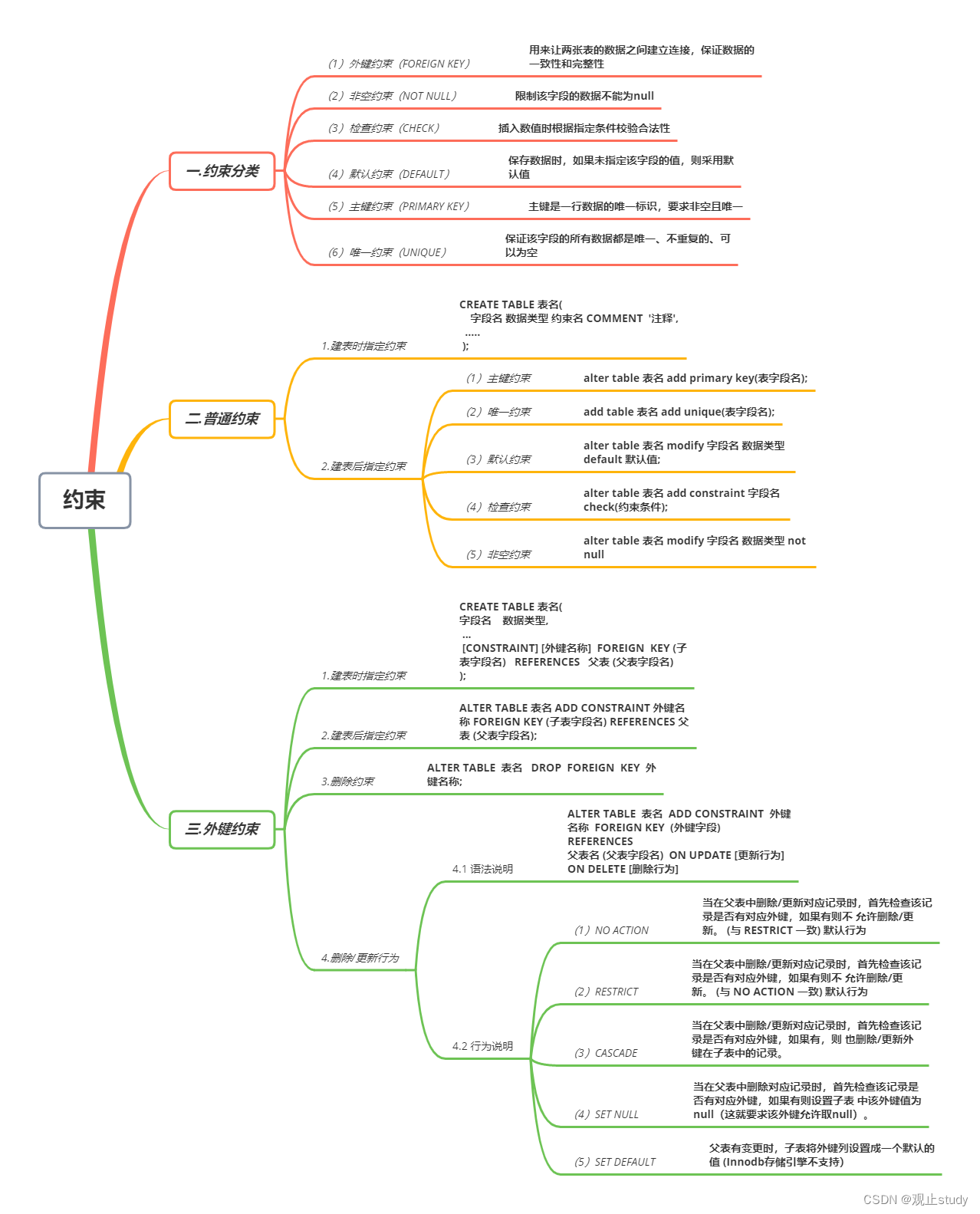

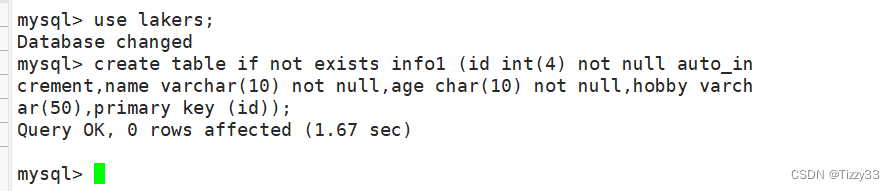

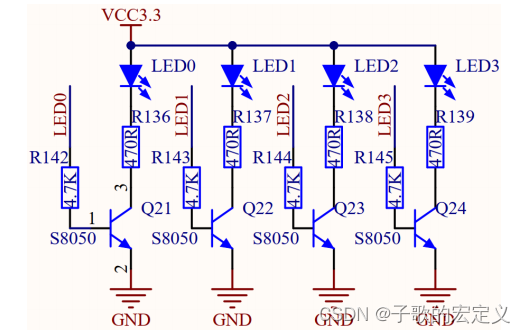

一、原理图

LED0-LED3 这 4 个发光二极管均有连接三极管,这是由于 LED0~LED3 连接到了 FPGA的 IO 口,但是电压只有 1.35V,电压较低,所以此处连接三极管是为了起到放大信号的作用。

当 FPGA 输出 LED0 到 LED3 为高电平时,三极管导通,点亮 LED 灯;

当 FPGA 输出 LED0 到 LED3 为低电平时,三极管截止,LED 灯熄灭。

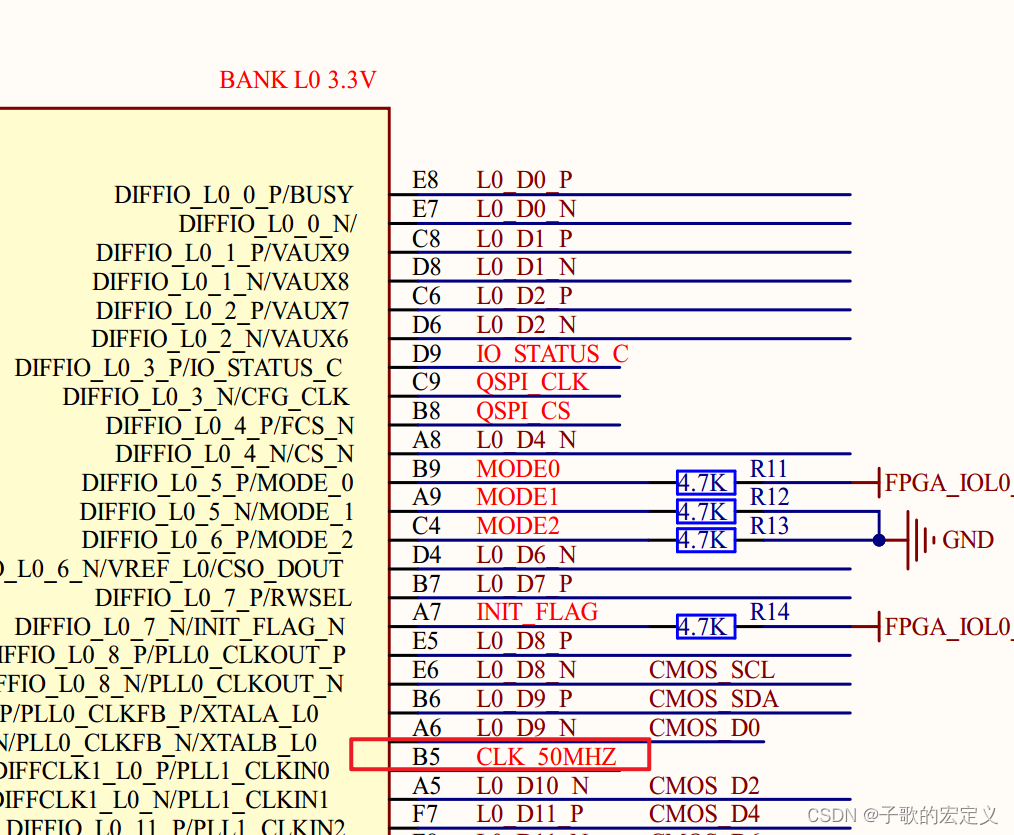

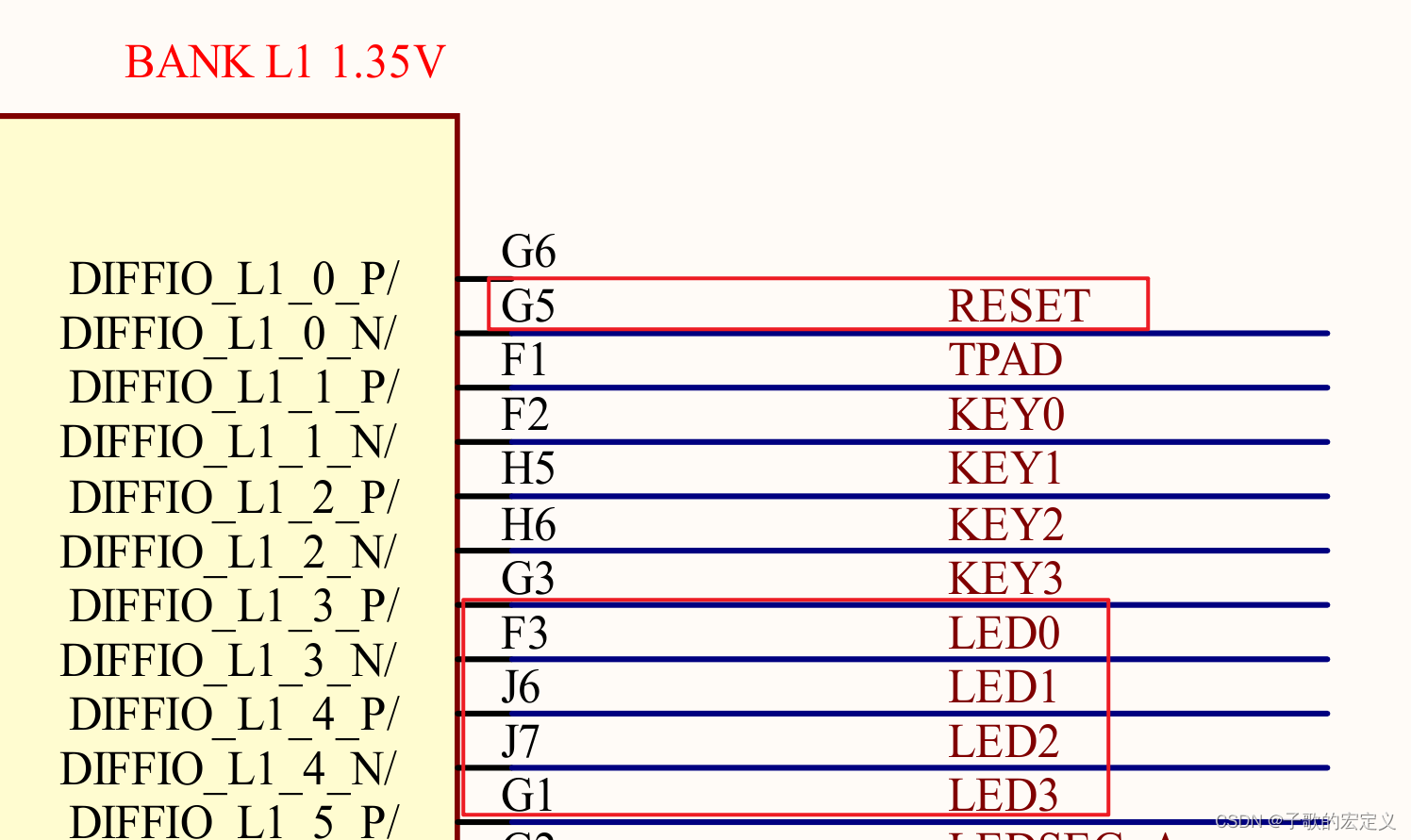

端口对应

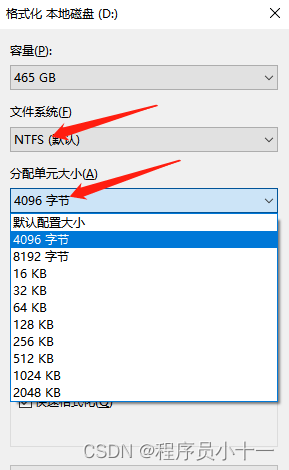

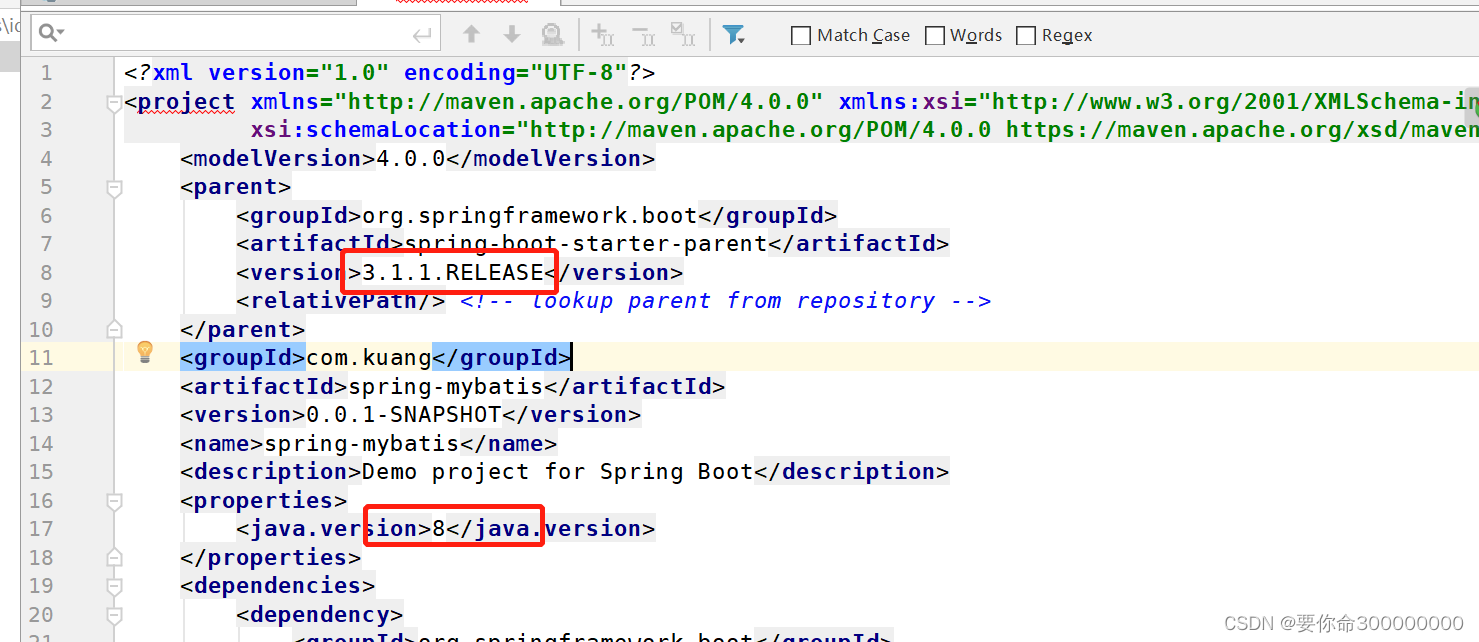

后面管教约束的时候可以用来选择电平和对应的管教,生成fdc文件

平台使用

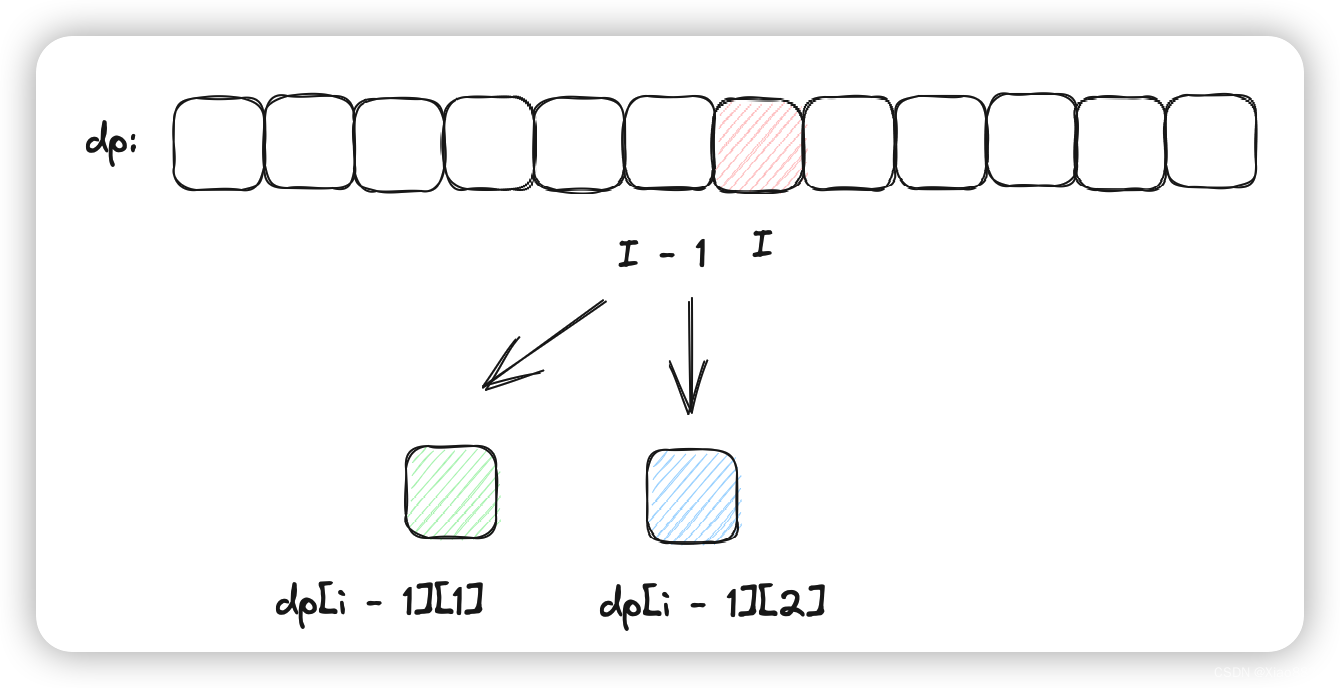

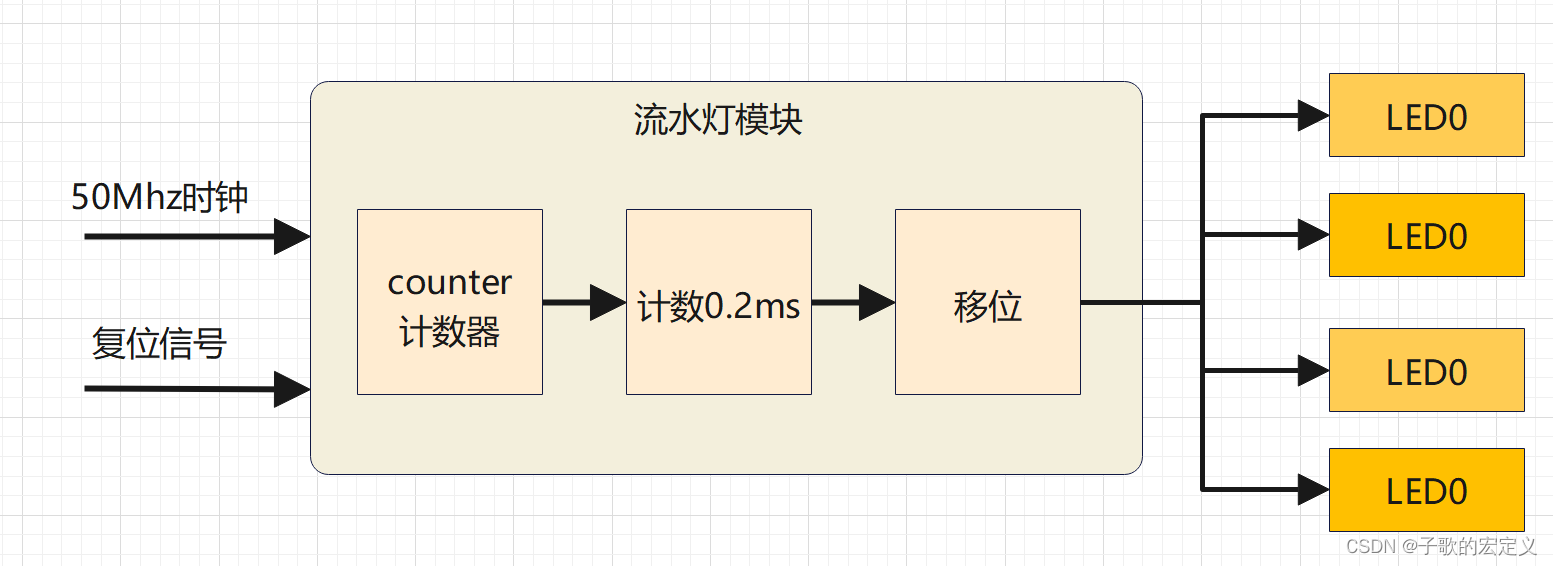

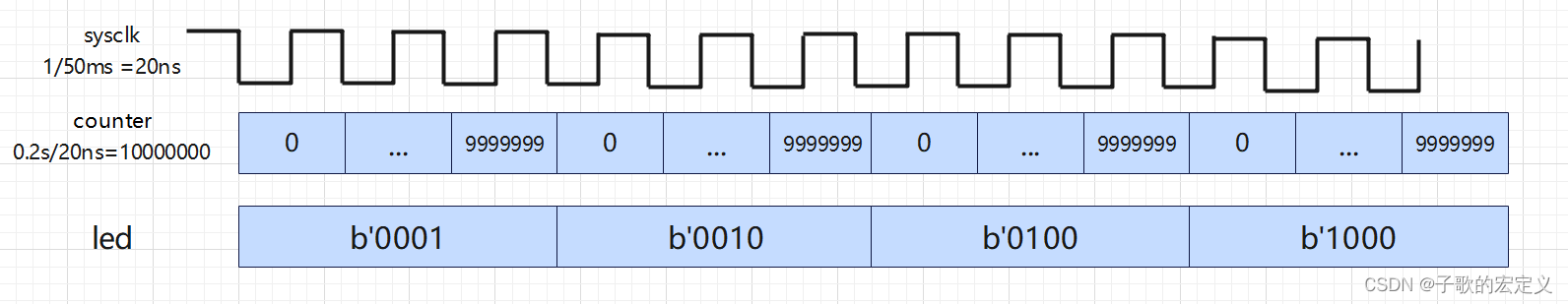

二、程序设计

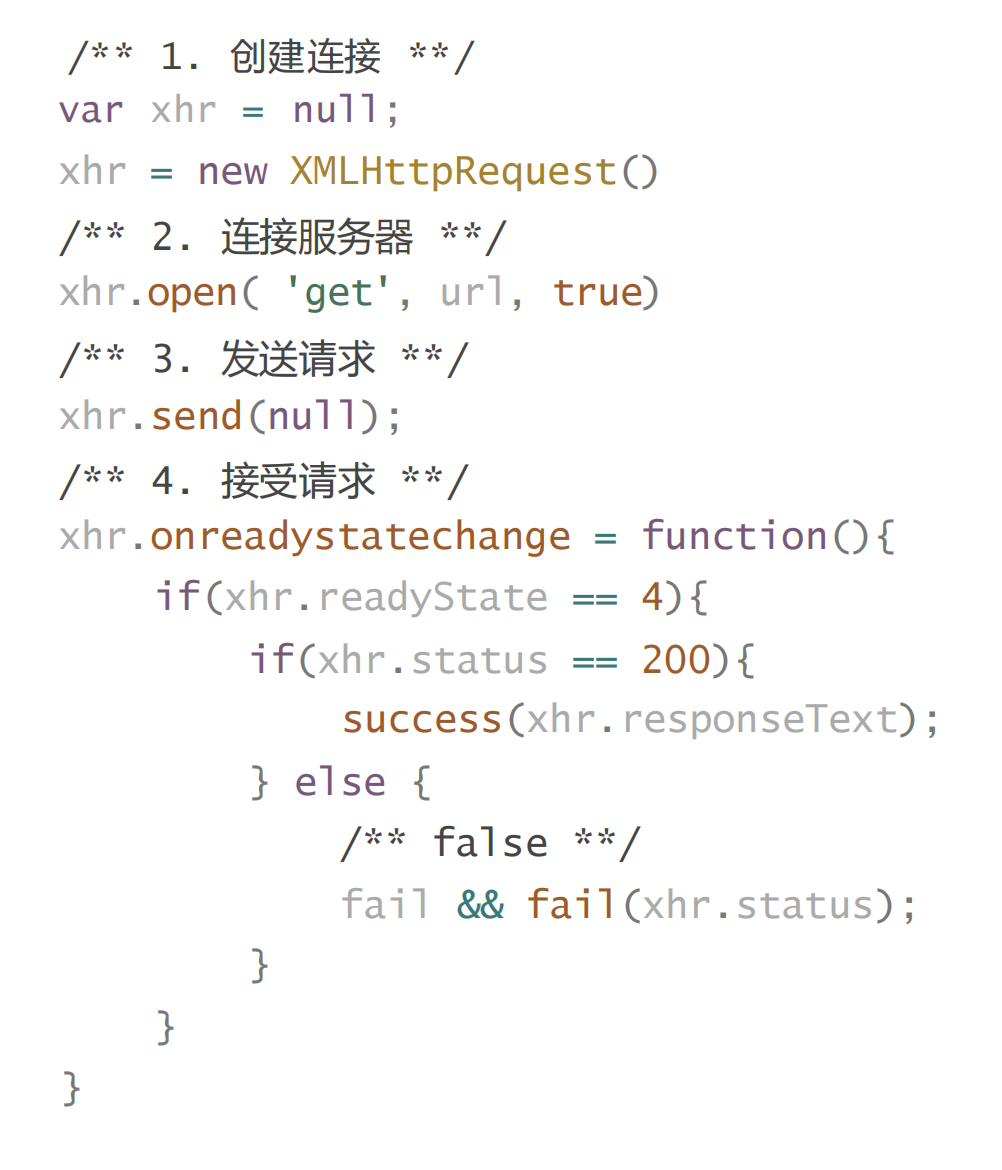

三、程序编写

代码:

module flow_led(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位

output reg [3:0] led

);

reg [23:0] counter;

//时钟上升沿有效,复位信号下降沿有效

always @(posedge sys_clk or negedge sys_rst_n )begin

if (!sys_rst_n)

counter <= 24'd0; //非阻塞赋值,同时赋值

// else if (counter < 24'd1000_0000 - 1'b1)

else if (counter < 24'd10 - 1'b1)

counter <= counter + 1'b1;

else

counter <= 1'd0;

end

always @(posedge sys_clk or negedge sys_rst_n )begin

if (!sys_rst_n)

led <= 4'b0001;

// else if (counter == 24'd1000_0000 - 1'b1)

else if (counter == 24'd10 - 1'b1)

led <= {led[2:0],led[3]};

else

led <= led;

end

endmodule

仿真:

`timescale 1ns/1ns // 仿真单位\仿真精度

module tb_flow_led();

reg sys_clk ;

reg sys_rst_n;

wire [3:0] led ;

initial begin

sys_clk =1'b0;

sys_rst_n =1'b0;

#200

sys_rst_n =1'b1;

end

always #10 sys_clk <= ~sys_clk; //50MHZ

flow_led u_flow_led(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n),

.led (led )

);

endmodule

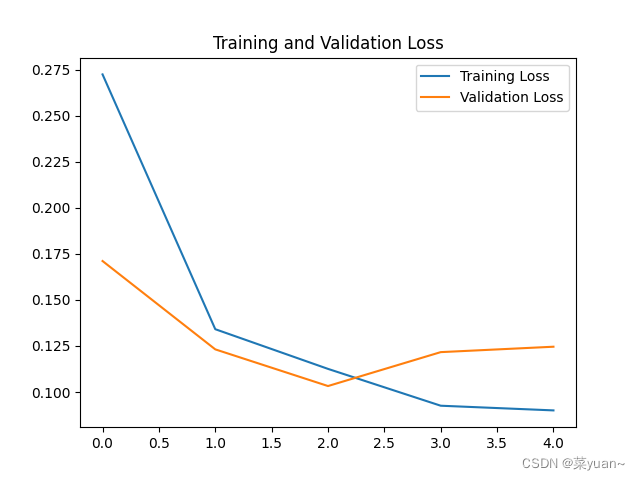

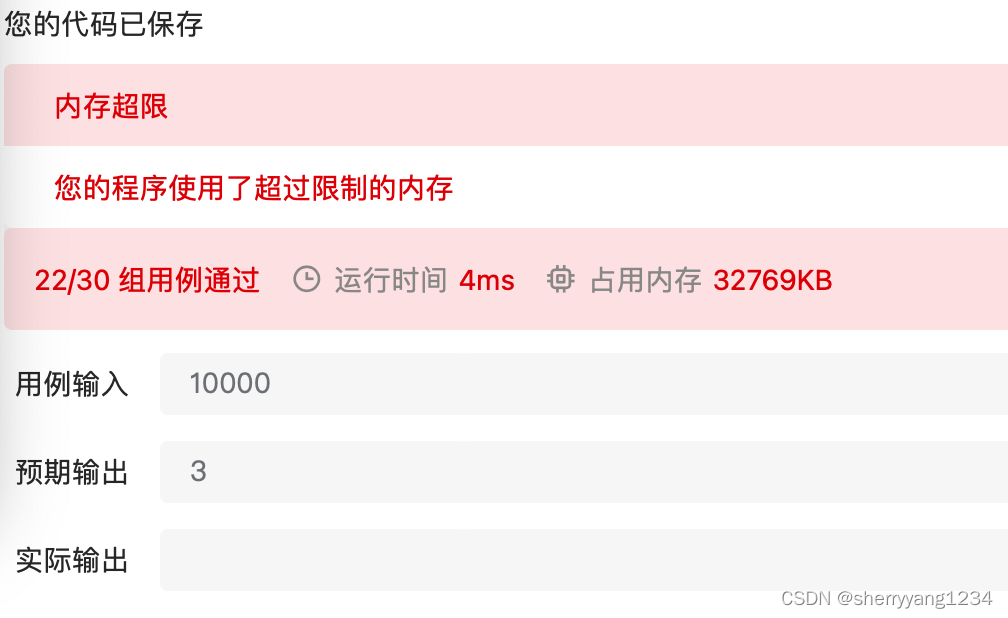

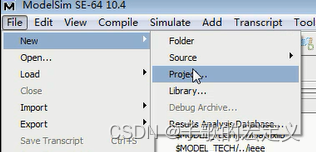

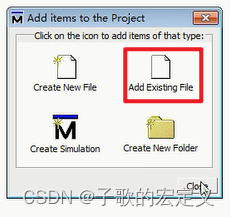

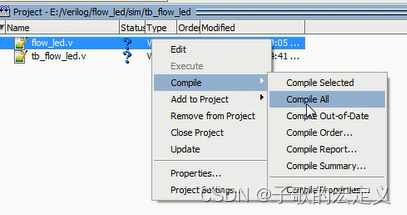

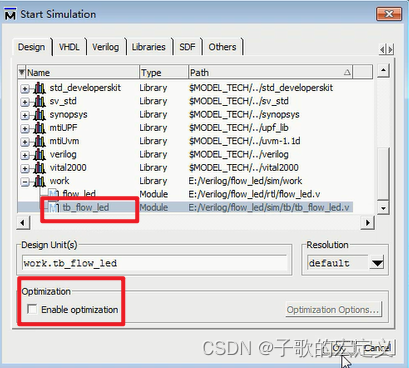

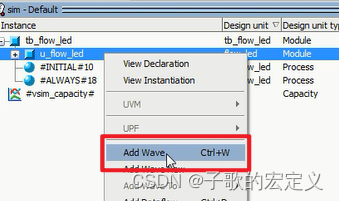

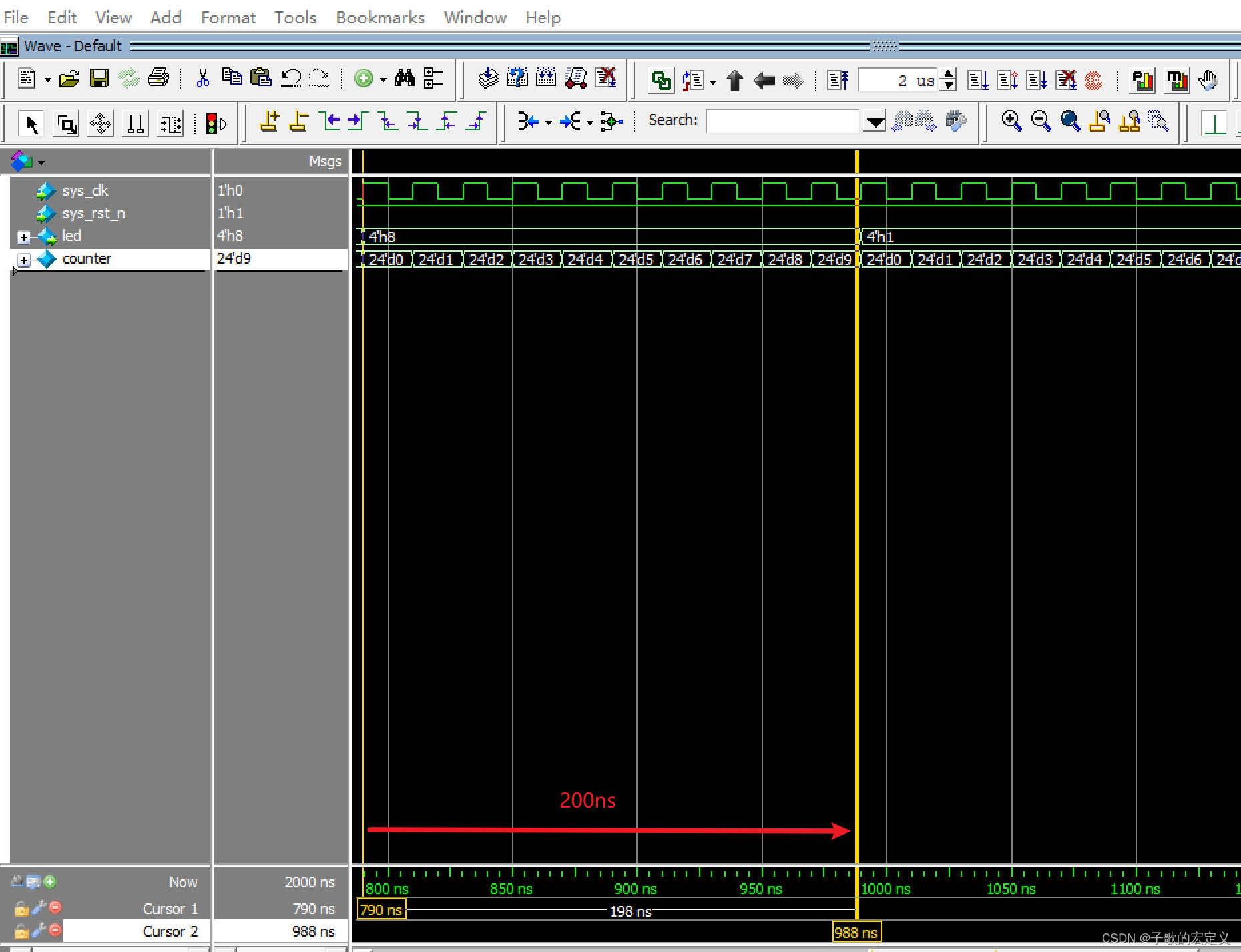

四、仿真

可输入命令或点开始仿真

restart -f

run 2us

200ns,对应i(counter == 24’d10 - 1’b1)

那么

(counter == 24’d1000_0000 - 1’b1)对应200us

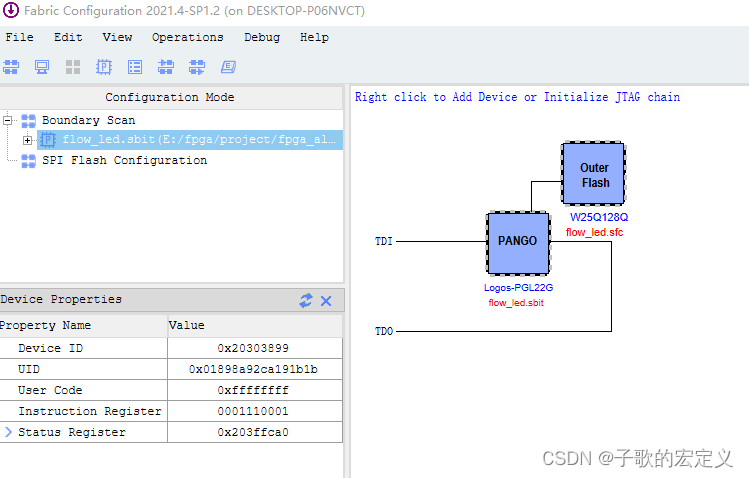

五、工程下载

平台使用

下载后即可看到现象