矩阵乘法的硬件加速

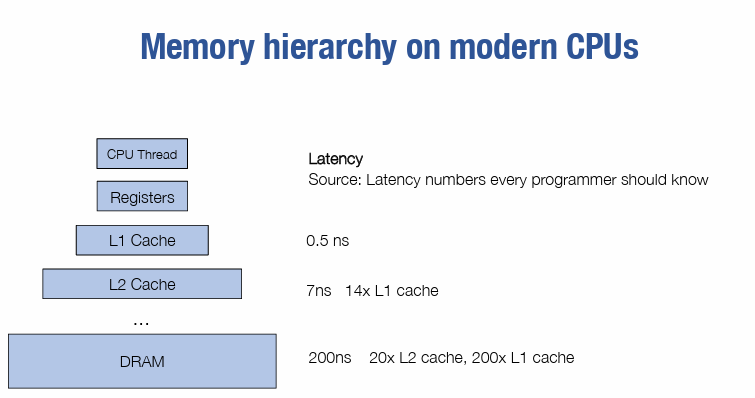

这里的硬件加速是指,如果依靠算法,可以通过减少访存次数来加速。可以将数据预取到cache来减少访存次数。

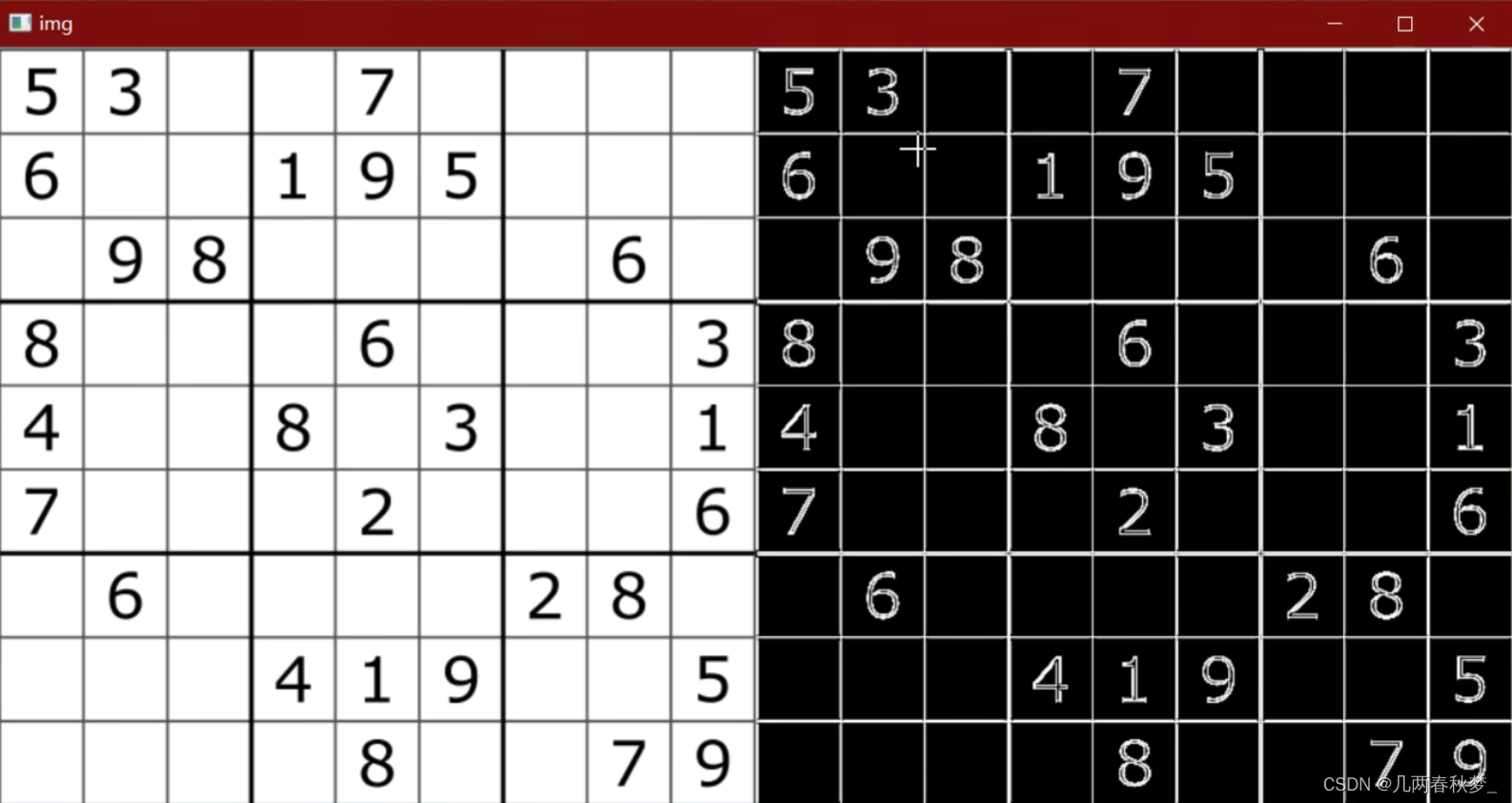

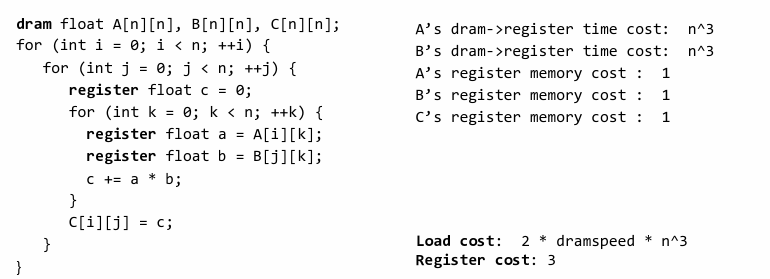

矩阵相乘最简单的实现

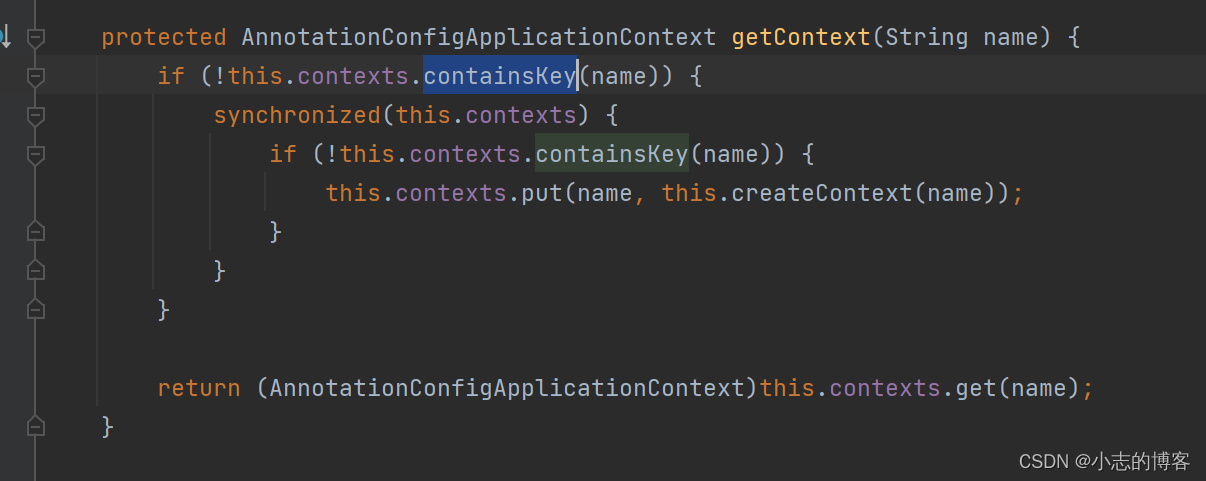

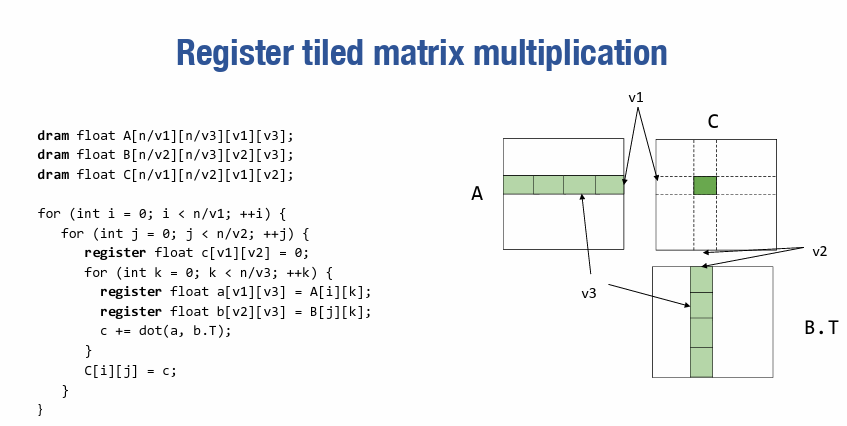

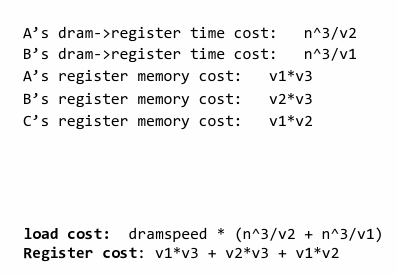

寄存器平铺矩阵乘法

将矩阵划分成多个小的矩阵块,小的矩阵块可以存放在寄存器中,进行小矩阵的乘法时,无需再向内存中取值

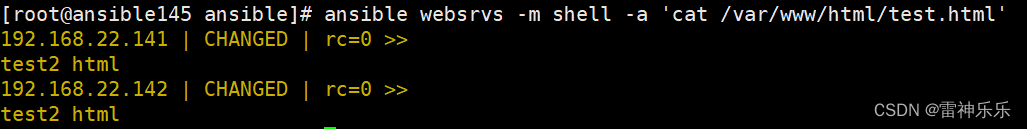

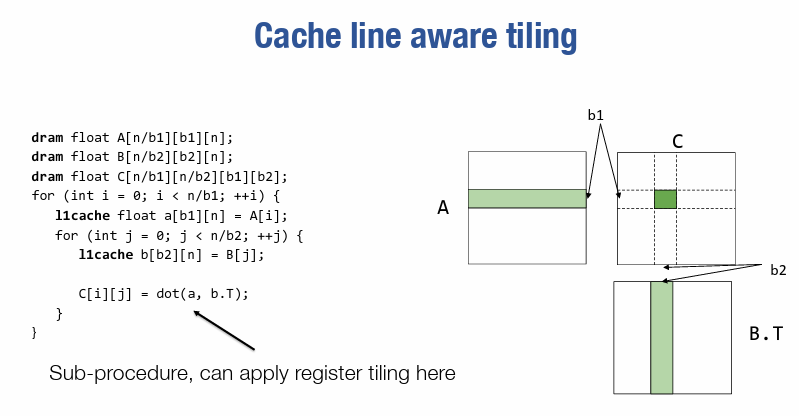

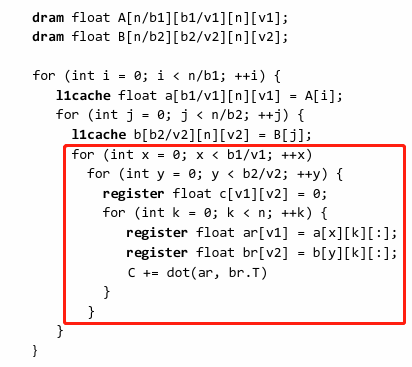

cache 行级别平铺

尽可能将一行或者一列矩阵块读入 l1cache,然后从一行或者一列的cache中读取小的矩阵块到寄存器中进行乘法计算。

下方红框中就是计算 v 1 ∗ v 2 v_1*v_2 v1∗v2 大小的矩阵过程,再将 v 1 ∗ v 2 v_1*v_2 v1∗v2 大小的矩阵拼成 b 1 ∗ b 2 b_1*b_2 b1∗b2 大小

在寄存器分块的例子中,ar被复用了v2次,br被复用了v1次

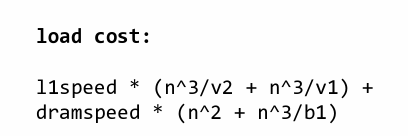

耗时: