文章目录

- 38译码器

- 一、38译码器介绍

- 二、项目代码

- 三、仿真代码

- 四、仿真结果

- 五、总结

38译码器

一、38译码器介绍

38译码器是一种常用的逻辑电路元件,用于将一个3位二进制输入编码转换成8个输出信号之一。它具有多个输入引脚和多个输出引脚。

通常,38译码器有3个输入引脚(A0、A1、A2)和8个输出引脚(Y0、Y1、Y2、Y3、Y4、Y5、Y6、Y7)。输入引脚可以接收二进制编码信号,而输出引脚则对应着相应的解码结果。

对于每一种输入组合,只有一个输出引脚处于高电平状态,其他引脚处于低电平状态。这意味着根据输入来选择其对应的输出,实现了从二进制编码到解码的转换。

二、项目代码

decoder.v

module decoder (

input wire[2:0] a,//3位输入

output wire[7:0] b//8位输出

);

reg[7:0] b_r;

//寄存器类型赋值

always @(*) begin

case(a)

3'b000:b_r = 8'b1111_1110;

3'b001:b_r = 8'b1111_1101;

3'b010:b_r = 8'b1111_1011;

3'b011:b_r = 8'b1111_0111;

3'b100:b_r = 8'b1110_1111;

3'b101:b_r = 8'b1101_1111;

3'b110:b_r = 8'b1011_1111;

3'b111:b_r = 8'b0111_1111;

default :b_r = 8'b0000_0000;

endcase

end

assign b = b_r;

endmodule

三、仿真代码

`timescale 1ns/1ns //单位/精度

module decoder_tb ();

parameter TIME = 20;

reg[2:0] a;

wire[7:0] b;

initial begin

a = 3'b100;

#10

a = 3'b000;

#10

a = 3'b001;

#10

a = 3'b010;

#10

a = 3'b011;

#10

a = 3'b100;

#10

a = 3'b101;

#10

a = 3'b110;

#10

a = 3'b111;

#100;

end

decoder tb(

.a(a),

.b(b)

);

endmodule

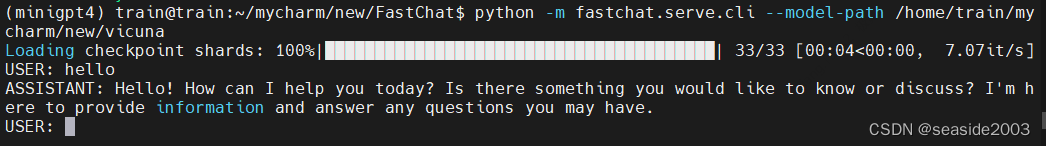

四、仿真结果

五、总结

38译码器是一种将3位二进制编码转换成8个输出信号的逻辑电路元件,广泛应用于数字电路设计和逻辑控制系统中,使用verilog实现38译码器相对于来说比较简单