文章目录

- 前言

- 一、简单并行匹配

- 二、戴维南并行匹配

- 三、主动并行匹配

- 四、串联RC并行匹配

- 五、串联匹配

- 六、差分对匹配

- 七、收发器片内匹配

前言

高速电路阻抗匹配方法

阻抗不匹配会导致信号在传输线上来回反射,使负载接收器出现振铃。振铃降低了接收 器的动态范围,导致错误的触发。为消除反射,源阻抗(ZS)必须等于走线阻抗(Zo),以 及负载阻抗(ZL)。Stratix 器件支持片内电阻匹配。这一部分讨论以下信号匹配方法:

■简单并行匹配

■戴维南并行匹配

■主动并行匹配

■串联 RC 并行匹配

■串联匹配

■差分对匹配

■片内匹配

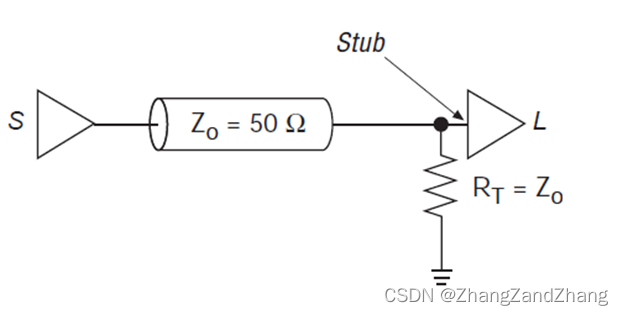

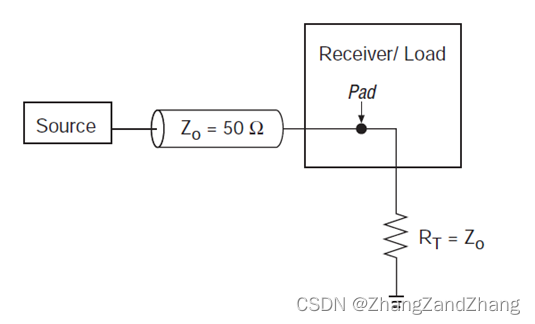

一、简单并行匹配

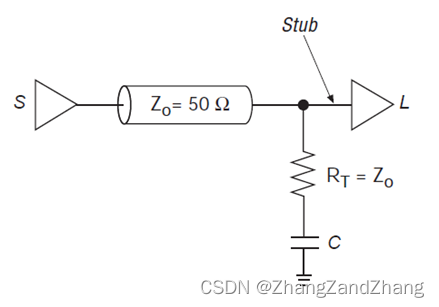

在简单并行匹配方法中,匹配电阻(RT)等于传输线阻抗。匹配电阻尽可能靠近负载放置, 以提高效率。请参考图。

RT 到接收器引脚和焊盘的短截线长度应尽可能短。较长的短截线会带来接收器焊盘反射,导致信号劣化。如果您的设计在匹配终端和接收器之间需要较长的匹配线,那么,电阻的放置会非常重要。对于较长的匹配线,使用飞越匹配。

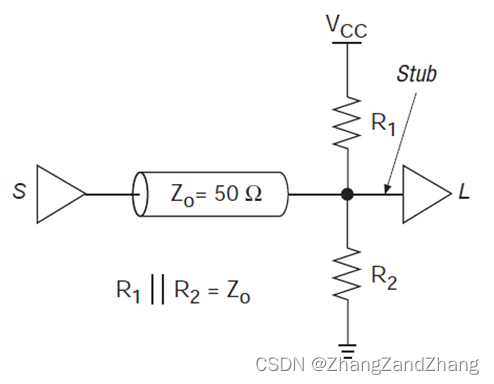

二、戴维南并行匹配

另一并行匹配方法使用戴维南电压分配器。匹配电阻在R1和R2之间分开,两个电阻连起来的阻抗等于传输线阻抗。这一方法虽然降低了源器件的电流吸收,但是,由于电阻连接在VCC和GND之间,因此,增大了电源的电流吸收。

如前所述,短截线长度取决于信号上升和下降时间,应尽可能短。如果您的设计在匹配 终端和接收器之间需要较长的匹配线,那么,使用飞越匹配或者戴维南飞越匹配。请参考图。

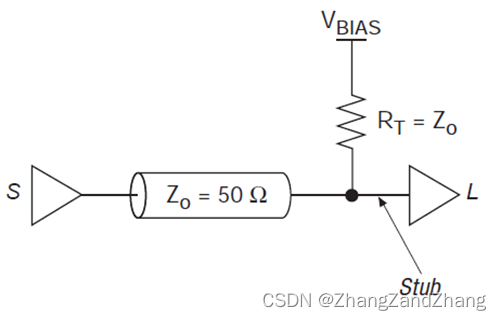

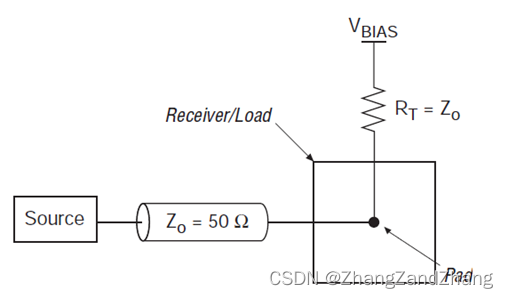

三、主动并行匹配

图显示了主动并行匹配方法,匹配电阻(RT = Zo)连接至偏置电压(VBIAS)。在这一方 法中,选择电压使得输出驱动器能够从高电平和低电平信号吸收电流。但是,这一方法 需要单独的电压源,吸收和源出电流,以匹配输出传递比。

四、串联RC并行匹配

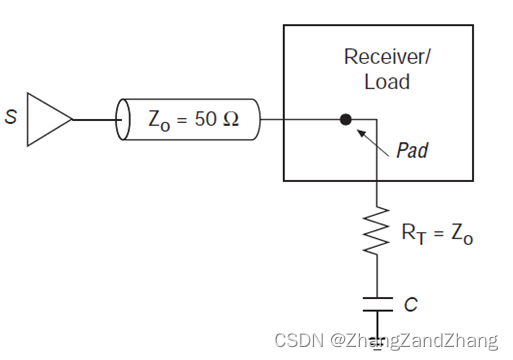

串联RC并行匹配方法使用电阻和电容(即,串联RC)网络作为匹配阻抗。匹配电阻(RT)等于Z0。电容必须足够大,以滤除直流恒流分量。但是,如果电容太大,信号延时会大于设计阈值。

小于100pF的电容会减小匹配效果。电容滤除低频信号,通过高频信号。由于没有连 接至地的直流通路,因此,RT 直流负载效应并不影响驱动器。串联 RC 匹配方法需要平 衡直流信号(例如,信号一半时间接通,一半时间关断)。交流匹配通常用于多个负载的 情况。请参考图。

图显示了串联 RC 并行飞越匹配。

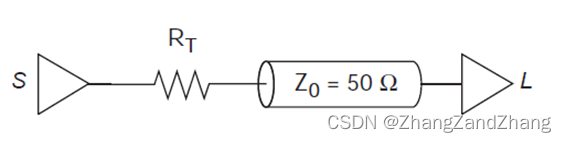

五、串联匹配

在串联匹配方法中,电阻匹配信号源阻抗,而不是每一负载的阻抗。RT和输出驱动阻抗之和应等于 Z0。由于Altera器件输出阻抗较低,因此,您应该增加一个串联电阻以匹配信号源和传输线阻抗。串联匹配的优点在于功耗较低。但是,缺点是RC时间常数较大,劣化了上升时间。因此,对于高速设计,在采用串联匹配方法之前,您应该通过输入/输出缓冲信息规范(IBIS)模型,进行预布板信号完整性仿真。

六、差分对匹配

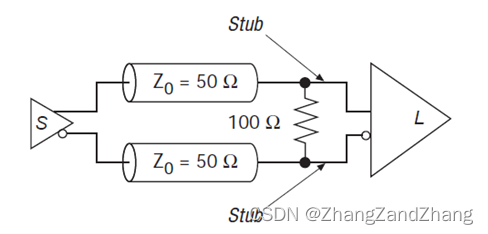

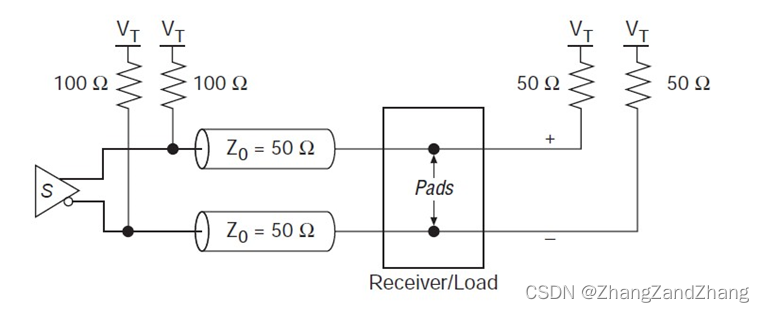

差分信号I/O标准在接收器件信号之间需要一个匹配电阻。对于LVDS和LVPECL标准,匹配电阻应匹配总线的差分负载阻抗(例如,典型值为100Ω)。。使用片内匹配减小了电路板 面积。如果需要了解详细信息。

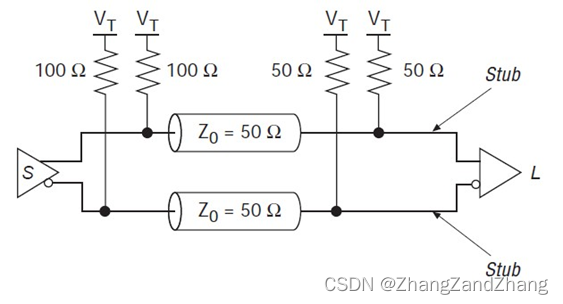

图显示了LVDS和LVPECL标准的差分对飞越匹配方法。

3.3-V PCML 在发射器使用两个并联 100-Ω 匹配电阻,在接收器使用两个并联 50-Ω 匹 配电阻(参见图 33)。匹配电压(VT)与 VCCIO 电压相同(3.3 V)。

图显示了3.3-VPCML的差分对飞越匹配方法。

七、收发器片内匹配

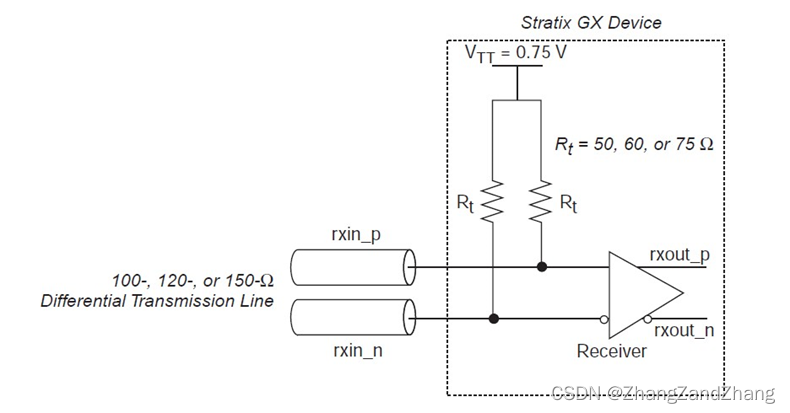

Stratix GX 器件还具有片内电阻,设计支持多种 I/O 标准的匹配。片内电阻释放了电路 板空间,您可以更自由的进行信号布线,从而简化了电路板设计工作。而且,由于电阻 到信号引脚的距离减小了,所以,片内电阻降低了短截线反射。因此,Stratix GX 器件 提供更好的负载和源匹配,从而提高了信号完整性。

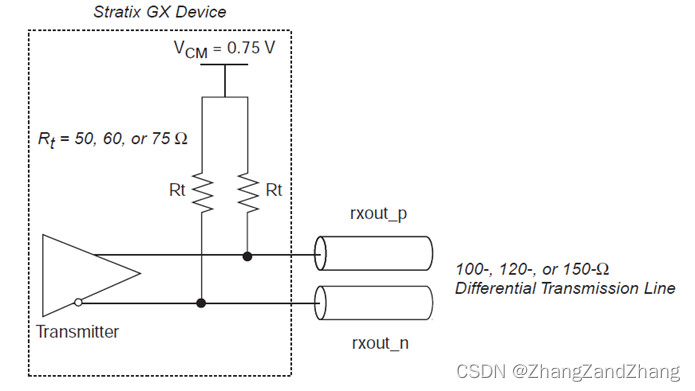

Stratix GX 器件中的所有收发器每个通道都有可设置内部匹配电阻,可以设置为 50、60 或者 75-Ω 单端电阻。在差分模式下,电阻产生 100、120 或者 150-Ω 匹配。图 35 和图 36 显示了 Stratix GX 器件的接收器和发射器片内匹配方法。

不同的 I/O 标准需要不同的匹配电阻,因此,可设置内部匹配电阻会有很大的帮助。例 如,XAUI 和 Infiniband 应用需要 100-Ω 差分匹配,而千兆以太网和光纤通道需要 150-Ω 差分匹配。

您可以旁路接收器中的片内电阻,使用外部电阻。

图Stratix GX 器件发射片内匹配方法

对于 Stratix GX 器件中的非收发器 I/O 引脚,匹配方法与 Stratix 器件的相同。