目录

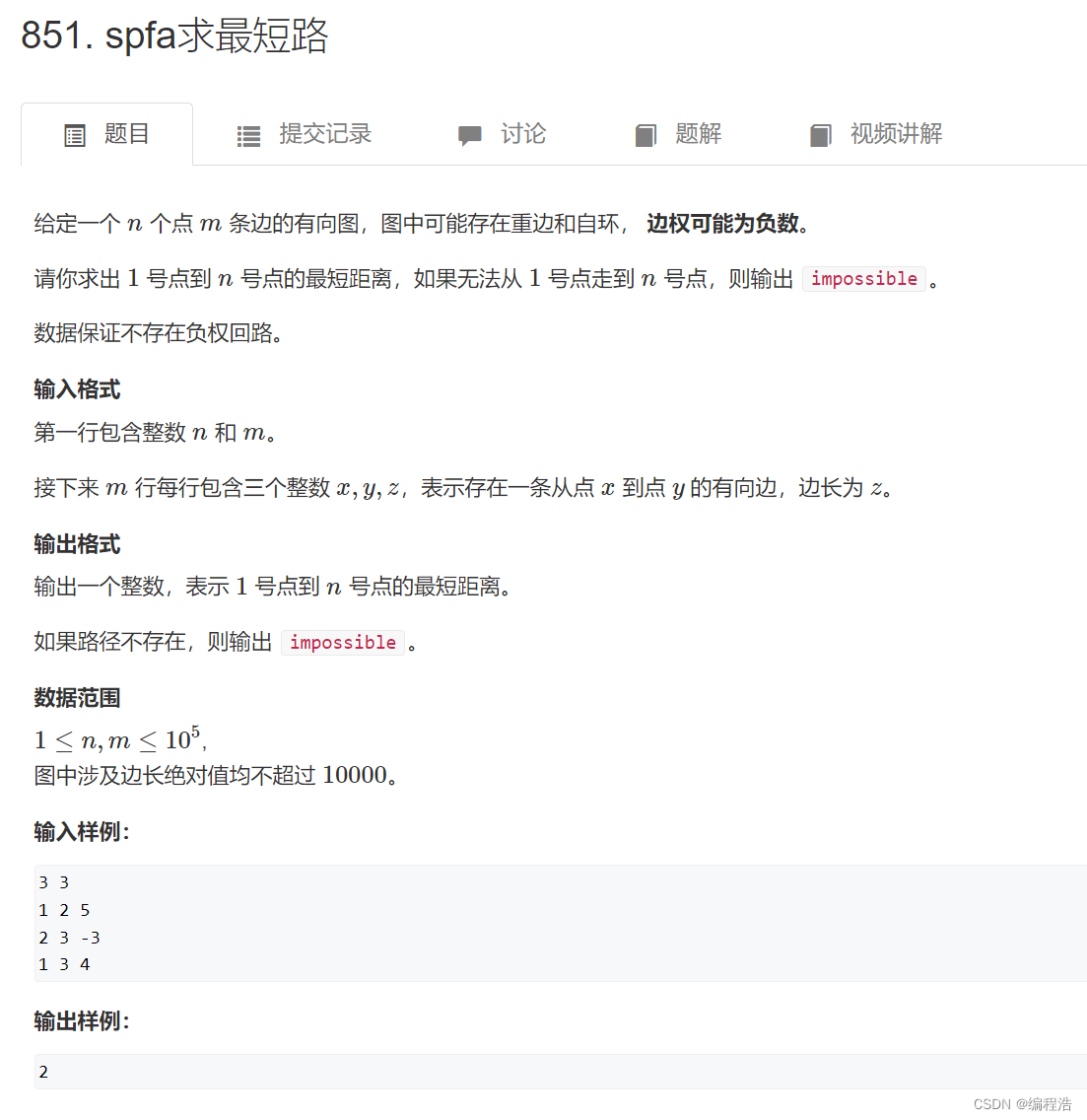

一、问题描述

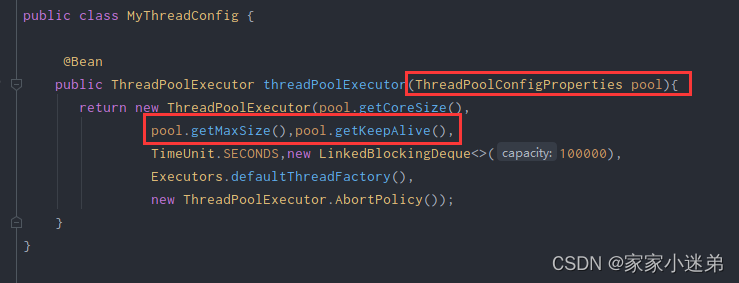

1.1 设计代码

1.2 综合结果

1.3 仿真结果

二、问题原因

三、解决方法

一、问题描述

在使用modelsim进行功能仿真时,会遇到如下情况,仿真结果在前面一段时间内的逻辑输出不符预期,后面的结果符合预期

以实现一个D触发器的逻辑为例

1.1 设计代码

功能简单,为一个异步清零的D触发器

module FF_test(d,ce,clk,clr,fdce );

input d;

input ce;

input clk;

input clr;

output reg fdce;

always@(posedge clk,posedge clr)

begin

if(clr)

fdce<=0;

else

if(ce)

fdce<=d;

else

fdce<=0;

end

endmodule测试代码,根据输入数据d时间点变化将输入进行了两轮的变动,一轮在100ns以前,第二轮在100ns之后

`timescale 1ns / 1ns

module FF_tb();

reg d,ce,clk,clr;

wire out;

initial

begin

clk=0;

d=0;

ce=0;

clr=0;

//第一轮数据变化

#10 clr=1;

#4 clr=0;

#4 ce=1;

#11 d=1;

#10 d=0;

#10 d=1;

//第二轮数据变化

#60 clr=1;

#4 clr=0;

#4 ce=1;

#10 d=1;

#10 d=0;

#10 d=1;

end

//时钟周期2ns

always #1 clk=~clk;

FF_test FF(.d(d),.ce(ce),.clk(clk),.clr(clr),.fdce(out));

endmodule1.2 综合结果

综合为FDCE,符合预期

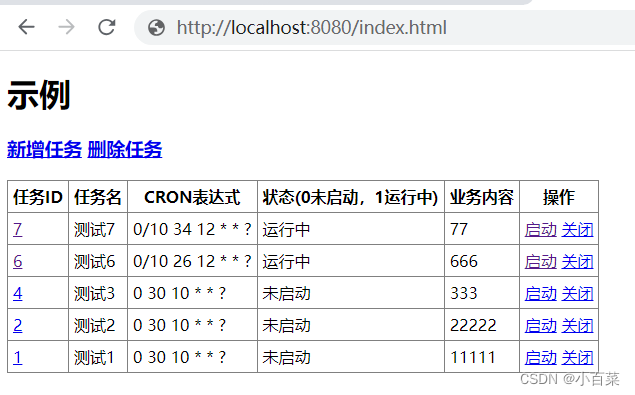

1.3 仿真结果

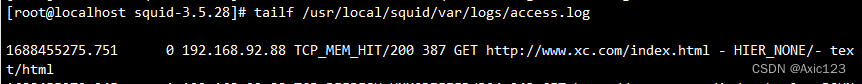

在红框1内,当ce=1,clr=0,输入数据d变化时,输出out一直为0,不符合预期逻辑,红框2内,在输出结果正确,clr为1时清零,输出为0,ce=1,clr=0时,out跟随d变化,符合预期

二、问题原因

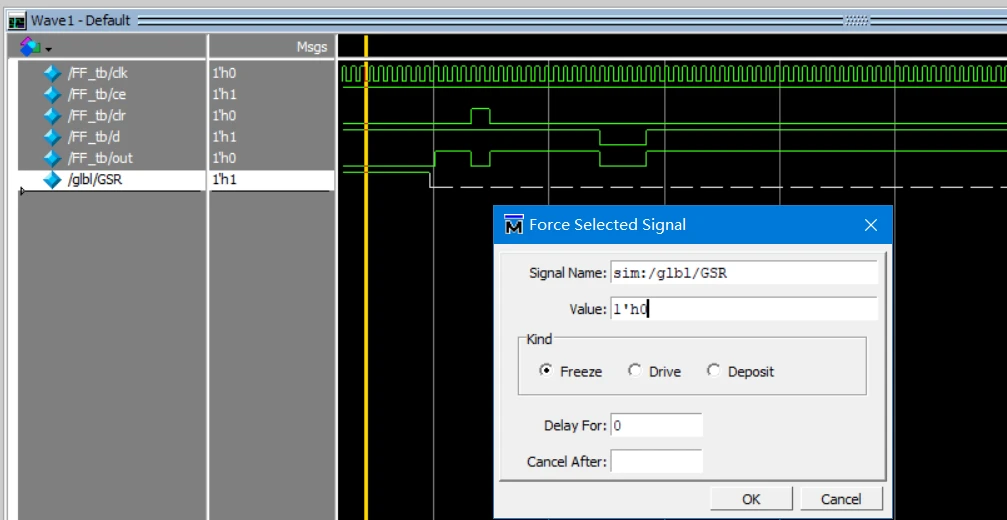

仔细观察会发现,波形中多了一个全局复位信号GSR,在设计中是未体现的,该信号在100ns时进行了从1到0 的切换,切换之后,输出逻辑符合预期。

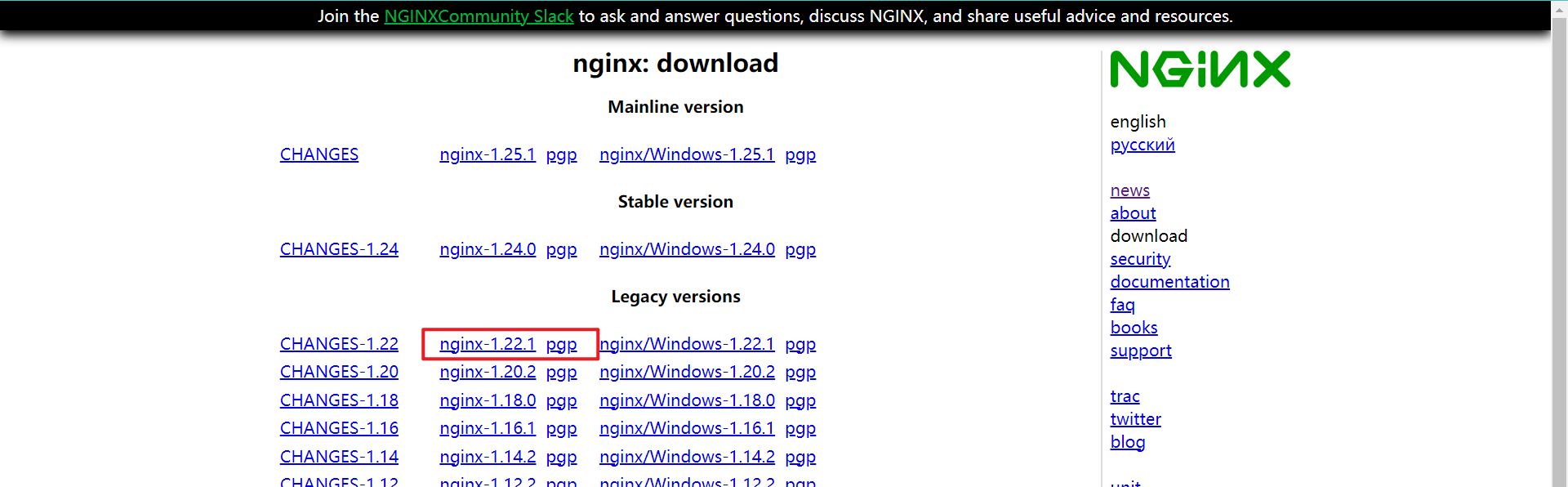

100ns来自何处?测试文件中未有设置,信号列表中选中该信号,点击鼠标右键,进入“Object Declaration”查看其来源。

GSR信号来源于FF_tb_func_impl.v文件的glbl模块,如下图,在125行定义了GSR信号,129行的initial模块中对GSR_int进行了赋值,初始值为1,等待ROC_WIDTH=100000(100ns)后状态变为0,符合前面的现象。

三、解决方法

比较容易想到的办法是直接修改FF_tb_func_impl.v中initial模块,但该模块是仿真前生成的,修改重新运行会被覆盖。此时可借用modelsim的force功能,将GSR信号强制置为0再运行。

操作:选中GSR信号,鼠标右键,执行restart将原有结果删除。

再选中GSR信号,选择“Force”,弹出下图弹框“Force Selected Signal”,在Value中将值改为1'h0,OK进行保存。

再将默认运行100ps修改为300ns,即运行300ns,最后执行run。如下图,GSR一直为低电平0,所以前100ns的结果也符合预期

![火车头小发猫AI伪原创[php源码]](https://img-blog.csdnimg.cn/6b0790b51d7f4bf192da2d3e2ff6f57a.png)