目录

一、实验目的

二、设计要求

三、实验代码

1.代码原理分析

2.代码设计思路

3.IP核的设计与配置

四、实验结果及分析

1、引脚锁定

2、仿真波形及分析

(1)关于波形一些指标的介绍

(2)对波形转换功能的验证

(3)对幅度调节功能的验证------三角波幅度的变化

(4)对调频功能的验证---以三角波频率的变化为例

3、下载测试结果及分析

五、实验心得

一、实验目的

(1)掌握信号发生器的原理;

(2)学习复杂数字系统设计;

(3)学习用IP核进行设计;

(4)学习用在线逻辑分析仪观察FPGA产生的信号。

二、设计要求

(1)数字化波形数据存在ROM中,ROM用IP核进行设计;

(2)正弦波或方波、锯齿波波形可选并数码管显示所选波形种类;

(3)信号频率、幅度可调并用数码管显示频率和幅值;

(4)连接开发板,用在线观察信号的幅度、频率调制波形;

(5)可采用DDS原理产生正弦信号。

三、实验代码

限于篇幅,此处仅给出顶层文件代码

-

module TOP( input clk, input rst_n, input [1:0] wave, //input [11:0] p_word, input [2:0] AM, input [3:0] f_set, //output [11:0] dac_dataa, output[10:0] count_display//数码管输出 ); wire [31:0] f_word; wire [4:0] amplitude; wire [11:0] dac_dataa; wire [1:0] cnt_1; wire [6:0] cnt_2; wire [2:0] cnt_3; wire [31:0] fre; // 分频: reg[26:0] clk_cnt; reg [2:0] sel=4'b0; reg clk1; //reg [10:0] count_display=11'b1111_1111111; always @(posedge clk) begin clk_cnt=clk_cnt+1; if(clk_cnt==100000000) begin clk_cnt=0; clk1=1'b1; end else clk1=1'b0; if(clk_cnt%100000==0) begin sel=sel+1; if(sel==4) sel=0; end end DDS uut1( .clk(clk), .rst_n(rst_n), .wave(wave), .f_word(f_word), //.p_word(p_word), .amplitude(amplitude), .dac_dataa(dac_dataa), .cnt_1(cnt_1) ); F_word_set uut2( .clk(clk), .rst_n(rst_n), .f_set(f_set), .f_word(f_word), .fre(fre), .cnt_2(cnt_2) ); A_set uut3( .clk(clk), .rst_n(rst_n), .AM(AM), .amplitude(amplitude), .cnt_3(cnt_3) ); display SG_display( .clk (clk), .rst (rst_n), .counter_1 (cnt_1), .counter_2 (cnt_2), .counter_3 (cnt_3), .count_display (count_display), .sel(sel) ); ila_0 ila ( .clk(clk), // input wire clk .probe0(dac_dataa), // input wire [11:0] probe0 .probe1(wave), // input wire [1:0] probe1 .probe2(AM), // input wire [2:0] probe2 .probe3(f_set) // input wire [3:0] probe3 ); endmodule1.代码原理分析

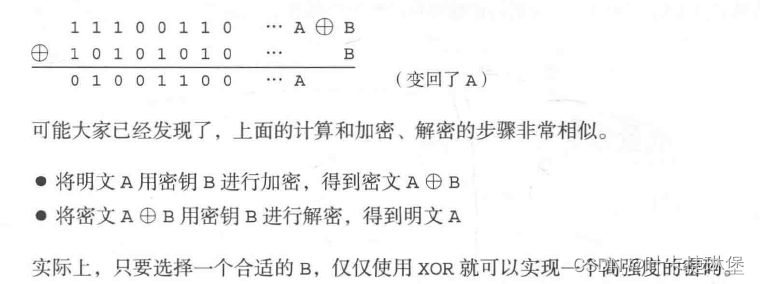

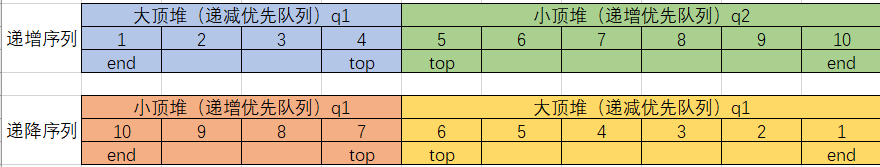

正弦信号发生器由计数器或地址发生器(6位)、正弦信号数据 ROM(6位地址线,8位数据线,含有 64 个 8 位数据,一个周期)、原理图顶层设计和 8 位D/A。其框图如图 1 所示。其中信号产生模块将产生所需的各种信号,这些信号的产生可以有多种方式,如用计数器直接产生信号输出,或者用计数器产生存储器的地址,在存储器中存放信号输出的数据。信号发生器的控制模块可以用数据选择器实现。将波形数据送入 D/A 转换器,将数字信号转换为模拟信号输出。

2.代码设计思路

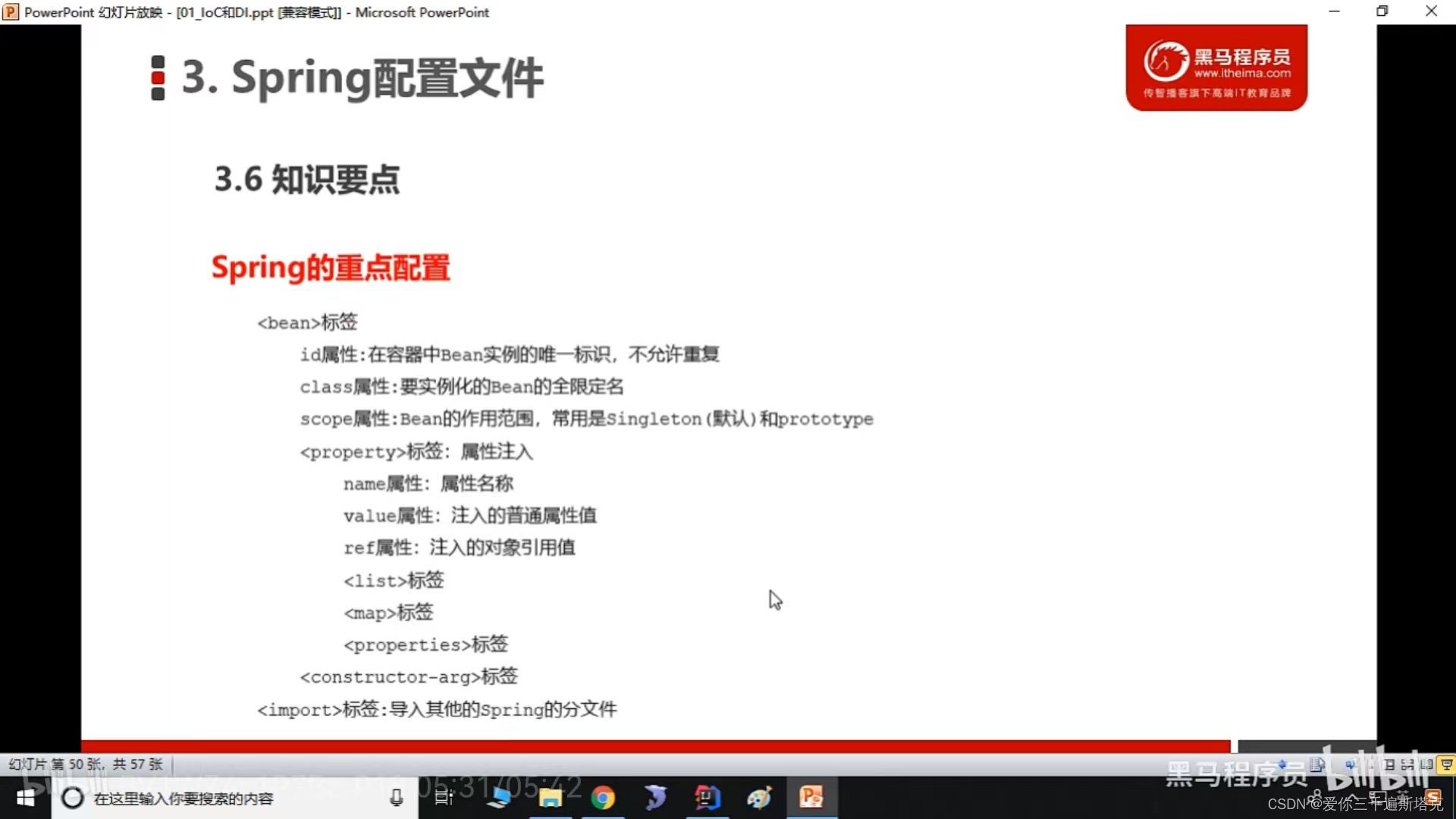

3.IP核的设计与配置

(以ila_0为例)

在线逻辑分析仪的配置

此处设置了5个探针,在逻辑分析仪中显示出频率、幅度、波形类型额变化。

四、实验结果及分析

1、引脚锁定

set_property -dict { PACKAGE_PIN W5 IOSTANDARD LVCMOS33 } [get_ports clk]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

## Switches

set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports {wave[0]}]

set_property -dict { PACKAGE_PIN V16 IOSTANDARD LVCMOS33 } [get_ports {wave[1]}]

set_property -dict { PACKAGE_PIN W16 IOSTANDARD LVCMOS33 } [get_ports {f_set[0]}]

set_property -dict { PACKAGE_PIN W17 IOSTANDARD LVCMOS33 } [get_ports {f_set[1]}]

set_property -dict { PACKAGE_PIN W15 IOSTANDARD LVCMOS33 } [get_ports {f_set[2]}]

set_property -dict { PACKAGE_PIN V15 IOSTANDARD LVCMOS33 } [get_ports {f_set[3]}]

set_property -dict { PACKAGE_PIN W14 IOSTANDARD LVCMOS33 } [get_ports {AM[0]}]

set_property -dict { PACKAGE_PIN W13 IOSTANDARD LVCMOS33 } [get_ports {AM[1]}]

set_property -dict { PACKAGE_PIN V2 IOSTANDARD LVCMOS33 } [get_ports {AM[2]}]

set_property -dict { PACKAGE_PIN R2 IOSTANDARD LVCMOS33 } [get_ports {rst_n}]

##7 Segment Display

set_property -dict { PACKAGE_PIN W7 IOSTANDARD LVCMOS33 } [get_ports {count_display[6]}]

set_property -dict { PACKAGE_PIN W6 IOSTANDARD LVCMOS33 } [get_ports {count_display[5]}]

set_property -dict { PACKAGE_PIN U8 IOSTANDARD LVCMOS33 } [get_ports {count_display[4]}]

set_property -dict { PACKAGE_PIN V8 IOSTANDARD LVCMOS33 } [get_ports {count_display[3]}]

set_property -dict { PACKAGE_PIN U5 IOSTANDARD LVCMOS33 } [get_ports {count_display[2]}]

set_property -dict { PACKAGE_PIN V5 IOSTANDARD LVCMOS33 } [get_ports {count_display[1]}]

set_property -dict { PACKAGE_PIN U7 IOSTANDARD LVCMOS33 } [get_ports {count_display[0]}]

#set_property -dict { PACKAGE_PIN V7 IOSTANDARD LVCMOS33 } [get_ports dp]

set_property -dict { PACKAGE_PIN U2 IOSTANDARD LVCMOS33 } [get_ports {count_display[7]}]

set_property -dict { PACKAGE_PIN U4 IOSTANDARD LVCMOS33 } [get_ports {count_display[8]}]

set_property -dict { PACKAGE_PIN V4 IOSTANDARD LVCMOS33 } [get_ports {count_display[9]}]

set_property -dict { PACKAGE_PIN W4 IOSTANDARD LVCMOS33 } [get_ports {count_display[10]}]

2、仿真波形及分析

(1)关于波形一些指标的介绍

rst_n:表示使能端 clk:表示时钟周期 wave:波形类型0-正弦波 1-矩形波 2-三角波 3-锯齿波

AM:波形幅度 f_set:波形频率

(2)对波形转换功能的验证

I:波形类型的变化:从正弦波到矩形波 II:从矩形波到锯齿波的变化

III :从锯齿波到三角波的变化

(3)对幅度调节功能的验证------三角波幅度的变化

(4)对调频功能的验证---以三角波频率的变化为例

分析:

当信号的类型、频率、幅度发生变化时,具体的波形也会立即出现明显的变化,实现了频率、幅度、波形类型的可调性。

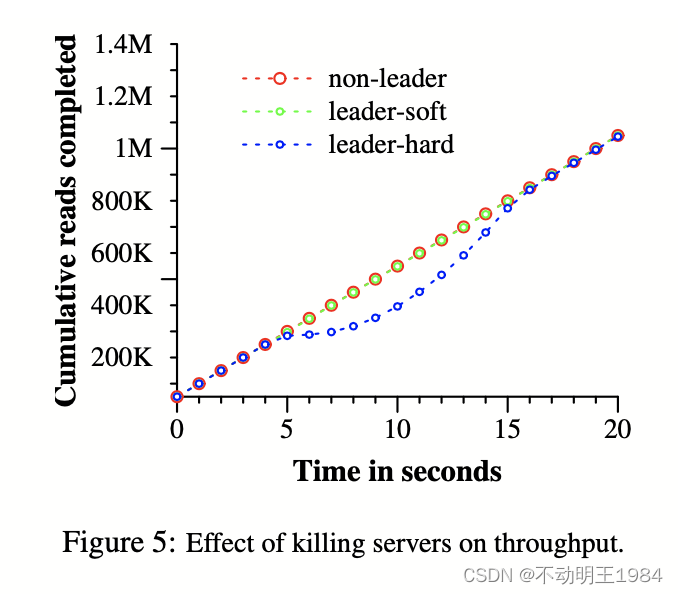

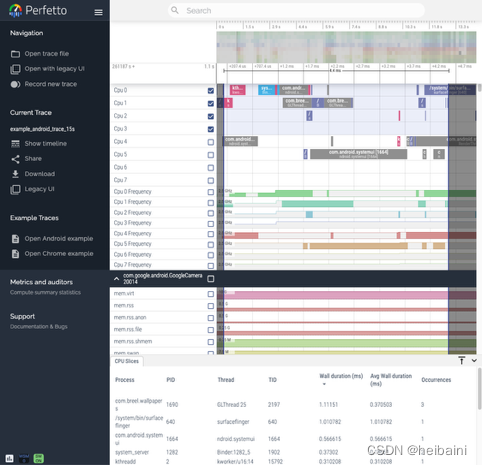

3、下载测试结果及分析

包含在线逻辑分析仪情况及开发板情况

波形类型:0-正弦波 1-矩形波 2-三角波 3-锯齿波

不断改变波形类型、幅度及频率

- 锯齿波

幅度:3 频率:12 波形类型:3 开发板

(2)正弦波

幅度:4 频率:8 波形类型:0 开发板

(3)矩形波

幅度:1 频率:7 波形类型:1 开发板

(4)三角波

幅度:2 频率:10 波形类型:2 开发板

五、实验心得

1.实验过程中在完成仿真实验后准备上开发板进行测试,但发现此次实验与之前的实验上板子有点不一样。在查阅相关资料后,才知道此次实物实验不能仅依靠bassy3开发板,还需要使用在线逻辑分析仪观察FPGA产生的信号,实现波形的显示,展示其频率、幅度及波形类型,这让我对实物实验有了不一样的认识。

2.最初实验刚开始的时候真的是一头雾水,实验要求用IP核进行设计虽然有一定的思路,但也不清楚到底如何下手,最后还是参考了网上的方法程序,一点点理解下来。当然,网上的内容和我们的实验有许多出入,所以还是要在理解之后进行诸多修改。像“数字化波形数据存在ROM中,ROM用IP核进行设计”这类步骤,如果不是参考网上的教程,我得花很多时间去消化理解,虽然是借着别人的经验前进,但我认为只要最后能消化吸收转化为自己的知识,也是能够被理解的。经过这次实验,我真的是收获良多,如理解了信号发生器的设计原理、学会了使用DDS原理产生正弦信号。特别是对ip核设计的理解,这也给我在今后对于verilog编程也提供了更多的选择,也能为我之后的实验提供不少帮助。

2022-05-05