文章目录

- 1.1 ARM Coresight 介绍

- 1.1.1 ARM Coresight 发展历史

- 1.2 ARM Coresight 框架介绍

- 1.1.1 Trace 通路

- 1.1.3 Debug 通路

- 1.1.4 Trigger 通路

1.1 ARM Coresight 介绍

ARM Coresight是ARM公司提供的一种调试和跟踪技术,用于ARM处理器的调试和性能分析。它通过在处理器内部集成一组硬件组件,提供了对处理器内部状态和执行信息的可观察性。

Coresight技术包括多个组件,如调试接口、调试逻辑和跟踪组件等。调试接口提供了与处理器进行通信的接口,用于调试器与处理器之间的数据交换。调试逻辑是一组硬件逻辑,用于控制和管理调试操作。跟踪组件用于收集处理器的执行信息,包括指令执行、数据访问和事件触发等。

ARM Coresight技术可以帮助开发人员进行软件调试和性能分析。通过使用Coresight技术,开发人员可以实时监测处理器的内部状态和执行信息,以便快速定位和解决软件问题。此外,Coresight技术还可以提供性能分析功能,帮助开发人员优化软件性能并提高系统效率。

1.1.1 ARM Coresight 发展历史

ARM Coresight的发展始于ARMv6架构时期,当时的Coresight技术主要用于处理器的调试和跟踪。随着ARM架构的不断演进,Coresight技术也得到了进一步的发展和改进。

在ARMv7架构时期,Coresight技术引入了更多的功能和组件,如Coresight Debug Access Port (DAP)、Coresight Trace Port (ETM)和Coresight Trace Funnel (ETF)等。这些组件提供了更强大的调试和跟踪能力,使开发人员能够更好地监测和分析处理器的内部执行信息。

随着ARMv8架构的引入,Coresight技术也得到了进一步的创新和改进。ARMv8架构引入了新的调试和跟踪扩展,如Coresight Trace Memory Controller (TMC)和Coresight Embedded Trace Router (ETR)等。这些扩展提供了更高级的跟踪和调试功能,使开发人员能够更好地理解和优化软件的执行性能。

1.2 ARM Coresight 框架介绍

Coresight Framework

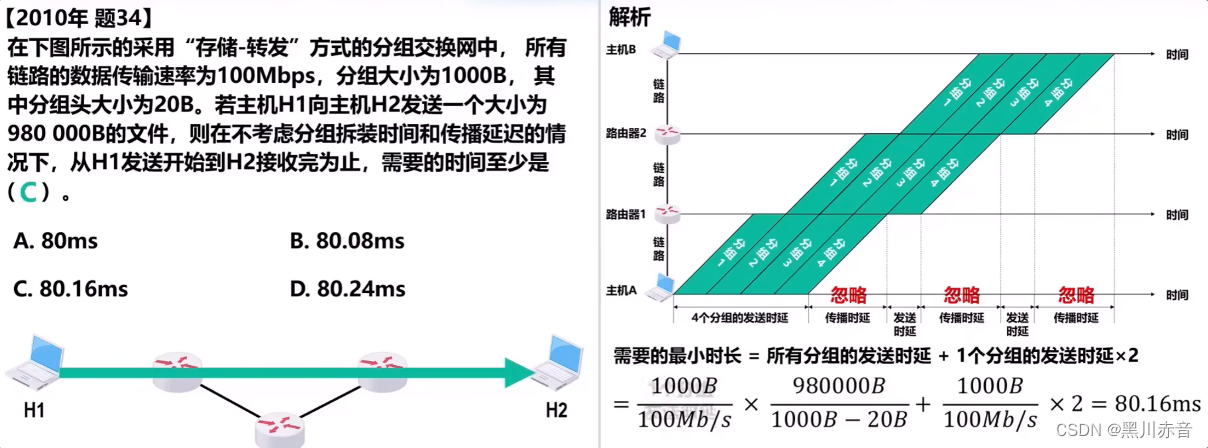

下图是 DGI0012D_coresight_dk_sdg.pdf 中的一个典型的 Coresight 环境,其包含了两个 ARM Core,和一个 DSP(Digital Signal Processing,简称DSP),和众多的 Coresight 组件。

用这些 Coresight 组件实现对 ARM Core 及 DSP 的 Debug 和 Trace功能(包含 Instruction Trace 和 Data Trace)。

Coresight 图 1-1

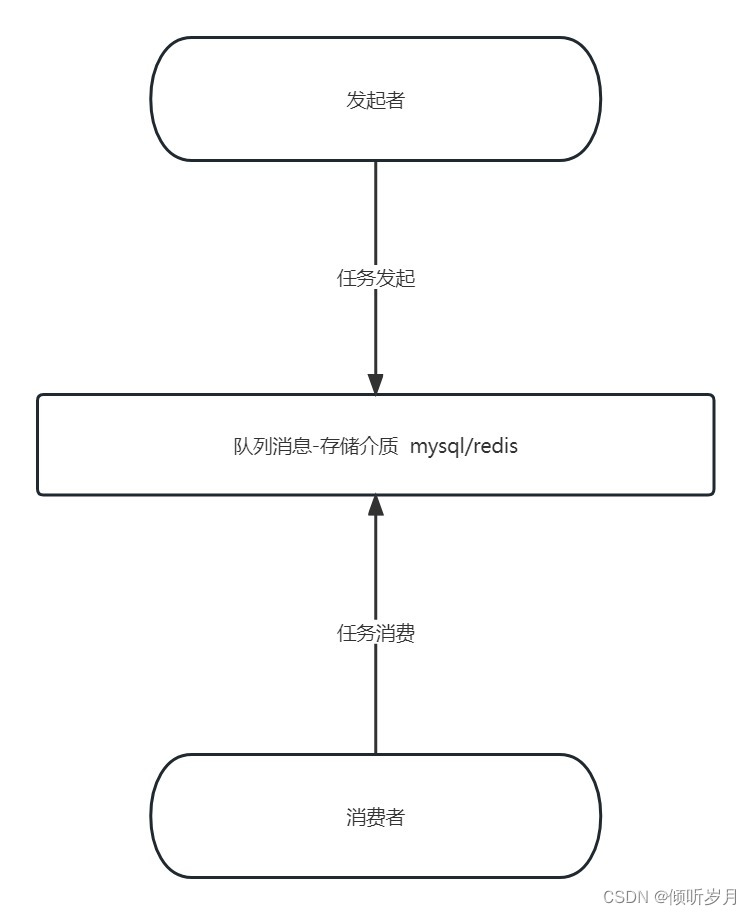

上图的环境中总共包括 3 个通路

- Trace 通路: 将 Core 和 DSP 内部信息输出到外部;

- Debug 通路:对 Core 和 DSP 实现 debug;

- Trigger 通路: 用于 Core 和 Core 之间,Core 和 DSP 之间,传输 trigger 信号。

1.1.1 Trace 通路

Trace 通路 实现对 Master 组件的数据追踪功能,使用 ETM(嵌入式跟踪宏单元) 来追踪。

ETM 负责追踪 处理器 和 DSP 的信息,将信息打包,通过 ATB 总线发送到 trace bus上。trace bus上有 Trace Funnel(聚合器),Funnel 接收多个 ATB 总线数据,然后合并成一个 ATB 总线数据,发送给 Replicator(分发器)。

Replicator 接收到 ATB 数据,根据配置,将 ATB 数据发送给 ETB(片上缓冲区) 和 TPIU。

Coresight 图 1-2

1.1.3 Debug 通路

Debug 通路 用于外部的 debugger,对 ARM core 和 DSP 进行调试功能。

图 1-1 中只考虑了 JTAG 的 Port。其实还有 SWO 的 Port。

DAP 接收外部端口的 JTAG 数据,然后转化成对 DAP 内部的 AP 的访问,然后 AP 再转化为 memory-mapped 的总线访问,去访问 SoC 内部的资源。

ARM Coresight SWO(Serial Wire Output)是一种用于调试和跟踪的串行通信协议。它通过串行线路将调试信息从目标设备传输到调试器或其他外部设备。SWO协议可以在ARM处理器系统中使用,并且可以与其他Coresight组件(如DWT和ITM)一起工作。

图 1-1 中,DAP 输出两个 Memory-Mapped 总线:

- 一个是 Debug APB 总线,连接到 Debug APB 互联上,用于访问 Debug 组件的寄存器;

- 一个是 System Bus,连接到 Bus matrix,用于访问 SoC 的内部的资源。

Memory-Mapped 总线是一种常见的总线协议,用于连接 ARM 处理器系统中的各种外设和存储器。它基于内存映射的概念,将外设和存储器映射到处理器的地址空间中。

Debug APB 互联,连接了有CTI,ETM,HTM,ITM,ETB,TPIU 等 Coresight 组件,因此外部的 Debugger 可以通过JTAG Port,对这些 Coresight 组件进行访问。

Bus Matrix 一般是连接 SoC 的一些外设,如 memory,串口等,因此外部的 Debugger(J-link/DS-5) 可以通过 JTAG port 对这些外设设备进行访问。

1.1.4 Trigger 通路

Trigger 通路 用于给指定的组件发送 trigger 信号,或者接收指定的组件的 trigger 信号。这个功能由 CTI 和 CTM 来实现。每个 core 和 DSP 都有一个 CTI 组件相连,CTI 可以给处理器(DSP)发送 trigger 信号,也可以接收处理器(DSP)的 trigger 信号。

所有的 CTI 和 CTM 相连,因此可以实现多个 CTI 之间的 trigger 信号的相互发送与接收。

上一篇:ARM Coresight 及 DS-5 介绍 1 - ARM DS-5介绍

下一篇:ARM Coresight 及 DS-5 介绍 2.1 - ARM Coresight 组件介绍