目录

一、实验目的

二、设计要求

三、实验代码

1.顶层文件代码

2.仿真文件部分代码

3.系统工程文件

四、实验结果及分析

1、引脚锁定

2、仿真波形及分析

3、下载测试结果及分析

五、实验心得

一、实验目的

(1)掌握通信信号调制过程及实现原理;

(2)了解设计中的优化方案;

(3)进一步学习复杂数字系统设计;

(4)培养工程思维及创新思维。

二、设计要求

(1)实现单路PWM 信号模块,可通过端口设置初始相位,频率,占空比;

(2)通过模块调用方法,实现三路PWM信号输出,分辨展示相位,频率,占空比可调;

(3)加入正弦波形VTH(t)实现SPWM波形;

三、实验代码

1.顶层文件代码

限于篇幅,此处仅给出顶层代码

-

`timescale 1ns / 1ps module PWM1( input clk, //systerm clock 50MHz input rst_n, input fclock,//频率设置信号 input xclock ,//相位设置信号 input zclock,//占空比设置信号 input[1:0]f, input[1:0]x, input[1:0]z, output pwm1, output pwm2, output pwm3, output pwm4, //output [7:0]CNT2, //output [7:0]CNT2, //output [7:0]CNT3, //output [7:0]CNT4 output [9:0]dataout ); wire [7:0]CNT1; wire[7:0]CNT2; wire [7:0]CNT3; wire [7:0]CNT4; //wire [9:0]dataout; reg [19:0]count=0; reg [30:0]count2=0; reg [2:0] sel=0; parameter T1MS=50000; //仿真 //wire clk1; //assign clk1=clk; //板子 reg clk1; always @(posedge clk) begin count2=count2+1; if(count2/100000%2==1) begin clk1=1'b1; count2=0;end else clk1=1'b0; end //频率变换 pwm_gen U1(.clk(clk),.rst_n(rst_n),.fclock(fclock),.xclock(0),.zclock(0),.f(f),.x(x),.z(z),.pwm(pwm1),.CNT(CNT1)); //相位变换 pwm_gen U2(.clk(clk),.rst_n(rst_n),.fclock(0),.xclock(xclock),.zclock(0),.f(f),.x(x),.z(z),.pwm(pwm2),.CNT(CNT2)); //占空比变换 pwmz U3(.clk(clk),.rst_n(rst_n),.fclock(0),.xclock(0),.zclock(zclock),.f(f),.x(x),.z(z),.pwm(pwm3),.CNT(CNT3)); //SPWM SPWM U4(.clk(clk),.rst_n(rst_n),.fclock(0),.xclock(0),.zclock(0),.f(0),.z(0),.x(0),.pwm(pwm4),.CNT(CNT4),.dataout(dataout)); ila_0 U5 ( .clk(clk), // input wire clk .probe0(pwm1), // input wire [0:0] probe0 .probe1(pwm2), // input wire [0:0] probe1 .probe2(pwm3), // input wire [0:0] probe2 .probe3(pwm4), // input wire [0:0] probe3 .probe4(dataout) ); endmodule2.仿真文件部分代码

module gen_PWMTB( ); reg clk; reg rst_n; reg fclock; reg xclock; reg zclock; reg [1:0]f; reg [1:0]x; reg [1:0]z; wire pwm1; wire pwm2; wire pwm3; wire pwm4; //wire [7:0] CNT1; //wire [7:0] CNT2; //wire [7:0] CNT3; wire [7:0] CNT4; wire [9:0]dataout; initial begin rst_n=0; clk=0; fclock=0; xclock=0; zclock=0; f<=2'd0; x<=2'd0; z<=2'd0; #2; rst_n=1; #2200; fclock<=1; f<=2'd1; xclock<=1; x<=2'd1; zclock<=1; z<=2'd1; # end always #10 clk=~clk; PWM1 U0(clk,rst_n,fclock,xclock,zclock,f,x,z,pwm1,pwm2,pwm3,pwm4,CNT4,dataout); endmodule

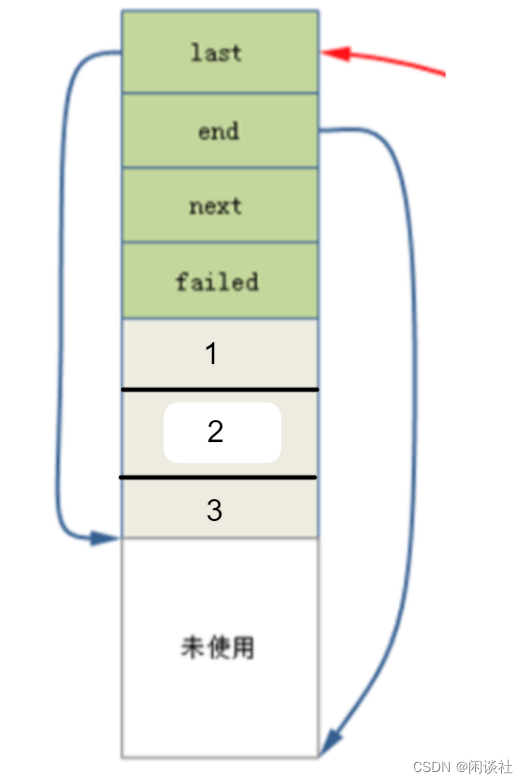

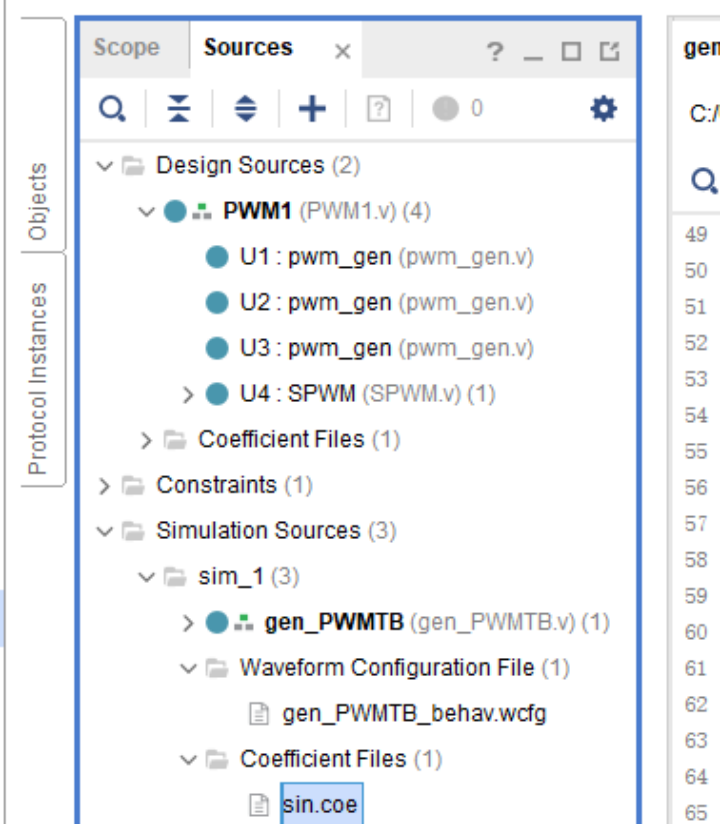

3.系统工程文件

四、实验结果及分析

1、引脚锁定

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets fclock]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets xclock]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets zclock]

set_property PACKAGE_PIN W5 [get_ports clk]

set_property PACKAGE_PIN U16 [get_ports {dataout[0]}]

set_property PACKAGE_PIN E19 [get_ports {dataout[1]}]

set_property PACKAGE_PIN U19 [get_ports {dataout[2]}]

set_property PACKAGE_PIN V19 [get_ports {dataout[3]}]

set_property PACKAGE_PIN W18 [get_ports {dataout[4]}]

set_property PACKAGE_PIN U15 [get_ports {dataout[5]}]

set_property PACKAGE_PIN U14 [get_ports {dataout[6]}]

set_property PACKAGE_PIN V14 [get_ports {dataout[7]}]

set_property PACKAGE_PIN V13 [get_ports {dataout[8]}]

set_property PACKAGE_PIN V3 [get_ports {dataout[9]}]

set_property PACKAGE_PIN V17 [get_ports {f[0]}]

set_property PACKAGE_PIN V16 [get_ports {f[1]}]

set_property PACKAGE_PIN W16 [get_ports fclock]

set_property PACKAGE_PIN L1 [get_ports pwm1]

set_property PACKAGE_PIN P1 [get_ports pwm2]

set_property PACKAGE_PIN N3 [get_ports pwm3]

set_property PACKAGE_PIN P3 [get_ports pwm4]

set_property PACKAGE_PIN R2 [get_ports rst_n]

set_property PACKAGE_PIN W17 [get_ports {x[0]}]

set_property PACKAGE_PIN W15 [get_ports {x[1]}]

set_property PACKAGE_PIN V15 [get_ports xclock]

set_property PACKAGE_PIN W14 [get_ports {z[0]}]

set_property PACKAGE_PIN W13 [get_ports {z[1]}]

set_property PACKAGE_PIN V2 [get_ports zclock]

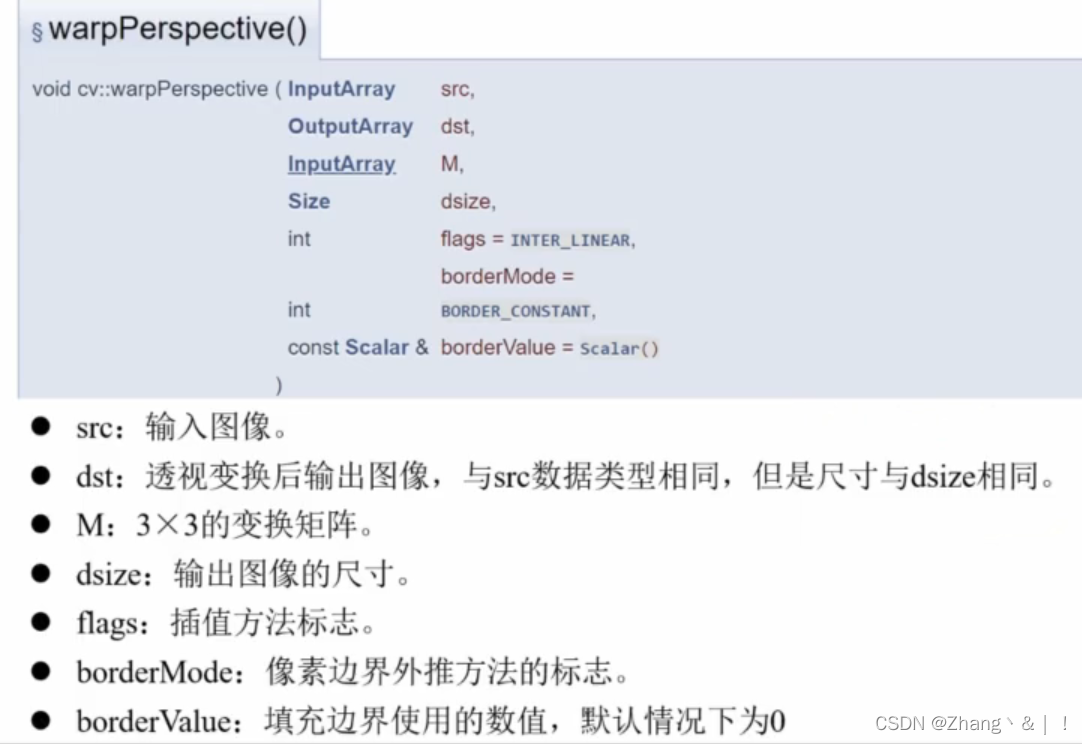

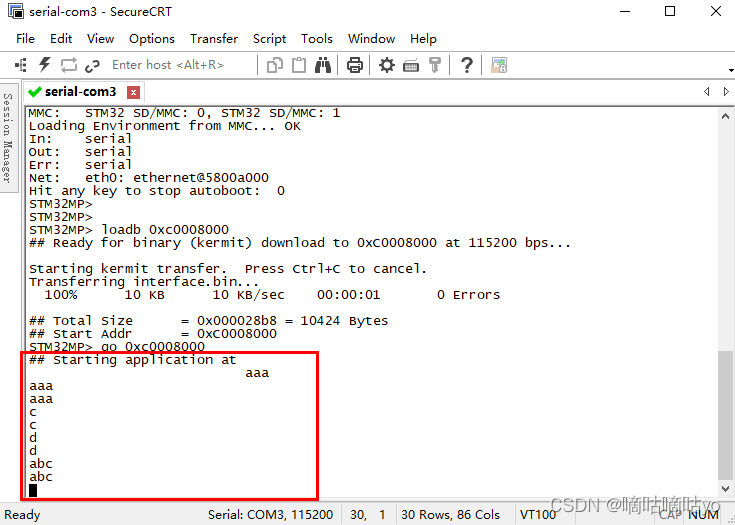

2、仿真波形及分析

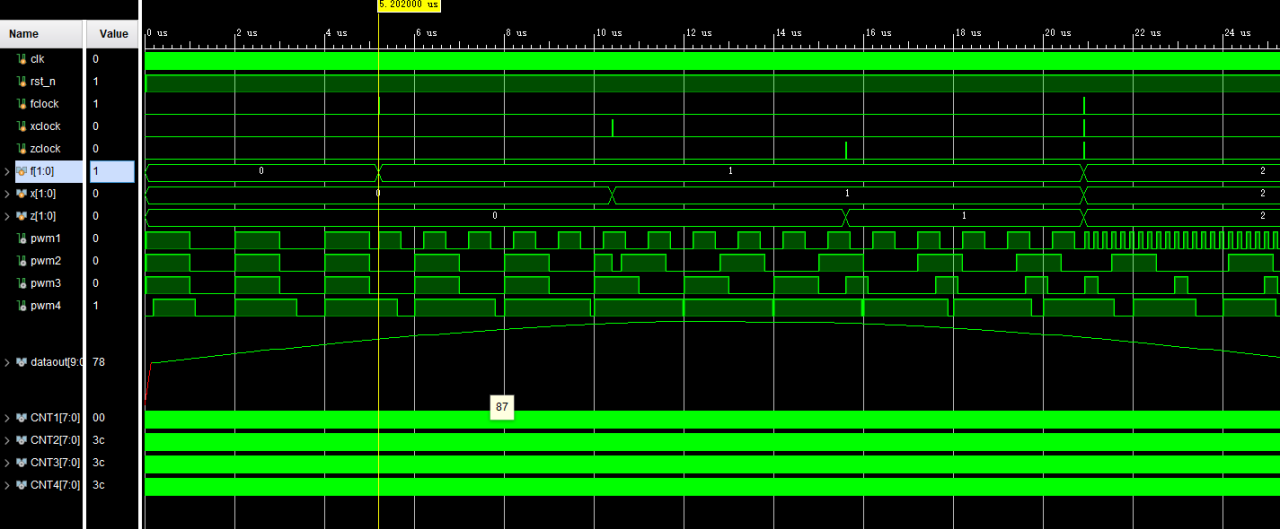

波形如下

Pwm1表示pwm信号的频率

Pwm1表示pwm信号的相位

Pwm3表示pwm信号的占空比

(1)可观察到在信号频率不变的情况下,相位的单独变化与占空比的对应变化

(2)可观察到在信号相位不变的情况下,频率的单独变化与占空比的对应变化

(3)SPWM功能验证

如图实现了一个完整的周期,且输出波形的占空比随 sin 波形变化。

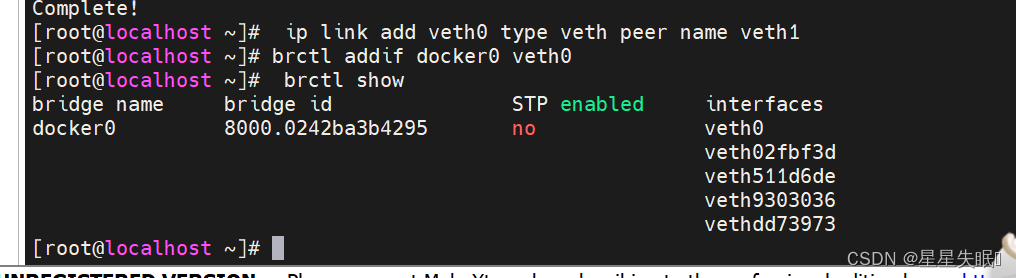

3、下载测试结果及分析

开发板情况如下:

在使能端有效的情况下,用在线逻辑分析仪观察FPGA产生的信号导入后,可观察到波形

两种不同比例的波形均可显示出信号频率、相位、占空比的可调。

五、实验心得

本次实验着实很难,令人头疼,但好在最终也验收完成。因为前几个实验虽然分了模块,但事实上都可以在一个文件中运行仿真,这次实验我本来也是下意识地想在一个文件里编完程序,但实行起来却很困难,因为不同路有不同的点要照顾到。而且实验要求是通过模块调用法,实现多路PWM 信号发生器,所以我这种写法肯定是错误的,这也意味着我又要去学习新的内容,比如如何调用其它文件的内容,如何更好地设计顶层文件。不过总还是差了那么一点点。其实老师的要求随课程的推进要更详细、更多了一些,这也说明设计时要更注重细节。在本次实验的进行之初,我连理顺实验要求都略显困难,到实验验收结束,我也能讲出如何编写如何操作以及各文件之间的联系和运用了。我感受到了自己的进步。希望在大作业的设计和推进过程中能学到更多东西,取得更大的进步!也希望本次PWM信号调制器的设计能为综合设计打下坚实的基础!

2023-05-25