目录

一、实验目的

二、实验要求

三、实验代码

四、实验结果及分析

1、引脚锁定

2、仿真波形及分析

3、下载测试结果及分析

五、实验心得

一、实验目的

(1)掌握基本组合逻辑电路的 FPGA实现;

(2)学习 Verilog HDL 的多层次设计方法;

(3)熟练应用 开发软件 进行 FPGA开发。

二、实验要求

以4位二进制全加器为例:

(1)先用Verilog HDL文本实现一位全加器,通过调用一位全加器完成4位全加器的设计,熟悉层次设计概念;

(2)给出此项设计的仿真波形;

(3)下载到开发板上,用LED发光管指示显示结果。

三、实验代码

1.首先对代码设计的实验原理分析

层次法电路设计通常是在设计比较复杂的电路和系统时采用的一种自上而

下的电路设计方法,即首先在一张图纸上设计电路总体框图,然后再在另外层次

图纸上设计每个框图代表的子电路结构,下一层次中还可以包括框图,按层次关

系将子电路框图逐级细分,直到最低层次上为具体电路图,不再包括子电路框图。

层次法设计电路的优点有:

(1)分工。将一个复杂的电路设计分为几个部分同时进行设计。

(2)模块化。让具有不同特长的设计人员负责不同部分的设计。

(3) 设备限制。打印输出设备不支持幅面过大的电路图页面。

(4)自上而下的设计策略。目前该策略已成为电路和系统设计的主流。

全加器是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全

加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进

行级联可以得到多位全加器。

- 具体的实验代码分析

(1)创建一个新的工程,并新建一个 verilog 文本文件,编写一位全加器代码。模

块名命名为“add”,一位全加器代码如下:

-

module add(input a ,input b, input ci,output sum,output count); assign sum=(a^b)^ci; assign count=(a&b)|(b&ci)|(a&ci); end module

(2)在同一文件夹下创建 4 位全加器工程,即通过顶层调用一位全加器完成4位全加器的设计

`timescale 1ns / 1ps

module adder(a,b,ci,sum,co);

input [3:0] a;

input[3:0]b;

input ci;

output[3:0] sum;

output[3:0] co;

wire[3:0] count;

add u0(a[0],b[0],ci,sum[0],count[0]);

add u1(a[1],b[1],count[0],sum[1],count[1]);

add u2(a[2],b[2],count[1],sum[2],count[2]);

add u3(a[3],b[3],count[2],sum[3],count[3]);

assign co = count[3];

end module

(3)测试文件module f_adder();

Testbench模块最重要的的任务就是利用各种合法的语句,产生适当的时序和数据,以完成测试,并达到覆盖率要求。测试文件源代码如下:

-

`timescale 1ns / 1ps module adder(a,b,ci,sum,co); input [3:0] a; input[3:0]b; input ci; output[3:0] sum; output[3:0] co; wire[3:0] count; add u0(a[0],b[0],ci,sum[0],count[0]); add u1(a[1],b[1],count[0],sum[1],count[1]); add u2(a[2],b[2],count[1],sum[2],count[2]); add u3(a[3],b[3],count[2],sum[3],count[3]); assign co = count[3]; end module

四、实验结果及分析

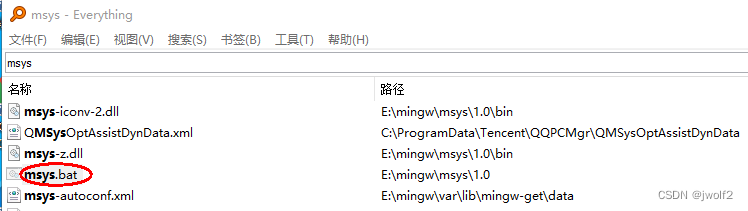

1、引脚锁定

以约束文件形式

set_property PACKAGE_PIN V17 [get_ports {a[0]}]

set_property PACKAGE_PIN V16 [get_ports {a[1]}]

set_property PACKAGE_PIN W16 [get_ports {a[2]}]

set_property PACKAGE_PIN W17 [get_ports {a[3]}]

set_property PACKAGE_PIN W15 [get_ports {b[0]}]

set_property PACKAGE_PIN V15 [get_ports {b[1]}]

set_property PACKAGE_PIN W14 [get_ports {b[2]}]

set_property PACKAGE_PIN W13 [get_ports {b[3]}]

set_property PACKAGE_PIN V2 [get_ports ci]

set_property PACKAGE_PIN U16 [get_ports {sum[0]}]

set_property PACKAGE_PIN E19 [get_ports {sum[1]}]

set_property PACKAGE_PIN U19 [get_ports {sum[2]}]

set_property PACKAGE_PIN V19 [get_ports {sum[3]}]

set_property PACKAGE_PIN W18 [get_ports co]

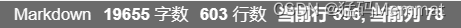

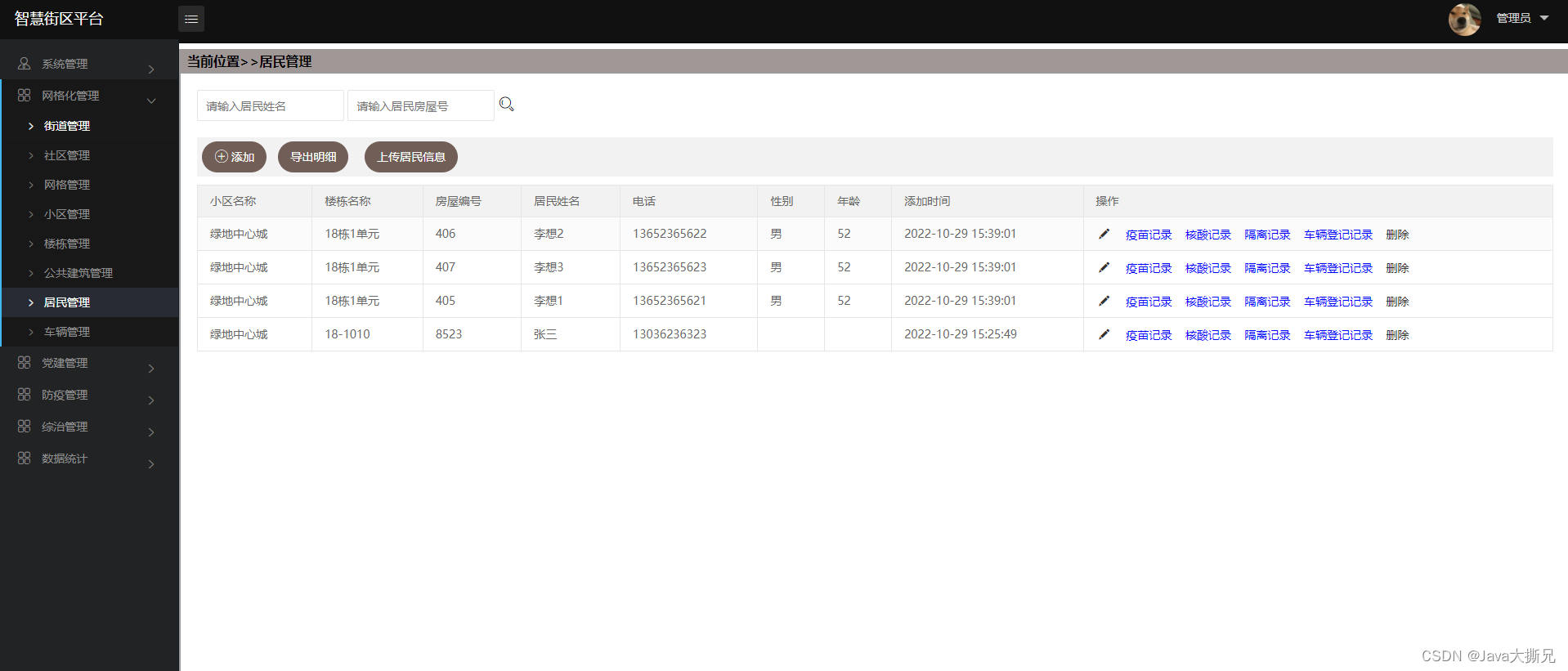

2.仿真波形及分析

(1)仿真波形如下

(3)如上图,第一行是加数a,第二行是加数b,两者均以十进制形式显示。两者之和加上低位的进位输入ci作为总输入数据。由于所设计的是四位加法器,结果超过15的部分才会向高位进位。

sum表示和,co表示向高位进位

以波形图数据为例进行分析:

a=7,b=7,ci=1,此时sum=15,co=0

a=9,b=9,ci=1,此时sum=3,co=1,向高位进了一位。

故此波形图很好的证明了加法器设计的正确性。

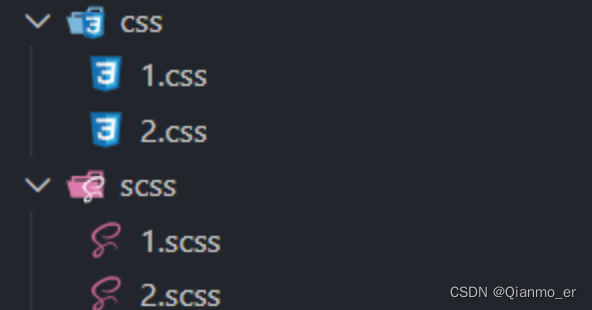

3、下载测试结果及分析

(1)测试用例1:1000+0111=1111

开发板情况如下所示:

进位co未亮灯,表示sum的V19-U6均亮灯,即和为15,未产生进位

(2)测试用例2:1001+1010+1=10011(高位的1为进位),即9+10+1=20

开发板情况如下:

进位co亮灯,表示sum的亮灯情况为0011,即和为3,产生一个进位

综合以上两种情况知:该设计实现了四位全加器的功能!

五、实验心得

本实验无论是设计原理还是功能仿真相对来说均难度不大,回过头看,实验各流程的设计内容都是很好实现的。完成这个实验最大的难点首先是在于初学时对软件的不熟悉,有时候明明知道自己下一步该做什么,却不知道应该点哪里,选择什么选项,经过在哔哩哔哩等平台的学习后才知道一个完整的fgpa工程要经过综合、仿真、烧写等过程;另一点是因为刚开始接触Verilog语言,对于其使用并不是很熟悉。

最开始实现一位全加器时的代码是自己根据自己的一些理解码出来的,后面参考了老师在学习通上面所给的示例进行改进,与自己先前所写代码相比简化了许多,虽然都能实现一位全加器的基本功能,但看上去更简短更清晰。

仿真后进行上板测试的过程卡了我一段时间,因为不清楚到底如何操作,但参考有关资料后,学习了约束文件的写法和如何进行引脚分配,使实物测试的过程比较顺利的通过。同时我认为上板子进行测试的这一过程可以更好的让我们通过实践更深层次的理解全加器的原理。

可以说实验一的完成,代表了我们正式入门了 VIVADO这个软件,也了解和能够运用它的基本操作来实现一些功能;在代码编写方面,通过此次实验,我对层次法设理解有了更深的理解,这为我们接下来实验的进行打下了很好的基础。