【VHDL】【作业】3 GENERIC语句 和 INTEGER类型

文章目录

- 【VHDL】【作业】3 GENERIC语句 和 INTEGER类型

- 前言

- 什么是GENERIC语句?

- 32位加法器

- 仿真波形

- 总结

- 每天进步一点点 笔记仅供自学,用来回看复习,不一定适合你,如有错误请指出。

前言

记录学习的过程,顺便期末复习一下。

什么是GENERIC语句?

类属语句(GENERIC),其实就是一种ENTITY中的命名技巧,可以提高代码的复用率。

格式是 GENERIC(常数名数据类型 := 设定值);:=和变量赋值的符号一样

32位加法器

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

USE IEEE.STD_LOGIC_UNSIGNED.ALL ; --此程序包中包含算术操作符的重载函数

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY adder32b IS

GENERIC ( S : INTEGER := 8); --定义参数 S 为整数类型,且此时等于 8

PORT (A,B : IN STD_LOGIC_VECTOR(4*S-1 DOWNTO 0) ;--总共有32位 [0,31]

CIN : IN STD_LOGIC ;

COUT : OUT STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR(4*S-1 DOWNTO 0));--总共有32位 [0,31]

END ENTITY adder32b;

ARCHITECTURE BHV OF adder32b IS

SIGNAL DATA : STD_LOGIC_VECTOR(4*S DOWNTO 0);--总共有33位 [0,32]

BEGIN

DATA <= ('0' & A) + ('0' & B) + ("00000000000000000000000000000000" & CIN);--并置一下

--使得它们的位都相等,方便相加

COUT <= DATA(32); --[32]位 是1时,代表有进位 就是输出进位

DOUT <= DATA(4*S-1 DOWNTO 0);--总共有32位 [0,31] --输出计算结果

END ARCHITECTURE BHV;

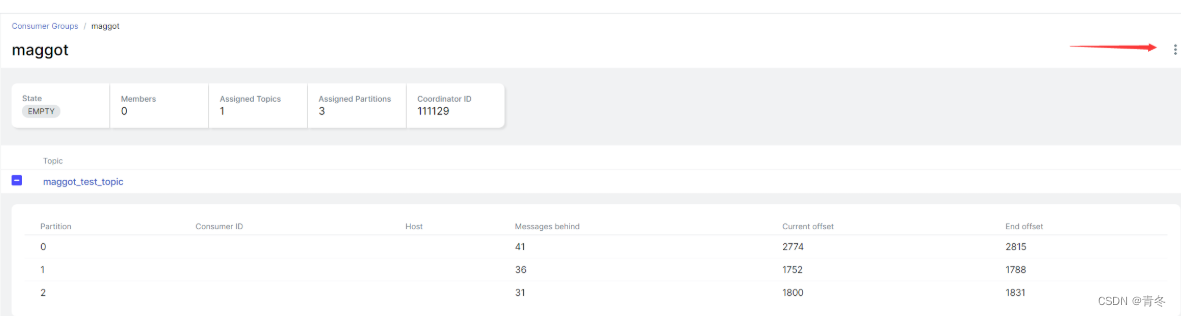

仿真波形

有进位 结果要加1

总结

这次作业 主要是为了理解一下 GENERIC语句 和 INTEGER类型 的搭配使用。

修改起来很方便,提高了代码的复用率。

![[选型] 实时数仓之技术选型](https://img-blog.csdnimg.cn/img_convert/41ccfc03b487d599a67a2b148245156b.png)