LVDS硬件接口电路设计

- 1 简介

- 2 硬件设计实战

- 3 硬件设计要点

- 4 Layout注意事项

- 5 MIPI与LVDS的区别

1 简介

LVDS(Low-Voltage Differential Singnaling,低电压差分信号)可以实现点对点或者一点对多点的连接,具有低功耗、低误码率、低串扰、低辐射等特点。LVDS时一种小振幅差分信号技术,使用非常低的振幅(约350mV)通过一对PCB差分信号或者平衡传输线缆传输数据。它允许单个信道传输速率达到每秒数百兆比特,其特有的低振幅及恒流源模式驱动只产生极低的噪声,功率极小。、LVDS物理接口使用1.2V偏置提供400mV振幅的信号(差分信号的优点时噪声以共模的方式在一对差分线上耦合出现,并在接收器中相减从而消除噪声)。LVDS 驱动和接收器不依赖于特定的供电电压,因此它很容易迁移到低压供电的系统中去,而性能不变。

建议最大的传输速率为655Mb/s,无失真媒质上理论极限传输速率为1.823Gb/s.

LVDS的组成:

LVDS一般由三部分组成:差分信号发送器、差分信号互联器,差分信号接收器。

| 名称 | 功能描述 |

|---|---|

| 差分信号发送器 | 将非平衡传输的TTL信号转换成平衡传输的LVDS信号。 |

| 差分信号接收器 | 将平衡传输的LVDS信号转换成非平衡传输的TTL信号。 |

| 差分信号互联器 | 包括连接线(电缆或者PCB走线)、终端匹配电阻(一般为100Ω)。 |

工作原理:

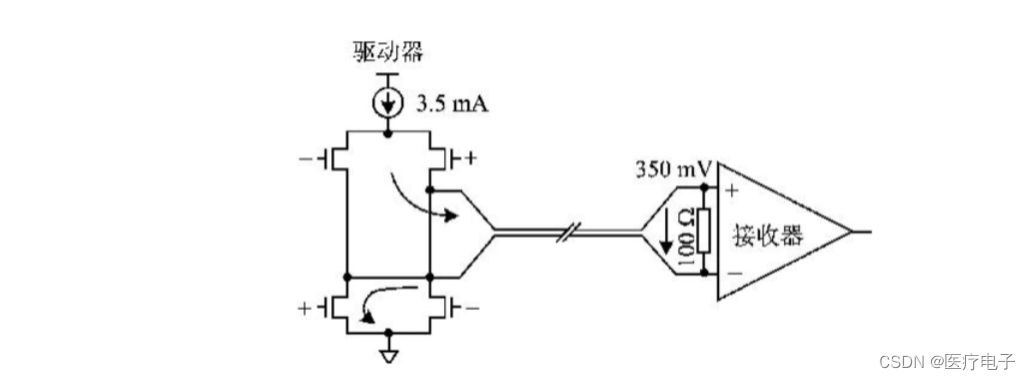

- LVDS 驱动器由一个驱动差分线对的电流源组成,通常为 3.5mA。

- LVDS 接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过 100Ω的匹配电阻,并在接收器的输入端产生大约 350mV 的电压。当驱动器翻转时,它改变流经电阻的电流方向,产生有效的逻辑"1"和逻辑"0"状态。

- 驱动器只有一个恒流源,这个差分驱动器采用奇模(Odd - mode)的传输方式,即等量的方向相反的电流分别在传输线路上传送。电流会重新回流到双绞线内,加上电流环路面积较小,因此产生最少电磁干扰。

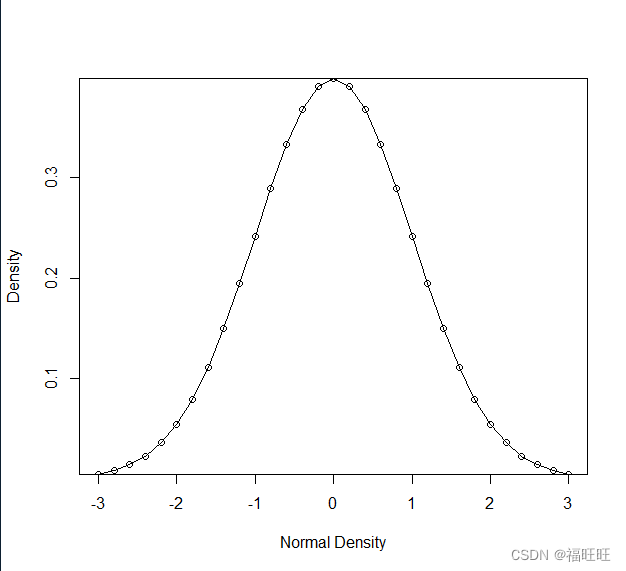

LVDS电平特性:

| DC特性 | 条件 | MIN | TYPE | MAX | UNITS |

|---|---|---|---|---|---|

| Output High Voltage for the Q or Q’ | RT=100Ω across Q and Q’ signals | - | 1.38 | 1.6 | V |

| Output Low Voltage for the Q or Q’ | RT=100Ω across Q and Q’ signals | 0.9 | 1.03 | - | V |

| Differential Output Voltage(Q-Q’) Q=High((Q-Q’),Q’=High | RT=100Ω across Q and Q’ signals | 250 | 350 | 450 | mV |

| Output Common-Mode Voltage (Q+Q’)/2 | RT=100Ω across Q and Q’ signals | 1.125 | 1.250 | 1.375 | V |

| Differential Input Voltage(Q-Q’) Q=High((Q-Q’),Q’=High | Common-mode Input Voltage=1.25V | 100 | 350 | - | mV |

| Input Common-Mode Voltage (Q+Q’)/2 | Differential Input Voltage=350mV | 0.25 | 1.25 | 2.25 | V |

LVDS 物理接口使用 1.2V 偏置电压作为基准(共模直流电压),提供大约350mV 摆幅(差模电压)。

LVDS 驱动器由一个驱动差分线对的电流源组成(通常电流为 3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过 100Ω的匹配电阻,并在接收器的输入端产生大约 350mV 的电压。电流源为恒流特性,终端电阻在 100-120 欧姆之间,则电压摆动幅度为:3.5mA100=350mV;3.5mA120=420mV。

LVDS的特点:

-

低至 2V 的电源电压兼容性

-

低噪声

-

高噪声抑制能力

-

可靠的信号传输

-

能够集成到系统级 IC 内

-

使用 LVDS 技术的的产品数据速率可以从几百 Mbps 到 2Gbps

-

它是电流驱动的,通过在接收端放置一个负载而得到电压,当电流正向流动,接收端输出为 1,反之为 0

-

它的摆幅为 250mv-450mv

-

此技术基于 ANSI/TIA/EIA-644LVDS 接口标准

2 硬件设计实战

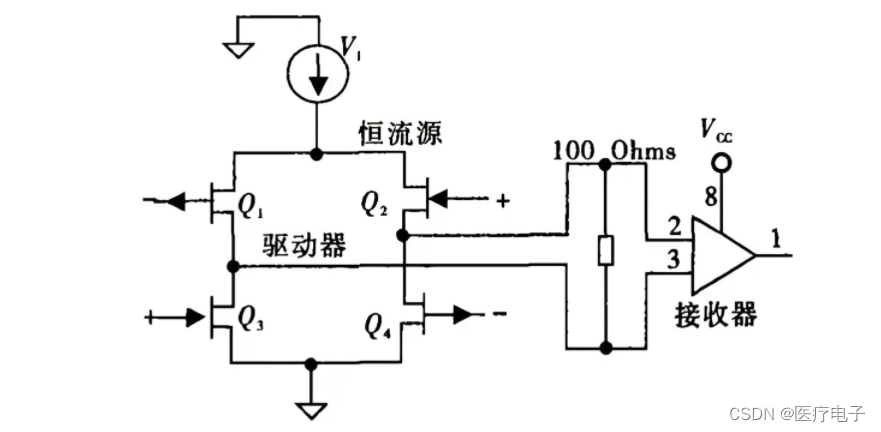

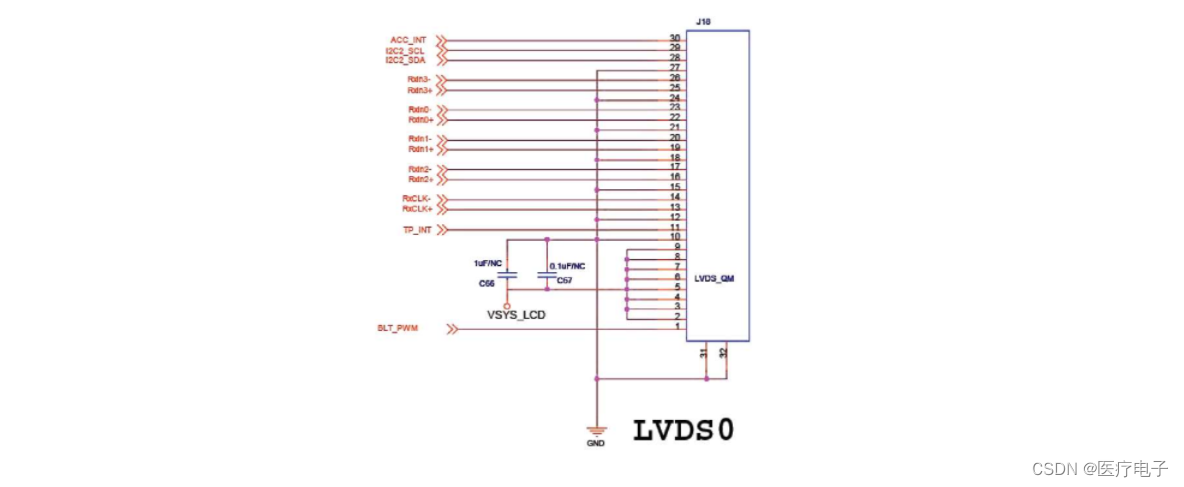

实战电路1:

实战电路2:

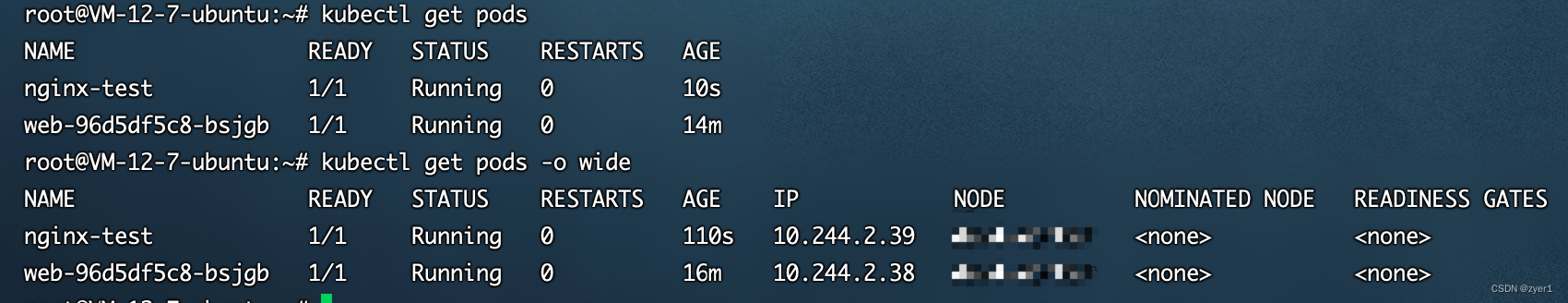

3 硬件设计要点

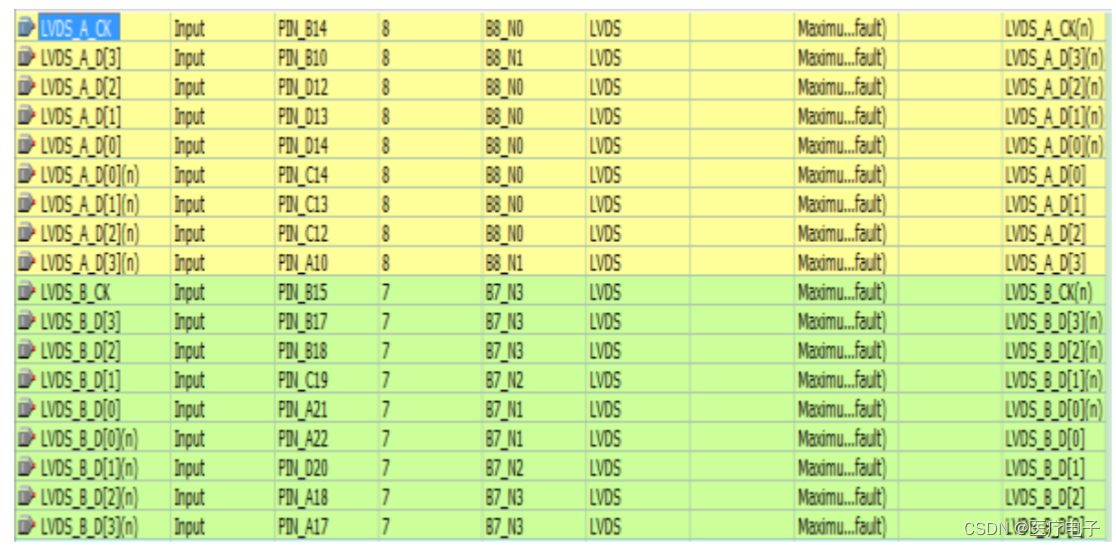

- altera FPGA

- 对于作为 LVDS 传输的 BANK 必须接 2.5V 的 VCCIO

- 左右 BANK(即 1/2/5/6 BANK)的 LVDS 发送差分对信号无需外接匹配电阻,而上下 BANK(即 3/4/7/8 BANK)则需要,如果硬件工程师忘了,还可以在 FPGA 的 IO 引脚分配时里加端接电阻设置;

- 分配管脚时,左右 BANK 的 LVDS 差分信号脚在 IO 分配时选择的 IO 电平标准是 LVDS,而上下 BANK 的 LVDS 差分信号脚在 IO 分配时选择的 IO 电平标准是 LVDS_E_3R;

- 分配管脚时,只要指定 LVDS 信号的 p 端(+),则 n 端(-)会自动分配。在 verilog 代码中只要一个信号接口即可,无需在代码中定义一个差分对接口;

- 速度高时需用 IP 核(200MHz 或 400Mbps 以上,串并转换器),在 altera FPGA 内使用的 LVDS 收发 IP 核是 altlvds_rx 和 altlvds_tx,相应的 IP 使用说明在 megawizard 里有。

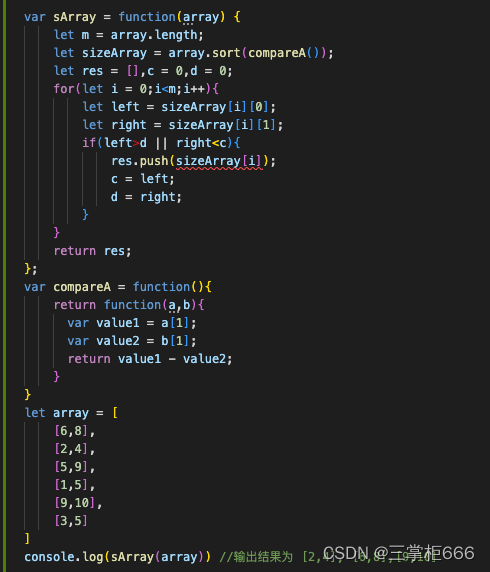

- xilinx FPGA

区别 altera 的地方在于首先在 Verilog 的代码里,xilinx 的 LVDS 信号需要定义一对差分对信号,通过 xilinx 的原语进行差分对转单端或者单端转成差分对信号。另外在 IO 引脚分配时,xilinx 的电平标准都是一样的,比如都是 LVDS_33。下图 1 是 altera 下的 LVDS 信号引脚分配,可见用户只需要分配 p 端(+)引脚即可。

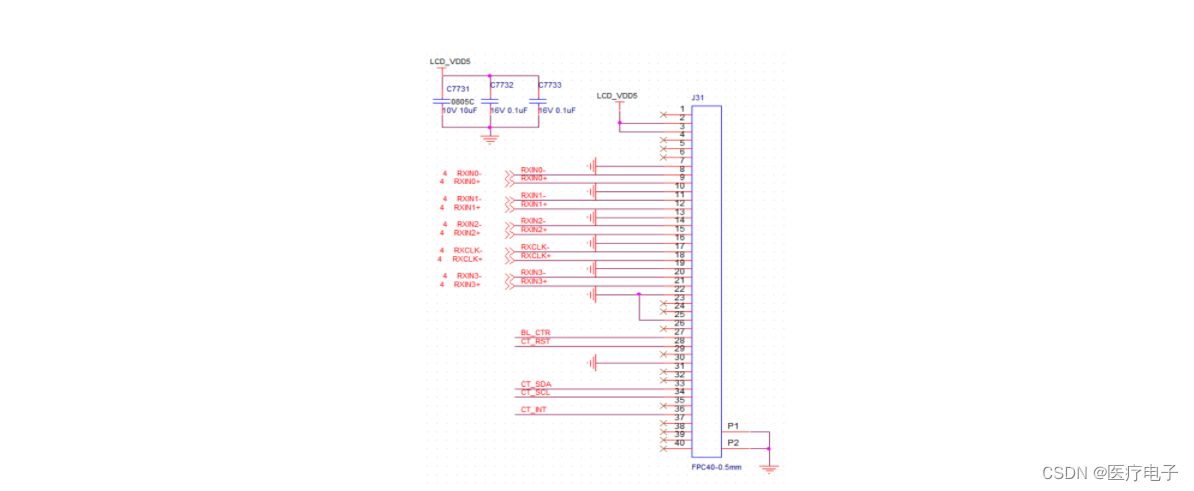

4 Layout注意事项

-

由于差分线较多并为了方便做阻抗匹配,PCB 至少采用四层板设计;

-

电源滤波电容尽可能的靠近芯片电源 pin;

-

每组电源都需要通过磁珠进行隔离,且都要增加电源滤波电容;

-

PCB 板尽可能铺设大面积的 GND ;

-

LVDS 输出差分信号走线设计成 100Ω 差分匹配,走线尽可能保持等长;

-

LVDS 输出差分信号正负通道间隔 S1 尽可能的小;

-

LVDS 各输出差分信号通道间的间隔至少要大于 2 倍 S1;

-

100Ω 终端电阻要尽可能的靠近 LVDS 接收器输入端口;

-

LVDS 输出差分信号通路尽可能的少用通孔,且走线避免设计成 90°弯角。

5 MIPI与LVDS的区别

-

LVDS 接口只用于传输视频数据,MIPI 不仅能够传输视频数据,还能传输控制指令;

-

LVDS 接口主要是将 RGB TTL 信号按照 SPWG/JEIDA 格式转换成 LVDS 信号进行传输,MIPI 接口则按照特定的握手顺序和指令规则传输屏幕控制所需的视频数据和控制数据。

![[附源码]计算机毕业设计酒店客房管理信息系统Springboot程序](https://img-blog.csdnimg.cn/cb452dccce504d7fa28fabb5430afc13.png)